- •Содержание

- •1. Теоретическая часть 17

- •1. Теоретическая часть 37

- •Лабораторная работа № 1 системы счисления. Построение алгоритмов решения задач

- •1. Теоретическая часть

- •1.1. Основные сведения

- •1.1.2. Перевод чисел из одной формы в другую.

- •1.1.3. Формы представления чисел.

- •1.1.4. Операции над числами.

- •1.1.5. Алгоритмы.

- •2. Порядок выполнения работы

- •3. Содержание отчета

- •Контрольные вопросы

- •5. Литература

- •Лабораторная работа № 2 изучение однокристальных 8-ми разрядных микропроцессоров на примере микропроцессора кр580

- •1. Теоретическая часть

- •1.1. Общие сведения о мп к580.

- •1.2. Структура мп к580.

- •1.3. Система и формат команд мп к580.

- •1.4. Учебный микропроцессорный комплект к580.

- •2. Подготовка к выполнению работы

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •6. Литература

- •Лабораторная работа № 3 изучение однокристальных микропроцессоров на примере микропроцессора кр1810

- •1. Теоретическая часть

- •1.1. Общие сведения о мп кр1810.

- •1.2. Структура мп кр1810

- •1.3. Способы адресации

- •1.4. Система и формат команд мп к1810

- •2. Подготовка к выполнению работы

- •3. Порядок выполнения работы

- •Программа

- •4. Содержание отчета

- •5. Контрольные вопросы

- •6. Литература

- •Лабораторная работа № 4 изучение секционных микропроцессоров на примере микропроцессорного комплекта км1804

- •1. Краткие теоретические сведения

- •1.1. Микропроцессорная секция параллельной обработки информации

- •1.2. Операции, выполняемые в мпс.

- •1.3. Схемы управления адресом микрокоманды кр1804ву1, кр1804ву2

- •1.4. Схема управления следующим адресом кр1804вуз.

- •1.5. Формат микрокоманды

- •1.6. Микротренажер для изучения мпк км1804

- •2. Подготовка к выполнению работы

- •3. Порядок выполнения работы

- •4. Содержание отчета

- •5. Контрольные вопросы

- •6. Литература

4. Содержание отчета

4.1. Подробный алгоритм и программа на языке АССЕМБЛЕР по нахождению значения функции.

4.2. Результат выполнения программы по нахождению значения функции.

4.3. Подробный алгоритм и программа на языке АССЕМБЛЕР по организации условий при работе с массивами чисел.

4.4. Результат выполнения программы по организации условий при работе с массивами чисел.

5. Контрольные вопросы

5.1. Какие шины рассматривают в структуре МП К1810, и каковы их назначение и разрядность.

5.2. Назначение устройства сопряжения с шиной МП К1810. Его состав и назначение.

5.3. Назначение операционного устройства МП К1810. Его состав и назначение.

5.4. Назначение и состав блока регистров общего назначения МП К1810.

5.5. Регистр признаков. Размерность и состав.

5.6. Устройство управления МП К1810. Сигналы связи с внешними устройствами.

5.7. Способы адресации МП К1810.

5.8. Формат команд МП К1810.

5.9. Система команд МП К1810.

6. Литература

6.1. Каган Б.М., Сташин В.В. Основы проектирования микропроцессорных устройств автоматики. – М.: Энергоиздат, 1987. – 303с.

6.2. Калабеков Б.А. Микропроцессоры и их применение в системах передачи и обработки сигналов: Учебное пособие для высших учебных заведений. М.: Радио и связь, 1988. – 368с.

6.3. Балашов Е.П., Григорьев В.Л., Петров Г.А. Микро- и мини-ЭВМ/Для студентов ВУЗов. – Л.: Энергоатомиздат, 1984. – 376с.

6.4. Микропроцессоры: Том1./ под ред. Преснухина Л.Н. – Мн.: Вышэйшая школа, 1987. – 416с.

Лабораторная работа № 4 изучение секционных микропроцессоров на примере микропроцессорного комплекта км1804

Цель работы:

Изучение микропроцессорного комплекта КМ1804. Приобретение навыков программирования секционных микропроцессоров.

1. Краткие теоретические сведения

Микропроцессорный комплект серии КМ1804 выполнен на основе биполярной технологии ТТЛШ и предназначен для построения быстродействующих вычислительных устройств, контроллеров различного назначения, микроЭВМ с различными системами команд, измерительных систем.

В табл. 4.1 приведен функциональный состав микропроцессорного комплекта (МПК) серии КМ1804.

Таблица 4.1

Функциональный состав МПК серии КМ1804

Тип микросхемы |

Назначение микросхемы |

1 |

2 |

КМ1804 ВС1 |

Микропроцессорная секция параллельной обработки информации |

КМ1804 ВР1 |

Схема ускоренного переноса |

КМ1804 ВИ1 |

Параллельный регистр |

КМ1804 ВУ1 |

Схема управления адресом микрокоманды |

КМ1804 ВУ3 |

Схема управления следующим адресом |

1.1. Микропроцессорная секция параллельной обработки информации

Микросхема КМ1804ВС1 (аналог АМ2901) представляет собой четырехразрядную микропроцессорную секцию, предназначенную для построения блоков обработки цифровой информации с разрядностью, кратной 4.

Микросхема имеет:

двухадресную архитектуру внутреннего регистрового запоминающего устройства с организацией 16 х 4 бит;

восемь функций арифметико-логического устройства (АЛУ) – сложение, два вычитания с формированием сигналов переноса и состояния и пять логических функций (И, ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ, ИСКЛЮЧАЮЩЕЕ ИЛИ-НЕ);

большой выбор пар источников операндов АЛУ;

сдвиги влево/вправо независимо от АЛУ;

четыре флага состояния (перенос, переполнение, нуль, знак).

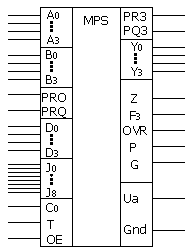

б)

а)

Рисунок 4.1.

а) Внешний вид корпуса микросхемы КМ1804ВС1;

б) Структура секционного МП КМ1804ВС1.

Структурная схема КМ1804ВС1 представлена на рис. 4.1.

Микропроцессорная секция условно делится на четыре независимых блока:

1. Блок внутренней памяти;

2. Блок рабочего регистра;

3. Арифметико-логический блок;

4. Блок управления.

1. Блок внутренней памяти (БВП) – предназначен для кратковременного хранения данных, необходимых для выполнения программы. Кроме этого блок организует выборку операндов, необходимых для выполнения текущей операции. Блок содержит следующее:

РЗУ – регистровое запоминающее устройство

СДА – сдвигатель данных АЛУ

Рг А – регистр А

Рг В – регистр В

А3-0 – параллельный вход канала А

В3-0 – параллельный вход канала В

PR0 – двунаправленный вывод младшего разряда РЗУ

PR3 – двунаправленный вывод старшего разряда РЗУ

РЗУ, содержит 16 4–ех разрядных регистра. Адреса регистров представляются четырехразрядной кодовой комбинацией, РЗУ имеет два адресных входа А3-0, В3-0, на которые информация поступает из микрокоманды.

Задавая в полях микрокоманды адреса по А и В можно одновременно производить чтение любой пары регистров. Выданное на выходы А и В содержимое регистров РЗУ принимается соответственно в регистры Рг А и Рг В, которые служат источником операндов.

Запись в РЗУ в каждый такт может производиться лишь в один из регистров, адрес которого задается шиной Д. Записанные данные поступают на его вход с выхода АЛУ через узел сдвигателя данных. Данные через этот узел могут передаваться без сдвига или со сдвигом на один разряд вправо или влево.

Выводы PR0 и PR3 служат входом или выходом, через которые производится запись значений в освободившийся при сдвиге разряд и выдача содержимого выдвигаемого регистра.

2. Блок рабочего регистра (БР) – дополнительный блок, позволяющий выполнять параллельно основной операции операций сдвига. Может являться источником операнда при выполнении операций. Блок содержит:

СР – сдвигатель регистра

PQ3 – двунаправленный вывод старшего разряда регистра Q

PQ0 - двунаправленный вывод младшего разряда регистра Q

Блок рабочего регистра Q содержит одиночные четырехразрядные регистры, построенные на Д – триггерах. Содержимое этого регистра постоянно передается в узел АЛУ. Данные на вход регистра передаются через узел СР, передавая записанные в регистр данные без сдвига или со сдвигом на один разряд вправо или влево.

3. Арифметико-логический блок (БАЛ) – предназначен для выполнения операций. В своем составе содержит:

СИД – селектор источника данных;

АЛУ – арифметика–логическое устройство;

СВД – селектор выходных данных;

Y3-0 – параллельный выход данных;

ОЕ – разрешение вывода;

R и S – каналы данных и сброса;

АЛУ имеет два четырехразрядных входа R и S,на которые данные поступают с СИДа, который позволяет коммутировать следующие направления:

На вход R СИД может коммутировать: выход регистра А, внешнюю шину данных D. Кроме этого он может подавать 0.

На вход S СИД может подключать выход регистра А, выход регистра В, выход регистра Q, а также 0.

Селектор выходных данных представляет собой двухвходовой коммутатор, который в зависимости от состояния сигналов на входах I8…I6, выдает на шину Y функцию АЛУ (F) или выход канала А РЗУ (А).

АЛУ имеет выход признаков:

Z – признак нулевого результата

F3 – старший разряд результата АЛУ, признак отрицательного результата – “1”

OVR – переполнение АЛУ. Формируется следующим образом:

OVR= C3 + C4

C4 – последовательный перенос АЛУ (“1” – перенос из старшего разряда)

C3 – перенос, передаваемый в старший разряд

Если числа представляются со знаковым разрядом, то при OVR=1 искажается знаковый разряд и результат оказывается ошибочным.

P и G предназначены для подключения микросхем микропроцессорных секций по схемам с ускоренным переносом.

4. Блок управления (БУ) – организует работу микропроцессорной секции.

I0-8 – входы управления сигналов

Блок управления преобразует содержимого входа операций I0-8 микрокоманды в систему управляющих сигналов, под действием которых в узлах МПС выполняются микрооперации.

Микрокоманда выглядит следующим образом:

-

ОЕ… C0

I0… I8

A3… A0

B3… B0

Таким образом, тип выполняемой АЛУ микрокоманды задается кодом, подаваемым на входы I0…I8, причем разряды I0…I2 определяют источник входной информации АЛУ, разряды I3…I5 - выполняемую функцию, а разряды I6…I8 – приемник результата.