- •Лекции 13 -17

- •Особенности и основные характеристики плис семейств Spartan–3a и Spartan–3an

- •Программируемые логические генераторы

- •Блочная память

- •Аппаратные умножители — блоки dsp48e

- •Трассировочные ресурсы

- •1.1.7Трассировочные ресурсы

- •Состав семейства

- •Производительность

- •Fpga платформы плис Virtex-5 txt фирмы Xilin Общая характеристика

- •Назначение и применение

- •Переход к одночиповой реализации системы с суммарной пропускной способностью 100 Гбит/с

- •Программная поддержка

- •Семейство плис Virtex-5 fxt с встроенным процессорным ядром PowerPc 440 Характеристики плис платформы Virtex-5 ftx

- •Лекция 16 Stratix III – новое семейство fpga фирмы Altera

- •Архитектура fpga Stratix III

- •Адаптивные логические модули (alm)

- •Структура памяти TriMatrix

- •Блоки цифровой обработки сигналов

- •Банки ввода-вывода

- •Средства защиты проекта

- •Средства поддержки разработок

- •Архитектура плис со структурой cpld

- •Леция 17 40-нм fpga компании Altera Stratix IV

- •Процессоры dsp

- •Базовая логическая ячейка.

- •Пример пректирования цифровых устройств на основе плис

Лекции 13 -17

Лекция 1 3. Архитектура ПЛИС серии Spartan : Spartan-3, Spartan-3a Spartan–3AN.

Архитектура и основные особенности ПЛИС Spartan-3

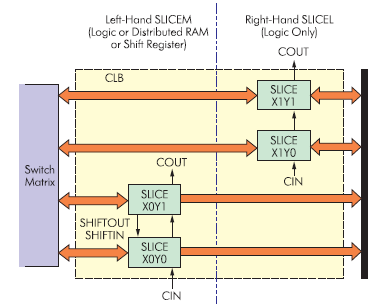

2002–2003 годы ознаменовались появлением очередного семейства Spartan-3,. Это семейство полностью отвечает ожиданиям от данной серии — еще дешевле и еще больше производи тельности в типичных задачах. В настоящее время розничные цены на младшие устройст ва Spartan-3 находятся в районе $10, что прак тически вплотную приближает ПЛИС к мик роконтроллерам с сопоставимыми функцио нальными возможностями. Самое важное, в составе этого семейства наконец-то появи лись выделенные умножители, а также изме нена организация блочной памяти с 4096 бит на 1КW18. Иными словами, архитектура Spartan-3 в целом основана на ПЛИС Virtex-II. Каждый КЛБ семейства Spartan-3 состоит из четырех секций, сгруппированных в пары (рис. 2). Левая пара называется SLICEM и содер жит привычные разработчикам, знакомым с предыдущими семействами ПЛИС Xilinx, пол нофункциональные логические генераторы, ко торые могут использоваться также в качестве распределенного ОЗУ или сдвигового регистра. Однако расположенная на рисунке справа пара SLICEL может реализовать только логику.

Рис. 1. Организация секций КЛБ в ПЛИС Spartan-3

Схемы секций семейств Spartan-3, представлены соответственно на рис. 2 . Для Spartan-3 показаны верхние секции и часть общей логики. Назначение этих рисунков — продемонстрировать общую схожесть архитектур последних семейств ПЛИС. Тем не менее, можно отметить некоторые моменты, свидетельствующие об «облегчении» устройств Spartan. В основном это касается чуть меньшей сложности внутренних трассировочных ресурсов и меньшего количества дополнительных выходов секции.

Рис. 2. Схема секции ПЛИС Spartan-3

Интересным является также анализ организации внутренних мультиплексоров в логических ячейках. Как уже упоминалось, они служат для объединения нескольких входных линий. В действительности такие устройства необходимы для нормального функционирования логических ячеек, поскольку в проекте может потребоваться использование выходного сигнала логической ячейки как непосредственно после LUT, так и после триггера той же ячейки. Поэтому часть мультиплексоров, входящих в логические ячейки, может быть использована для формирования более сложных узлов комбинаторной логики. Такие программируемые мультиплексоры обозначаются как Fx, где x — номер в порядке возрастания иерархии в общей структуре программируемых ресурсов.

Еще одним нововведением (впервые для устройств Xilinx) является возможность загруз ки конфигурации непосредственно с NOR-Flash с 8- или 16-разрядной шиной данных. Такой режим освобождает от необходимости исполь зовать только специальные конфигурацион ные ПЗУ производства Xilinx, заменив их прак тически любой подходящей по объему микро схемой Flash-памяти.

Технические характеристики ПЛИС Spartan-3 и Spartan-3E приведены в таблице.

Таблица

Рис .3

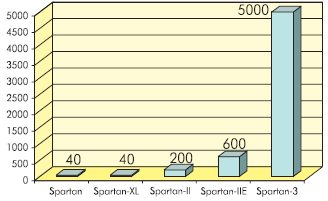

Динамика изменения максимального логи ческого объема и напряжения питания ПЛИС Spartan приведена на рис. 4 и 5.

Рис. 4. Максимальный логический объем ПЛИС серии Spartan

Рис.5

Еще более странно рассматривать такой проект на фоне присутствия в Spartan-3 блочной памяти еще большего объема (до 1,8 Мбит на кристалле в старших моделях!). Можно предположить, что большая часть логических ячеек, скорее всего, будет реализовывать имен но логические функции, а уменьшение макси мального объема доступной распределенной памяти прекрасно компенсируется увеличени ем количества блочной (гораздо более эффек тивной и удобной в использовании). Наконец, следует все-таки отметить, что распределенная память в секциях SLICEM так и осталась рас пределенной по всему кристаллу. В итоге пол нофункциональные SLICEM и облегченные SLICEL вполне могут дополнять друг друга.

Что касается внутренних буферов с тремя состояниями, то можно заметить, что выиг рыш от их использования появляется в тех случаях, когда в проекте требуется мульти плексирование шин с большой разрядностью, причем число входных шин мультиплексоров также оказывается достаточно большим. В этих случаях использование буферов с тре тьим состоянием оказывается выгоднее, чем ка скадное наращивание логических ячеек (огра ниченных по числу входов мультиплексора). Однако очевидно, что если возможности ло гических ячеек по реализации многовходовых мультиплексоров будут улучшены, то и по требность во внутренних буферах с тремя со стояниями существенно уменьшится. Имен но такой путь и был реализован в семействе Spartan-3, причем удаление буферов привело одновременно и к уменьшению задержек, и к удешевлению микросхем.