- •1. Мета роботи

- •2. Короткі теоретичні відомості

- •2.1. Призначення та режими роботи iнтерфейса

- •2.2. Структура мiкросхеми кр580вв55

- •2.3. Робота iнтерфейса кр580вв55.

- •3.2. Робота мiкросхеми в режимі 0.

- •0000 0110 – 06 (Вмiст акумулятора пiсля операцiї)

- •3. Опислабораторної установки

- •4. Завдання

- •4.1.Виконується на самостiйнiй пiдготовцi перед виконанням роботи.

- •4.2. Виконується в лабораторiї.

- •5. Опрацювання дослідних даних

- •6. Контрольні запитання

- •7. Література

ЛАБОРАТОРНА РОБОТА №5

Дослідження роботи ППІ КР580ВВ55

___________________________________________________________________________

1. Мета роботи

Вивчення структури та принципу роботи програмованого паралельного iнтерфейса КР580ВВ55.

2. Короткі теоретичні відомості

2.1. Призначення та режими роботи iнтерфейса

Мiкросхема КП580ВВ55 використовується для узгодження системної шини мiкро–ЕОМ з периферiйними пристроями для прийому та зберiгання iнформацiї, що пересилається мiж мiкропроцесором (МП) та зовнiшнiми пристроями. ВІС КР580ВВ55 виконана на nМОП – технології, живиться від джерела +5В і споживає струм 120 мА. Мікросхема являє собою програмований паралельний інтерфейс на 24 ліній вводу/виводу з навантажувальною здатністю 2,5 мА. Мікросхема містить два 8-розрядних і два 4-розрядних порти вводу/виводу.

Режим роботи iнтерфейса.

Мiкросхема використовується в трьох режимах роботи:

режим 0, в якому кожна з двох груп виводiв мiкросхеми ( А та В ), по 12 виводiв в кожнiй, можуть бути запрограмованi на ввiд або на вивiд;

режим 1, в якому по 8 виводiв кожної групи можуть бути запрограмованi на стробований ввiд або вивiд, а iншi 4 виводи використовуються для керування програмним обмiном або обмiном по перериванню;

режим 2, в якому мiкросхема є двонаправленим 8–розрядним каналом даних, що керується сигналами 5–и виводiв.

В данiй дослiднiй роботi мiкросхема працює в режимi 0.

2.2. Структура мiкросхеми кр580вв55

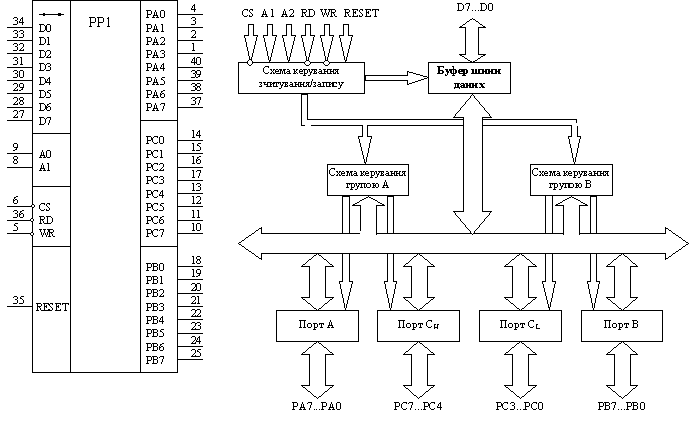

Мiкросхема, умовне позначення якої показане на мал.1, мiстить (мал.2):

порти вводу–виводу А, В, С;

схеми керування групами шин А та В;

буфер шини даних для узгодження з двонаправленою шиною даних МП;

схему керування зчитуванням/записом.

Через порти А (РА7...РА0), В (РВ7...РВ0), С (РС7...РС0) пiд’єднуються зовнiшнi пристрої.

Порт А мiстить два регiстри:

8–розрядний вхiдний iз вхiдними формувачами;

8–розрядний вихiдний iз вихiдними формувачами;

Порт А може працювати на ввід або вивід 8–розрядних слiв у всiх трьох режимах.

Порт В має аналогiчну порту А будову. Працює на ввід або вивід у двох режимах–0 та 1.

Порт С мiстить два чотирирозрядних регiстри:

–регiстр розрядiв С(L) = РС3...РС0;

–регiстр розрядiв С(H) = РС7...РС4, кожному з яких вiдповiдають вхiднi та вихiднi формувачi.

Використовуються для вводу–виводу 4–розрядних слiв в режимі 0. В режимах 1 та 2 можуть використовуватись для прийому та передачi керуючих сигналiв обмiну для портiв А та В, а регiстри порта С виконують функцiю регістра стану.

Схема керування групами шин А та В. Кожна iз схем мiстить Регіст Керуючого Слова (РКС), що використовується для при йому та зберiгання керуючого слова, яке поступає через Буфер Шини Даних (БШД). Запис цього слова в регiстр здiйснюється при наявностi одиницi в розрядi D7 керуючого слова. БШД–тристабiльний двонаправлений буфер.

Схемою керування групою А задається режим роботи портiв А та С(H), групою В режим роботи портiв В та С(L).

Схема керування зчитуванням/записом здiйснює керування мiкросхемою пiд дiєю зовнiшнiх сигналiв:

CS – вхiд вибiрки мiкросхеми. Активним рiвнем є 0, який дозволяє роботу iнтерфейса з МП;

RD – вхiд сигналу зчитування. Дозволяє передачу даних на шину даних МП при RD=0;

WR – вхiд сигналу запису. При WR=0 вiдбувається передача даних або слова стану з шини даних в регiстри iнтерфейса або в зовнiшнi пристрої;

А1, А0 – адреснi входи, що призначенi для вибору одного з портiв вводу–виводу, або регiстра керуючого слова (див.табл.1).

Таблиця 1.

А1 |

А0 |

Вибір порта або регістра керуючого слова |

0 |

0 |

порт А |

0 |

1 |

порт В |

1 |

0 |

порт С |

1 |

1 |

регістр керуючого слова |

а) б)

Рисунок 1. Умовне позначення (а) і функціональна схема інтерфейсу (б)

Rеset–вхiд сигналу скидання. При Reset=1 всi внутрiшнi регiстри обнуляються, а порти А, В, С встановлюються на ввід даних.

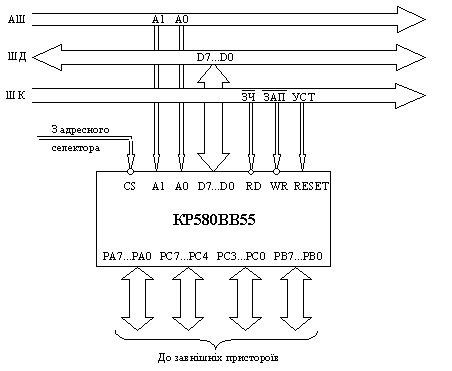

Схема узгодження КР580ВВ55 з системною шиною показана на мал.3. Значення сигналiв керування CS, RD, WR та A0, A1 в режимах запису/зчитування даних,запису керуючого слова та вимикання поданi в табл.2.

Таблиця 2.

CS |

RD |

WR |

A1 |

A2 |

Режим роботи та напрям обміну даними |

0 |

1 |

0 |

0 |

0 |

Шина даних–інтерфейс (ввід) запис даних в порт А |

0 |

1 |

0 |

0 |

1 |

Запис даних в порт В |

0 |

1 |

0 |

1 |

0 |

Запис даних в порт С |

0 |

1 |

0 |

1 |

1 |

запис керуючого слова |

0 |

0 |

1 |

0 |

0 |

Шина даних–інтерфейс (вивід) зчитування порта А |

0 |

0 |

1 |

0 |

1 |

Зчитування порта В |

0 |

0 |

1 |

1 |

0 |

Зчитування порта С |

1 |

Х |

Х |

Х |

Х |

Вимикання |

Х–будь–яке значення (0 або 1).

Рисунок 3. Узгодження КР580ВВ55 з системною шиною