Мікропроцесорна техніка Лабораторна робота №3

ЛАБОРАТОРНА РОБОТА №3

Функціонування МП КР580ВМ80 (i8080)

___________________________________________________________________________

1. МЕТА РОБОТИ.

Дослідження структури , принципу роботи мікропроцесора та виконання окремих команд і простих програм з використанням різних методів адресації в програмах.

2. КОРОТКI ТЕОРЕТИЧНI ВIДОМОСТI.

2.1. СТРУКТУРА МIКРОПРОЦЕСОРА.

Основним пристроєм всiх інформаційних систем е центральний процесор (ЦП), функції якого виконують мікропроцесори. МIКРОПРОЦЕСОР виконує такi основні функції:

- витяг, декодування та виконання команд у вказанiй послiдовностi;

- передача даних з пам’яті та в пам'ять, а також з пристроїв вводу-виводу

(ПВВ) та в ПВВ;

організація загальної синхронізації та сигналів керування для всієї мікропроцесорної системи.

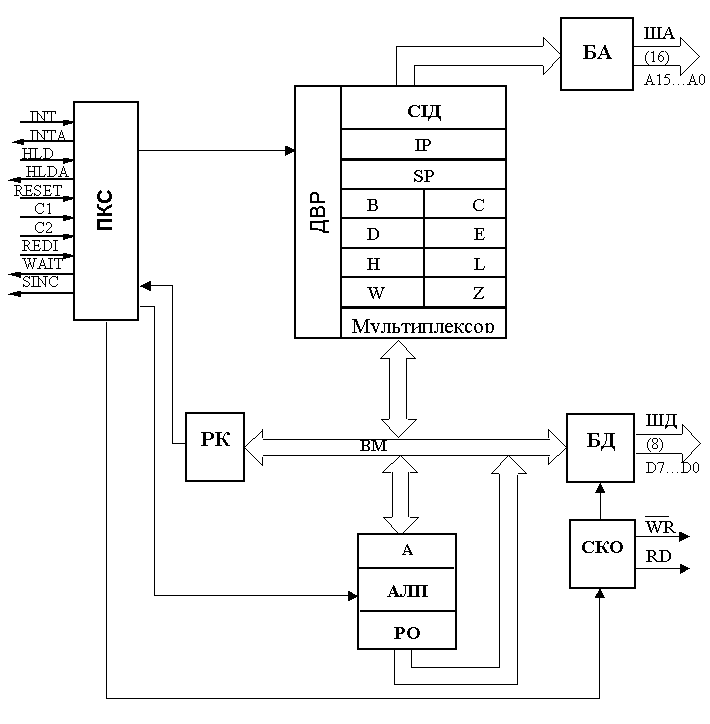

Малюнок 1. Структурна схема мікропроцесора

МІКРОПРОЦЕСОР КР580ВМ80 містить:

- двонаправлену 8-розрядну ШИНУ ДАНИХ (ШД);

- однонаправлену 16-розрядну АДРЕСНУ ШИНУ (ША), яка забезпечує

адресний простір пам'яті в 2^16=64 Кбайт;

- 8-розрядний АРИФМЕТИКО-ЛОГIЧНИЙ ПРИСТРІЙ (АЛП) МП;

-БЛОК РЕГIСТРIВ, що містить:

- 16-розрядний РЕГІСТР АДРЕСИ КОМАНДИ (IP) (він же лічильник

команд РС-Program Counter);

- 16-розрядний РЕГІСТР ВКАЗIВНИКА СТЕКУ (SP - Steсk Pointer);

- 16-розрядний РЕГІСТР ТИМЧАСОВОГО ЗБЕРІГАННЯ (WZ);

- 16-розрядну схему IНКРЕМЕНТА/ДЕКРЕМЕНТА;

- шість 8-розрядних РЕГІСТРІВ ЗАГАЛЬНОГО ПРИЗНАЧЕННЯ (В, С,

D, E, H та L), які можуть використовуватись і як три 16- розрядні

регістри (BC, DE, HL);

- ДЕШИФРАТОР БЛОКУ РЕГІСТРІВ (ДБР);

- ПРИСТРІЙ КЕРУВАННЯ та СИНХРОНІЗАЦІЇ (ПКС);

- РЕГІСТР КОМАНД (РК);

- АКУМУЛЯТОР (А);

- РЕГІСТР ОЗНАК (РО);

- БУФЕР ДАНИХ (БД);

- БУФЕР АДРЕСИ (БА);

- СХЕМУ КЕРУВАННЯ ОБМІНОМ (СКО).

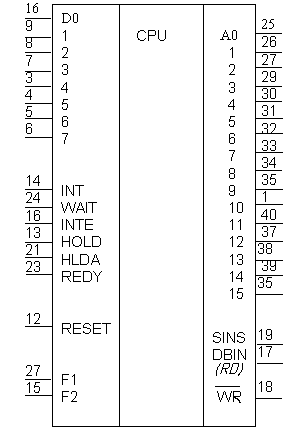

Функціональне призначення виводів МП КР580ВМ80А подане в табл. 1, а його графічне позначення - на мал.2.

Таблиця 1.

Номер |

Позначення |

Найменування |

Назва |

Тип |

Стан |

19 |

SYNС |

Синхронізація |

Ознака початку ма- шинного циклу |

Вихід |

1 |

17 |

DBIN |

Прийом даних |

Ознака зчитування iнформацiї |

-"- |

1

|

18 |

WR |

Запис |

Ознака запису iнформацiї |

-"- |

О

|

23 |

READY |

Готовнiсть |

Сигнал готовностi зовнiшнього пристрою до обмiну інформа цією |

Вхiд |

1 |

24 |

WAIT |

Очiкування |

Ознака переходу в стан очiкування го- товностi зовнiшнього пристрою |

Вихiд |

1 |

14 |

INT |

Запит на переривання |

Сигнал про необхiд- нiсть обмiну по пе- рериванню

|

Вхiд |

1 |

16 |

INTE |

Дозвiл переривання |

Сигнал про готов- нiсть до обмiну по перериванню |

Вихiд |

1 |

13 |

HOLD |

Запит на захоплення |

Сигнал про необхiд- нiсть обмiну за ме- тодом прямого досту- пу до пам'ятi |

Вхiд |

1 |

21 |

HLDA |

Пiдтвердження захоплення |

Ознака переходу до обмiну за методом прямого доступу до пам'ятi |

Вихiд |

1 |

12 |

RESET |

Скидання |

Початкове встанов- лення мiкропроцесора |

Вхiд |

1 |

3-1О |

DO-D7 |

Данi |

Двонаправлена вось- мирозрядна шина да- них |

Вхiд |

Х

|

1,25-27 29-4О |

АО-А15 |

Адреси |

Однонаправлена шiстнадцятирозрядна адресна шина |

Вихiд |

Х

|

Малюнок 2. Умовне позначення МП КР580ВМ80

Призначення основних блоків:

АЛП - виконує всі арифметичні операції (додавання, зсув/перестановка, порівняння, iнкремент, декремент, заперечення), логічні (I, АБО, виключне АБО) та операції зсуву. Результати більшості операцій заносяться в акумулятор;

АКУМУЛЯТОР - 8-розрядний регістр, де зберігається більшість результатів виконання команд;

РЕГІСТР КОМАНД - 8-розрядний регістр, що містить перший байт команди;

ДЕШИФРАТОР КОМАНД - декодує вміст регістра команд, визначає мікропрограму для виконання необхідної команди;

ЛІЧИЛЬНИК КОМАНД - е різновидністю 16-розрядноi пам'яті і містить 16-розрядну адресу виконуваної команди. Вмiст лiчильника автоматично збільшується на одиницю (адреса наступної команди) пiсля завантаження кожного байту команди. Може бути iнкрементований або скинутий пристроєм керування та синхронізації (ПКС).

ПРИСТРIЙ КЕРУВАННЯ та СИНХРОНІЗАЦІЇ - отримує сигнали

дешифратора команд для визначення природи виконуваної команди. Отримує також сигнали вiд регiстра стану у випадку умовного переходу. Передає сигнали керування і синхронізації у всі пристрої системи, А також виробляє сигнали керування зовнішніми пристроями (ОЗП, ПЗП, ПВВ і т.п.).

ВКАЗIВНИК СТЕКУ - мiстить адресу комiрки, яка визначає вершину стеку. Ємність вказiвника стека 16 бiт. Вмiст його зменшується перед записом коду в стек і збільшується пiсля зчитування.

РЕГIСТР ОЗНАК - мiстить iндикатори (флаги):

- знаку S, встановлюється в "1", коли результат операції вiд’ємний;

- нуля Z, якщо результат операції рівний О (встановлюється в "1");

парності P, встановлюється в "1", якщо результат містить парне число

одиниць;

- переносу CY, рівний "1" при наявності переносу (при додаванні) чи займу

(при відніманні) зі старшого розряду;

додаткового переносу AC ("1") при наявності переносу з третього розряду в четвертий (при додаваннi) або займу (при вiднiманнi) з четвертого в третiй.

Флаги регiстра ознак створюють байт керуючого слова, що

керує виконанням програми. Флаги скидаються при вiдсутностi перерахованих станiв.

РЕГIСТРИ ЗАГАЛЬНОГО ПРИЗНАЧЕННЯ - регiстри B, C, D, E, H і

L використовуються для зберiгання даних. Регiстри H і L можуть

використовуватись також як адресний регiстр.

РЕГIСТРИ ТИМЧАСОВОГО ЗБЕРIГАННЯ - (W, Z) призначенi для

прийому та тимчасового зберiгання другого та третього байтiв команд переходiв, що передаються з внутрішньої магiстралi даних в лiчильник команд.

2.3.Органiзацiя стеку.

Пам'ять завжди можна подати у виглядi стовбця комiрок пам'ятi, номери яких зростають зверху вниз. Вибираються адреси в порядку зростання (зверху вниз). Стек (область ОЗП) органiзований таким чином:

- заповнення стеку відбувається знизу вверх;

- вибираеться стек в зворотньому напрямку (див. мал.4);

Вказiвник стеку (SP) зберігає адресу останньої зайнятої комiрки ("вершини") стека. Команди, що використовують стек, переносять два байти (наприклад, вмiст пари регiстрiв H, L) таким чином, що вмiст старшого регiстра H (high) розміщується за адресою АS-1 (AS- початковий код адреси, що мiститься в SP до моменту пересилання), а молодшого L (low) - за адресою AS-2 (мал. 4).

Пiд час вибiрки двох байтiв спочатку вибирається молодший байт (AS-2), а потiм за адресою на одиницю бiльшу (AS-1) старший. Вмiст SP при цьому збільшується на два. В момент переривання основної програми в стек завантажується вміст лічильника команд, а в лічильник команд завантажується адреса першої команди підпрограми. Після закінчення програми переривання в лічильник команд повертається із стека значення

наступної до переривання команди основної програми (адреса повертання).

2.4. Слово стану мп

На першому такті Т1 кожного циклу МП видає на шину даних (магiстраль даних) так зване слово стану - код, що ідентифікує вид виконуваного циклу та інформує мiкропроцесорну систему про режим роботи МП. Слово стану зберігається на ШД тільки на протязі одного такту, тому для його зберiгання на час циклу використовують додатково спецiальний регiстр слова стану РСт. Інформація в РСт записується за сигналом SYNC на початку кожного циклу .

В табл.2 приведенi слова стану для всiх десяти циклiв МП К58ОВМ8О.

Таблиця 2

Цикли |

Назва циклу |

Значення розряду стану слова |

|||||||

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

||

М1 |

Вибiрка команди |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

М2 |

Зчитування з пам'ятi |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

М3 |

Запис в пам'ять |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

М4 |

Зчитування з стека |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

М5 |

Запис в стек |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

М6 |

Ввiд з зовнiшнього пристрою |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

М7 |

Вивiд в зовнiшнiй пристрiй |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

М8 |

Переривання |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

М9 |

Зупинка |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

М10 |

Переривання в зупинцi |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

В табл.3 поданi характеристики кожного розряду слова стану.

Таблиця 3

Позначення |

Розряд |

Характеристика |

|

D7 |

Дозвiл звертання до пам'ятi. D7 = 1 вказує, що шина даних буде використана для зчитування даних з пам'ятi. |

D6 |

Дозвiл звертання до iнтерфейсних та периферiйних пристроїв. D6 = 1 вказує, що на адресну шину видана адреса порта або блока, данi з якої повиннi поступити на шину даних. |

D5 |

Iндикацiя знаходження МП в першому циклi команди (цикл вибiрки команди) (D5 = 1). |

D4 |

Дозвiл виводу. При D4 = 1 iнформацiя на ШД готова до виводу в порти iнтерфейсу. |

D3 |

Iндикацiя знаходження МП в станi HALT (D3 = 1). |

D2 |

Вказiвник стеку. При D2 = 1 - дозволяється звертатись (записувати чи зчитувати) до стековоi областi ОЗП. |

D1 |

Вказiвник режиму обмiну даними. При D1 = О - вивiд даних з МП; D1 = 1 - ввiд даних в МП. |

D0 |

Обслуговування переривання. DО = 1. Разом iз сигналом переривання ініціює перехiд до пiдпрограми обслуговування. |

Розряди D7, D6, D4, DО використовують для формування сигналiв шини керування (рис.6). D3, D2, D1 - для індикації режимiв роботи МП.

Позначення до мал. 5:

ОП - обслуговування пам'ятi . ОП = DBIN*DО. Формується в першому циклi переривання. При ОП = О на ШД видається код команди, що визначає початкову адресу пiдпрограми обслуговування переривання.

ЗП - запис в пам'ять. ЗП = WR*D4. При ЗП = О дозволяється запис даних в ОЗП.

ЧП - зчитування з пам'ятi. ЧП = DBIN*D7. При ЧП = О дозволяє видачу даних з ОЗП на ШД МП.

ЧВ - зчитування з елементiв МП-системи за командою вводу IN. ЧВ = DBIN*D6. При ЧВ = О елемент МП-системи, до якої звертається МП за певною адресою, дозволяе видачу пристроєм вводу-виводу даних на ШД.

ЗВ - запис в елементи МП-системи за командою OUT. ЗВ = WR*D4. При ЗВ = О дозволяється запис даних з ШД в буферний регiстр елементiв МП-системи.