Архитектуры оперативной памяти

Давайте в первую очередь определим, какими факторами определяется производительность оперативной памяти.

Естественно было бы основным фактором производительности системы оперативной памяти назвать ее пропускную способность, т.е. количество мегабайт в секунду, которое способна считать (записать) оперативная память. Разумеется, пропускная способность оперативной памяти напрямую зависит от частоты работы чипов памяти и от ширины шины, связывающей память и процессор, и обычно определяется как произведение ширины шины на частоту ее работы. Например, ширина шины 64 бита, частота работы памяти 100 МГц, пропускная способность - 8 байт (64 бита) * 100 МГц = 800 Мбайт/с.

Но пропускная способность - не единственный фактор, определяющий производительность подсистемы памяти. Важнейшим параметром также является время доступа, т.е. временная задержка между запросом на выдачу какой-либо информации из памяти и ее реальной выдачей. Какая память лучше: с малой задержкой и малой пропускной способностью или с большой задержкой и большой пропускной способностью? Однозначного ответа на этот вопрос, конечно, быть не может. Если конкретная программа работает с большими массивами непрерывных данных, т.е. лишь однажды получает доступ, а затем много линейно считывает, то для такой программы оптимальна память с большой пропускной способностью, а если программа оперирует малыми блоками данных, т.е. постоянно получает доступ к разным областям памяти и понемногу читает из каждой области, то оптимальна память с малым временем доступа, а пропускная способность имеет меньшее значение. Так как обычно на компьютере исполняются разные приложения, то очень трудно найти компромисс. В общем случае, естественно, необходимо стремиться к тому, чтобы и время доступа и пропускная способность памяти были хорошими. Разобравшись с параметрами скорости, которыми мы будем описывать архитектуру памяти, теперь можно рассмотреть какие конкретно типы памяти применялись и применяются в персональном компьютере.

DRAM

В самых первых PC в качестве оперативной памяти использовалась так называемая DRAM (Dynamic RAM). Ячейки памяти в микросхеме DRAM - это крошечные конденсаторы, которые удерживают заряды. Именно наличием или отсутствием заряда кодируются биты. Основная проблема такой организации памяти в том, что она динамическая, т.е. должна регенерироваться, так как в противном случае заряды с конденсаторов "стекают" и данные будет потеряны. Регенерация происходит, когда контроллер памяти системы (встроенный обычно в чипсет) берет перерыв и обращается ко всем строкам данных в микросхеме памяти. Регенерация,

естественно, занимает время работы системы, во время, когда происходит регенерация памяти, процессор фактически ждет, ничего полезного не делая. Чем быстрее происходит регенерация, тем меньше процессорного времени теряется и тем производительнее работает система.

В DRAM для хранения одного бита данных используется только один транзистор и один конденсатор, поэтому технология DRAM позволяет делать достаточно компактные чипы с немалой емкостью. Например, сегодня существуют чипы, базирующиеся на технологии DRAM емкостью 512 Мбит, т.е. они содержат 1/2 миллиарда транзисторов. Для сравнения в современных процессорах количество транзисторов измеряется десятками миллионов. Но структура чипа DRAM весьма проста, представляя собой двумерную матрицу, в отличие от сложной архитектуры современного процессора. Итого: основное достоинство динамической памяти - немалая емкость при малых физических размерах чипа и небольшая цена. Применяемые в первых компьютерах и применяемые сегодня архитектуры памяти базируются в основном на динамической памяти. Давайте рассмотрим разновидности DRAM, нашедшие применение в PC и их достоинства.

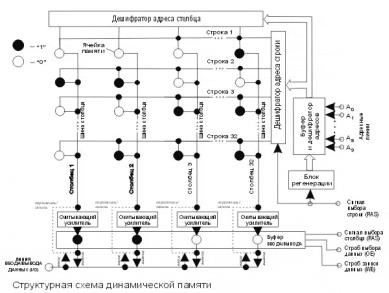

Принцип работы динамической памяти

Ячейки памяти организованы в матрицу, состоящую из строк и столбцов. Полный адрес ячейки данных включает два компонента — адрес строки (row Адрес, бит) и адрес столбца (column Адрес, бит). На рисунке представлена матрица, состоящая из 32 строк и 32 столбцов, то есть из 1024 ячеек.

Когда CPU (или устройство, использующее канал DMA) обращается к памяти Для чтения информации, на входы микросхемы поступает строб вывода данных ОЕ (Output Enabled), затем подается адрес строки и одновременно с ним (или с задержкой) сигнал RAS (Row Адрес, бит Strobe). Это означает, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Адрес ячейки поступает по адресным линиям (в на-

шем случае их десять) на дешифратор, который преобразует поступивший набор нулей и единиц в номер строки. Емкость конденсатора очень мала (доли пикофарады) и его заряд тоже мал, поэтому используется усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помешается в буфер ввода-вывода.

С незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS (Column Адрес, бит Strobe). При чтении данные выбираются из буфера ввода-вывода и поступают на выход динамической памяти в соответствии с адресом столбца.

При считывании информации из ячеек памяти происходит ее разрушение, поэтому производится перезапись считанной информации: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную информацию из строки. Если ячейка имела заряд, то она снова будет заряжена еще до завершения цикла чтения. На ячейки, которые не имели заряда, напряжение не подается.

Если выполняется запись в память, то подается строб записи WE (Write Enable) и информация поступает на соответствующую шину столбца не из буфера, а с входа памяти в соответствии с адресом столбца. Таким образом, прохождение данных при записи задается комбинацией сигналов, определяющих адрес столбца и строки, а также сигналом разрешения записи данных в память.

FPM DRAM

Первой, нашедшей применение в PC модификацией DRAM, была память, которая работала в так называемом быстром страничном режиме и ее принято называть FPM DRAM (Fast Page Mode DRAM) или просто FPM.

Чтобы сократить время ожидания на выборку данных (на доступ) стандартная DRAM разбивается на страницы. Обычно для доступа к данным в памяти требуется указать строку и столбец адреса, что занимает некоторое время. Разбиение на страницы обеспечивает более быстрый доступ ко всем данным в пределах данной строки памяти, т.е. если изменяется лишь номер столбца, но не номер строки.

Страничная организация памяти - простая схема повышения эффективности, в соответствии с которой память разбивается на страницы от 512 байт до нескольких килобайт. Соответствующая схема обращения позволяет в пределах страницы уменьшить количество состояний ожидания.

Чтобы увеличить скорость доступа к памяти был разработан так называемы пакетный (burst) режим доступа. Преимущества пакетного режима доступа проявляются тогда, когда доступ к памяти является последовательным (т.е. считывание происходит последовательно одно за другим из соседних ячеек). После задания строки и столбца и считывания информации, к следующим трем соседним адресам можно обращаться без дополнительных циклов ожидания. Однако доступ в таком пакетном ре-

жиме ограничивается лишь четырьмя операциями чтения-записи, затем необходимо снова полностью адресоваться к строке и столбцу.

Принято говорить о схеме синхронизации доступа в пакетном режиме в виде x-y-y-y, где х - количество тактов ожидания для произведения чтения первого адреса, а затем y - количество тактов ожидания для чтения каждого следующего адреса в пакетном режиме. (Такт - один период электромагнитного колебания той частоты, на которой работает память. Например: частота памяти 100МГц, один период равен 1/100млн, т.е. равен 10нс).

Архитектура DRAM такова, что для получения доступа первый раз необходимо 5 тактов ожидания. Если не разбивать память на страницы и не пользоваться пакетным режимом доступа, то каждая следующая операция получения доступа к следующей ячейке памяти тоже будет занимать 5 тактов ожидания. Однако если пользоваться разбиением на страницы и режимом burst, то, получив доступ первый раз, потратив на это 5 тактов ожидания, содержимое следующих ячеек можно считать, потратив на это лишь три такта ожидания, т.е. в режиме FPM схема доступа имеет вид не 5-5-5-5, как у обычной DRAM, а 5-3-3-3. В этом и преимущество памяти типа FPM перед обычной DRAM. Т.е. использование памяти типа FPM позволяет при той же частоте работы чипов памяти увеличить производительность обмена за счет сокращения времени на получение доступа к памяти.

EDO DRAM

Начиная с 1995 года, в PC используется новый тип оперативной памяти - EDO (Extended Data Out). Это усовершенствованный тип памяти FPM, у него было еще одно название, которое сейчас не используется Hyper Page Mode. Микросхемы памяти EDO учитывают перекрытие синхронизации между очередными операциями доступа. За счет этого удается частично совместить по времени следующий цикл чтения с предыдущим, т.е. чипсет при работе с EDO памятью может начать выполнение новой команды выборки столбца, пока данные считываются по текущему адресу, за счет чего еще уменьшаются задержки на получение доступа.

Для оперативной памяти EDO схема синхронизации в пакетном режиме имеет вид 5-2-2-2, т.е. на четырех операциях считывания тратится не 14, а 11 тактов. Т.е. налицо явный прирост производительности, в то время как стоимость чипов типа EDO лишь немного отличалась от чипов

FPM.

Пока что все рассмотренные нами архитектуры были лишь вариантами оригинальной DRAM, отличаясь схемой доступа в пакетном режиме, что, конечно, давало соответствующий прирост производительности. Частоты, на которых функционировала память перечисленных типов примерно таковы: DRAM функционировала с частотой 4,77 МГц (в первых PC) до 10-12 МГц. Затем применялась память типа FPM, ее частота функционирования составляла 10-40 МГц в 386 системах, 25-50 МГц в 486 системах

и 50-66 МГц в Pentium системах. Память типа EDO применялась наряду с FPM в 486 и Pentium системах на аналогичных частотах. Те технологии, которые мы рассмотрели на данный момент, можно назвать вчерашним днем. Что мы видим в период развития архитектуры памяти в период с первых PC, до середины доминирования на рынке процессоров Pentium?

Улучшение идеологии построения чипов памяти, приведшее к разработке новых типов архитектур (в рамках DRAM), в каждой новой архитектуре применяется новая схема работы с памятью, приводящая к уменьшению задержек при получении доступа и планомерное увеличение тактовой частоты работы памяти. При этом нужно отметить, что увеличение тактовой частоты памяти увеличивает не только пропускную способность (естественно, линейно), но и уменьшает время доступа. Почему?

Мы описывали время доступа как количество тактов ожидания, соответствующих задержке перед получением доступа. Но ведь реальная задержка измеряется в единицах времени, а не в каких-то абстрактных тактах. А величина одного такта как раз и определяется тактовой частотой, на которой работает память. Ведь чем больше тактовая частота, тем меньше время одного такта, и, следовательно, тем меньше время доступа. Если, к примеру, память работает на частоте 100 МГц, то время одного такта 1/100млн = 10нс, и 5 тактов ожидания соответствуют задержке в 50нс, то при частоте работы памяти 133 МГц время одного такта 7,5 нс, а задержка в 5 тактов равна 37,5 нс.

Давайте теперь поговорим об оперативной памяти дня сегодняшнего, а затем и памяти завтрашнего дня.

SDRAM

Уже начиная с 1997 года на смену памяти типа FPM и EDO приходит новый тип оперативной памяти: SDRAM (Synchronous DRAM) - синхронная DRAM. Эффективность SDRAM намного выше, чем у ее предшественников. Во-первых, дело в том, что схема пакетного чтения у SDRAM намного эффективнее, чем у EDO или FPM и описывается формулой 5-1-1-1. Т.е. для считывания четырех значений подряд задержка для памяти типа

FPM составит 5+3+3+3=14 тактов, у EDO 5+2+2+2=11 тактов, а у SDRAM 5+1+1+1=8 тактов.

Но это еще не все. Дело в том, что SDRAM более технологична, чем ее предшественники, и ее проще изготовить для работы на более высоких частотах. И если впервые SDRAM применяли в PC на частоте 66 МГц (как и EDO и FPM в то время), то затем были разработаны чипы SDRAM, работающие на частоте 100 МГц, а после и 133 МГц. Но время SDRAM практически завершилось. Сегодня компьютерная индустрия использует в качестве современной оперативной памяти компьютера две технологии - DDR SDRAM и DR DRAM.