- •Глава 1: Микропроцессор. Основные сведения

- •1.1 Основные характеристики мп

- •1.2 Структура мп устройства

- •1.3 Запоминающие устройства

- •1.4 Оперативное запоминающее устройство

- •1.5 Постоянные зу

- •Глава 2: Восьмиразрядный мп кр580

- •2.2 Система и формат команд. Способы адресации

- •2.3 Словосостояние мп

- •2.4 Работа устройства управления в режиме прерывания

- •2.5 Работа устройства управления в режиме прямого доступа к памяти (пдп)

- •Глава 3: Интерфейс Общие сведения

- •3.1Организация прерывания. Арбитраж

- •3.2 Программируемый периферийный адаптер

- •3.3 Программируемый связной адаптер

- •3.3.1 Работа пса в асинхронном режиме

- •3.3.2 Работа пса в синхронном режиме

- •3.4 Программируемый контроллер прерывания

- •3.5 Контроллер прямого доступа к памяти

- •Глава 4: 16-разрядный мп кр1810вм86

- •4.1 Структура мп кр1810

- •4.1.1 Устройство сопряжения с шиной

- •4.1.3 Устройство управления

- •4.2 Система и формат команд

- •4.2.1 Формат команд

- •4.2.2 Система команд

- •Глава 5: Микроконтроллеры

- •5.1 Классификация мкс

- •Глава 6: мк семейства Microchip

- •6.1 Процессорное ядро

- •6.1.1 Организация памяти

- •6.1.1 Организация памяти данных.

- •6.2 Организация периферийных модулей

- •6.2.1 Порты ввода/вывода

- •6.2.2 Модуль прерывания

- •Структурная схема модуля ацп

- •6.3 Периферийные модули специального назначения

- •6.3 Система и формат команд. Способы адресации

- •6.4 Средства разработки семейства Microchip

- •Глава 7: мк mcs 51

- •7.1 Организация памяти

- •7.2 Режим общего напряжения и электропитания

- •7.3 Модули ацп

- •7.4 Модуль цап

- •7.5 Периферийные модули

- •7.5.1 Последовательные порты ввода

- •7.5.2 Таймеры

- •7.5.3 Программируемый массив счетчиков (pca)

- •7.6 Модули захвата сравнения pca

- •7.7 Порты ввода

- •7.8 Система и формат команд

- •7.9 Способы адресации

- •7.10 Типы команд мк

- •Глава 7: применение програмируемых цифровых устройств в системах безопастности

- •8.1 Организация передачи информации

- •8.2 Параллельный интерфейс периферии lpt

- •8.3 Интерфейс rs232 (com порт)

- •8.4 Интерфейс Токовая петля

- •8.5 Интерфейс i2c

- •Глава 9: Применение мп техники

- •9.1 Разработка алгоритма управления.

- •9.2 Разработка структуры аппаратных и программных средств.

- •9.3 Совместная отладка

- •9.4 Сертификация

- •9.6 Измерительные системы

- •9.7 Системы управления

6.2 Организация периферийных модулей

6.2.1 Порты ввода/вывода

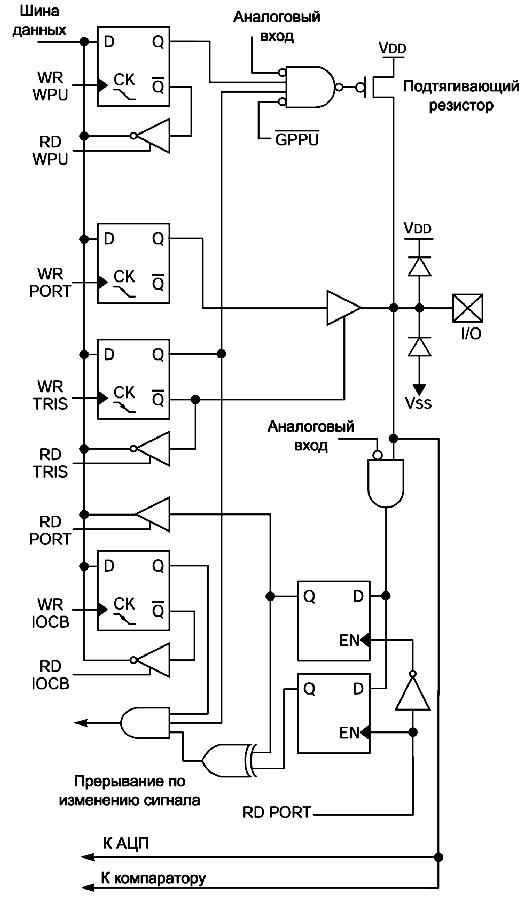

В рассматриваемом МК реализовано 6 каналов порта ввода/вывода, т.е. один порт в неполном объеме. Существуют МК, в которых количество портов может быть до 4-х и носят названия соответственно Port А, B, C, D. Все каналы портов ввода/вывода. Все каналы портов мультиплексированы с дополнительными функциями периферийных модулей МК. При этом линия порта ввода/вывода может работать как порт ввода/вывода или как линия периферийных функций. Непосредственно работу портов задает регистр GPIO, который и представляет собой 6-разрядный порт, т.е. логическая 1 в соответствующем разряде определяет высокий уровень на данном выходе порта. Все каналы GPIO имеют соответствующие биты направления, расположенных в регистре TRISIO, позволяющие настраивать канал как вход или выход. Запись «1» в TRISIO переводит соответствующий выходной буфер в 3-е состояние. Запись «0» в регистр TRISIO определяет соответствующий канал как выход, содержимое защелки GPIO передается на вывод микроконтроллера. Вывод GP3 может работать только на вход, чтение соответствующего бита TRISIO дает результат «1».

Чтение регистра GPIO возвращает состояние на выводах порта, а запись производится в защелку GPIO. Все операции записи в порт выполняются по принципу «чтение - модификация - запись», т.е. сначала производится чтение состояния выводов порта, затем изменение и запись в защелку. Биты регистра TRISIO управляют направлением канала GPIO, даже если они используются как аналоговые функции, т.е. пользователь программно должен задать режимы работы внешних портов. Дополнительно порты GPIO содержат индивидуальные биты разрешения прерывания по изменению уровня сигналов, данная информация хранится в регистре IOGB. Кроме этого каналы программно могут подключать внутренние подтягивающие резисторы при работе портов на вход. Данные резисторы автоматически выключаются при настройке порта на выход. Информация о данных резисторах находится в регистре WPU. Работа прерывания по изменению уровня сигнала на входе заключается в следующем: сигнал на выходе GPIO постоянно сравнивается со значением, сохраненным при последнем чтении регистра GPIO. В случае несовпадения одного из значений формируется флаг события и пре разрешенном прерывании генерируется прерывание.

Можно условно выделить:

1)блок управления портом. Сюда входят 4 D-триггера, представляющие собой защелки соответствующих разрядов регистров: GPIO, TRISIO, WPU, IOCB.

2)дополнительные функции. Подтягивающий резистор, представляющий собой p-n-переход с модулем управления (R=50кОм).

3)блок формирования прерывания. 2 динамические D-триггера с выходным сигналом формирования события.

Порт ввода/вывода имеет защитные диоды, позволяющие принимать сигналы от -0,6 относительно земли до + 0,6 В от напряжения питания.

Порт GP0 имеет мультиплексированные возможности работать как аналоговый вход, так и положительный вход встроенного компаратора. Для работы порта ввода/вывода используются следующие регистры специального назначения:

GPIO

TRISIO (регистр направления)

ANSEL (регистр выбора аналогового или цифрового канала)

WPU, IOCB

INTCON, OPTIONREG, CMCON (регистры определяют дополнительные функции портов)