- •1 Загальні відомості

- •6 Відладка програми

- •7 Налаштування параметрів імітатора

- •ATmega128, aTmega128l 8-розрядний avr-мікроконтролер з внутрішньосистемною програмованою флеш-пам'яттю ємністю 128 кбайт Особливості:

- •Короткий огляд

- •Завдання:

- •Лабораторна робота №2 «Вивчення математичних і логічних операцій і їх вплив на біти-стану мікроконтролера» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №3 «Вивчення методів додавання і віднімання чотирьохбайтних чисел» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Лабораторна робота №5 «Вивчення роботи з пам’яттю даних» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №6 «Вивчення операцій порівняння і реалізація циклічних операцій» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Завдання:

- •Часові діаграми таймера-лічильника 0

- •Опис регістрів 8-розрядного таймера-лічильника 0

- •Асинхронна робота таймера-лічильника 0

- •Дільник частоти таймера-лічильника 0 Дільник частоти таймер-лічильника 0

- •Завдання:

- •Завдання:

- •Набір інструкцій

Завдання:

1. Проініціалізувати стек

2. Здійснити стартову настройку таймера лічильника 0

2.1 Регістр порогу порівняння OCR0 рівним 78 (десяткове число)

2.2 Регістр управління таймером-лічильником 0 TCCR0

2.2.1 Біт примусової установка результату порівняння FOC0 = 0b0

2.2.2 Режим Скидання при збігу (CTC): WGM01, WGM00 = 0b10

2.2.3 Вихід OC0 відключений: COM01, COM00 = 0b00

2.2.4 Тимчасово таймер відключений: CS02, CS01, CS00 = 0b000

2.3 Регістр маски переривань скидаємо TIMSK = 0

2.4 Запускаємо таймер лічильник 0 з встановленням подільника частоти 25652: CS02, CS01, CS00 = 0b110

3. Написати підпрограму очистки біту OCF0 у регістрі TIFR53

3.1 Регістри, які будуть використовуватися у підпрограмі попередньо зберегти у стеку, для того, щоб їх використання не вплинуло на виконання всієї програми

3.2 Підготувати маску регістра з встановленим бітом під номером OCF0, всі інші біти мають бути очищеними

3.3 Записати цю підготовлену маску у регістр вводу-виводу TIFR – ця процедура очистить біт OCF0 у регістрі вводу-виводу TIFR.

3.4 Відновити регістри збережені у стеку

3.5 Вийти з підпрограми

4. Реалізувати безперервний цикл, який перевіряє чи лічильник досяг пирогового значення

4.1 Завантажити у регістр загального призначення регістр вводу-виводу TIFR

4.2 У разі, якщо біт під номером OCF0 встановлений, то перейти на підпрограму очистки біту OCF0 у регістрі TIFR

4.3 Перейти на пункт 4.1

5. Хід виконання програми

5.1 Зайти у стимулятор

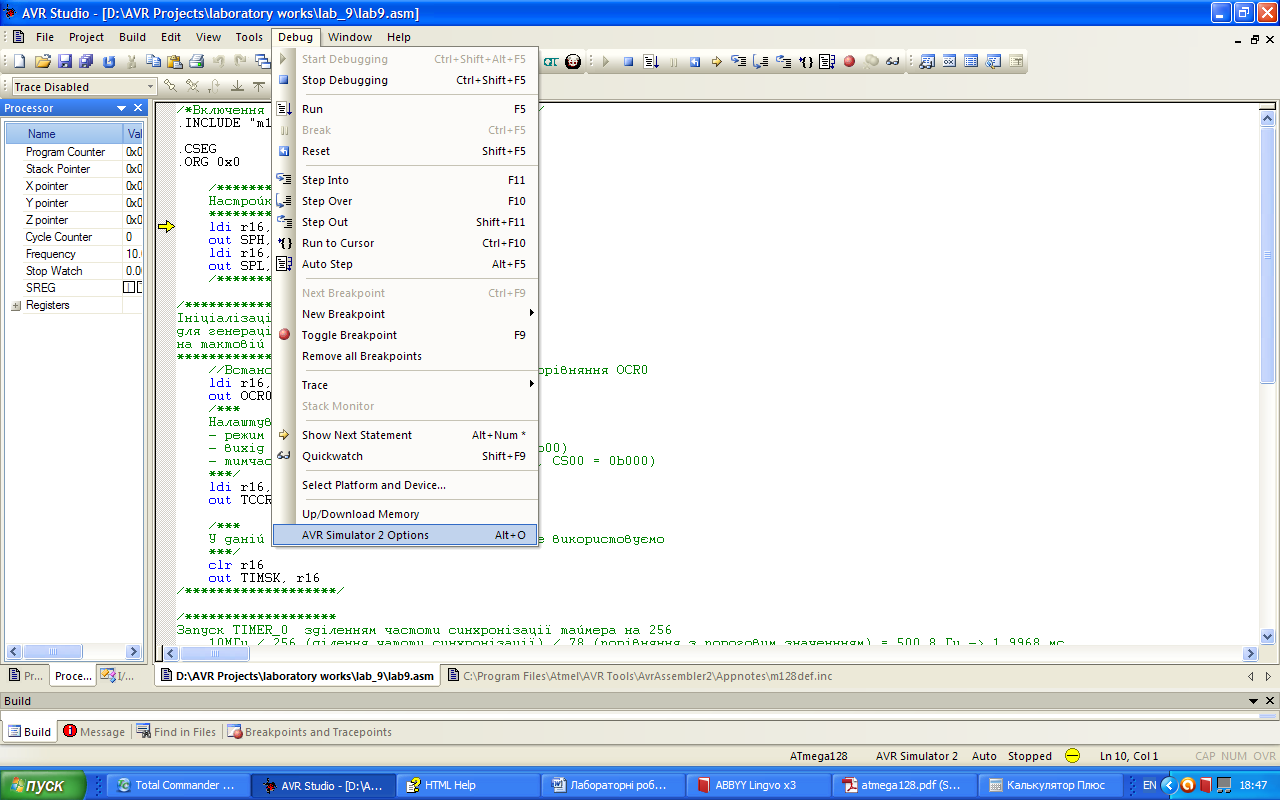

5.2. Відкрити настройки стимулятора Debug→AVR Simulator 2 Options

5.3 Найти поле Frequency MHz – тактова частота процесора

5.4 Встановити поле Frequency MHz 10.000000 МГц – нову тактову частота процесора

5.5 В такому разі у режимі CTC (поріг порівняння OCR0 рівне 78) і подільнику частоти 256 (CS02, CS01, CS00 = 0b110 регістра TCCR0) 10 МГц/256/78 ≈ 500 Гц (2 мс період встановлення біту OCF0)

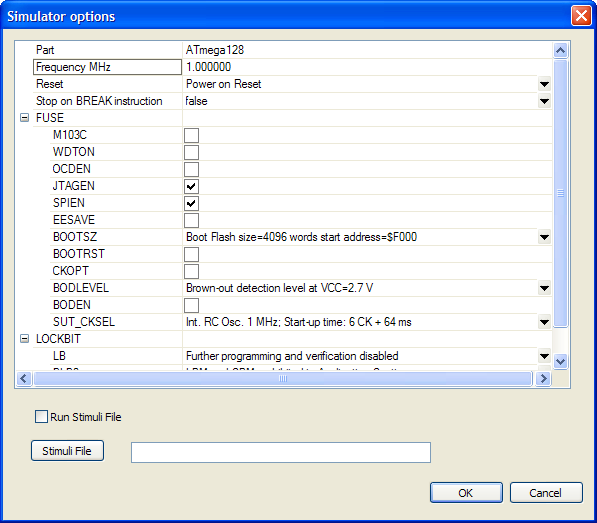

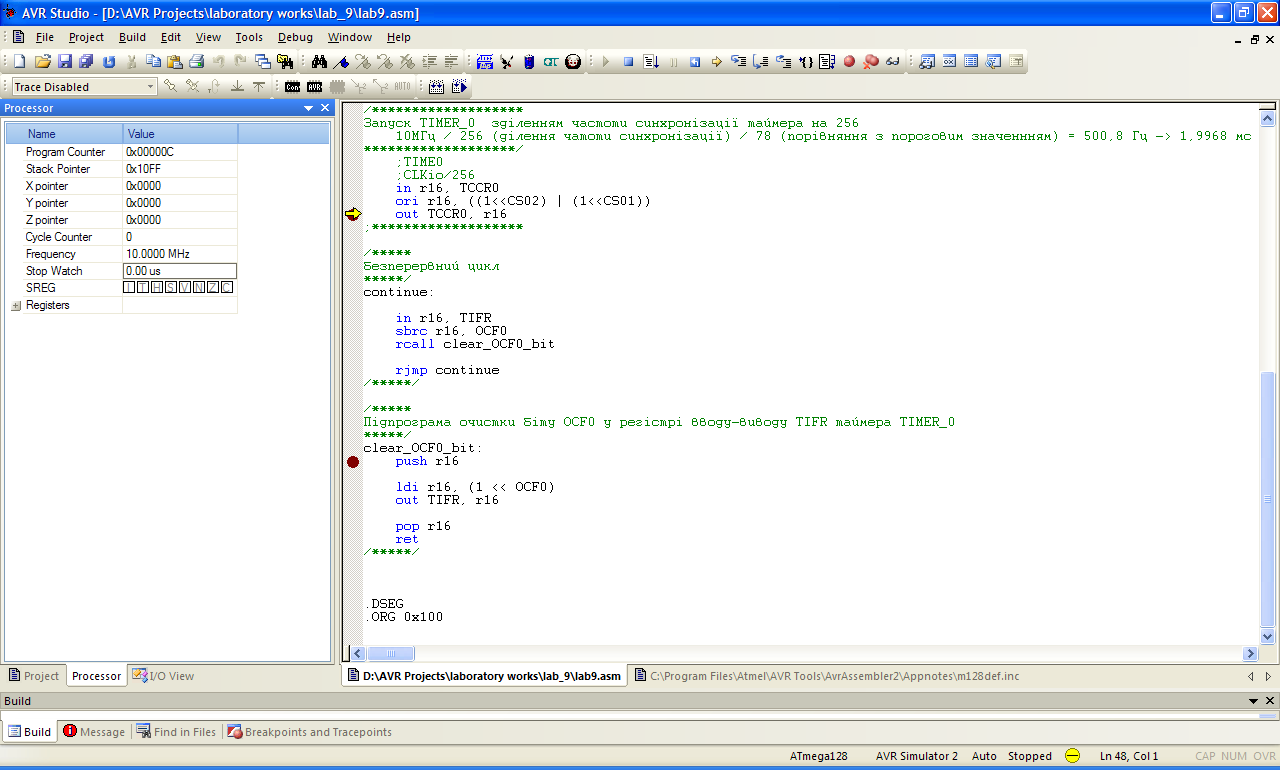

5.6 Стати курсором на рядку, де запускається таймер-лічильник 0, (де виконується встановлення CS02, CS01, CS00 = 0b110) і у цьому місця поставити точку зупинки (breakpoint) Debug→Toggle Breakpoint або функціональною кнопкою F9

5.7 Переконатися, що точка зупинки встановлена – збоку рядка буде червоний кружечок

![]()

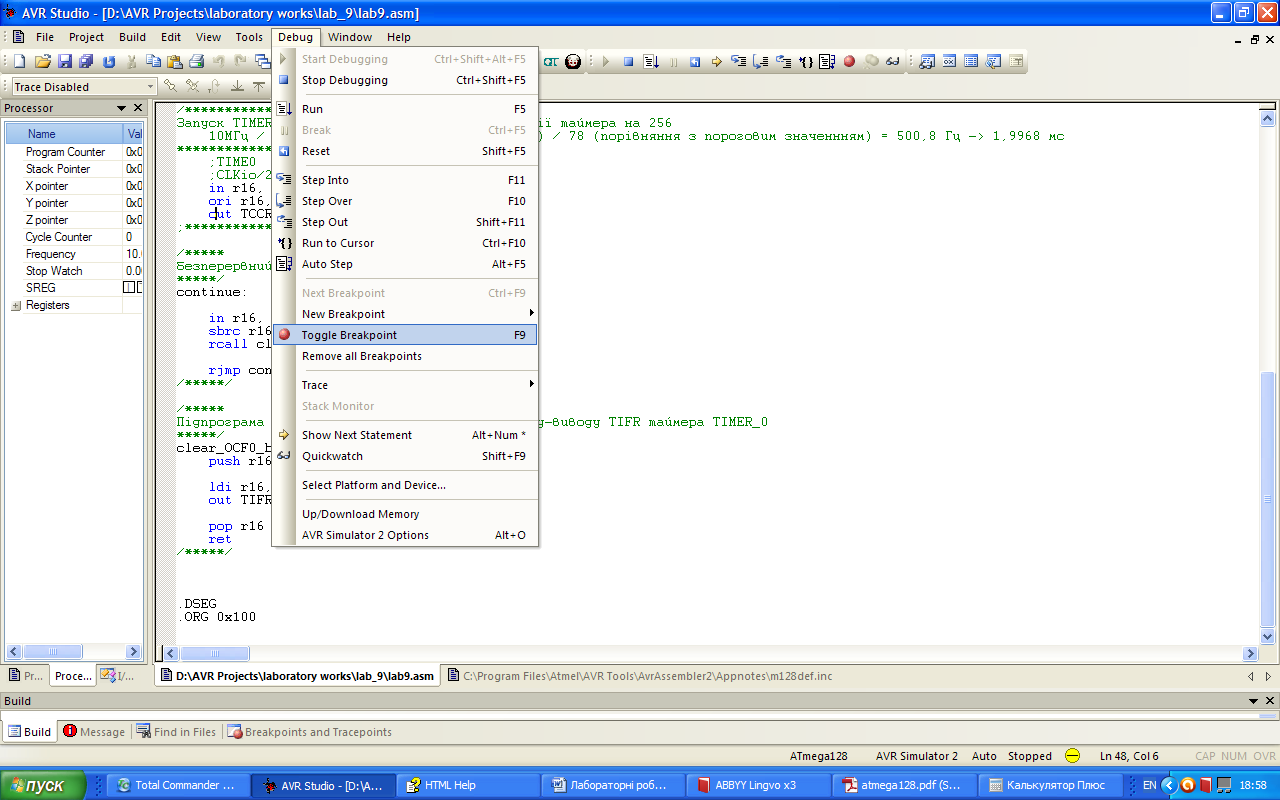

5.8 Аналогічно пунктам 5.6 і 5.7 встановити точку зупинки ум підпрограмі очищення біту OCF0 у регістрі вводу виводу TIFR

5.9 Запустити програму на виконання (не покроково) Debug→Run, або функціональною кнопкою F5

5.10 Програма має зупинитися у першій точці зупинки

5.11 Перейти у вікно Processor (якщо воно не відкрите, то його можна відкрити View→Toolbars→Processor)

5.11 Переконатися, що поле Frequency рівне 10.0000 МГц

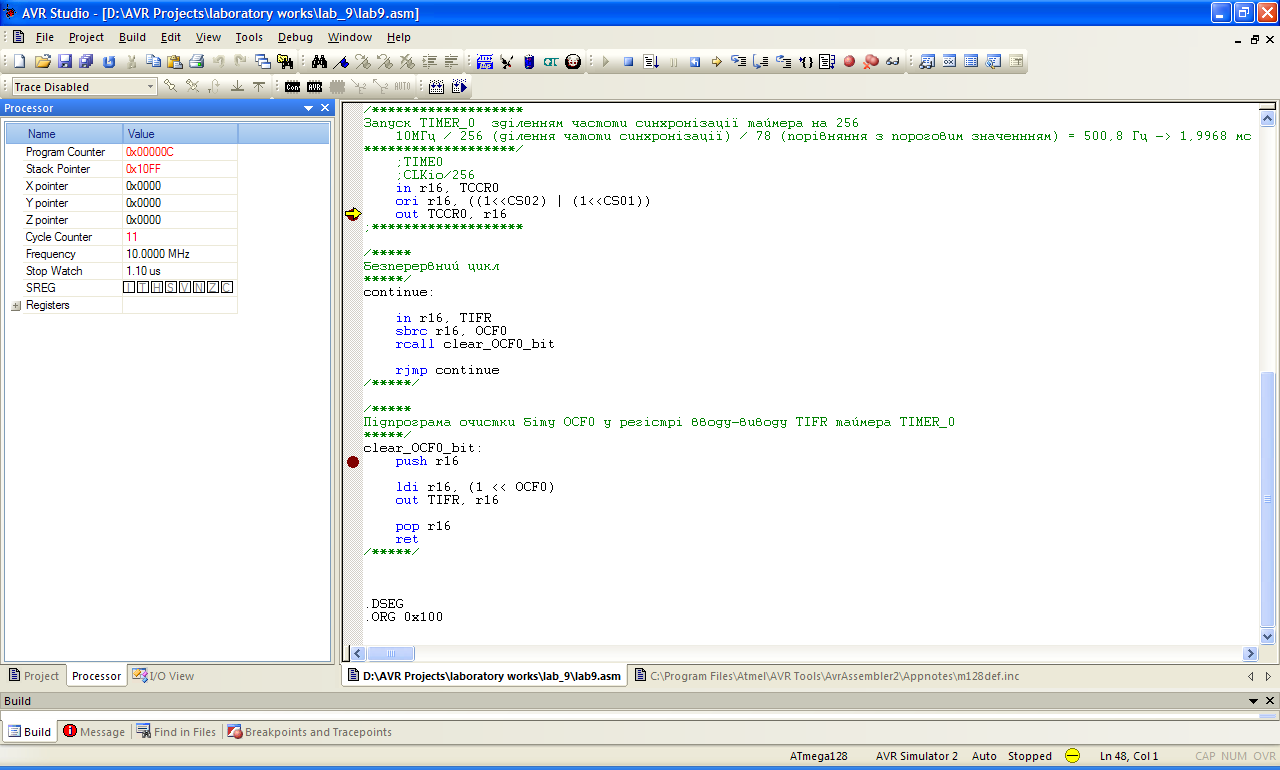

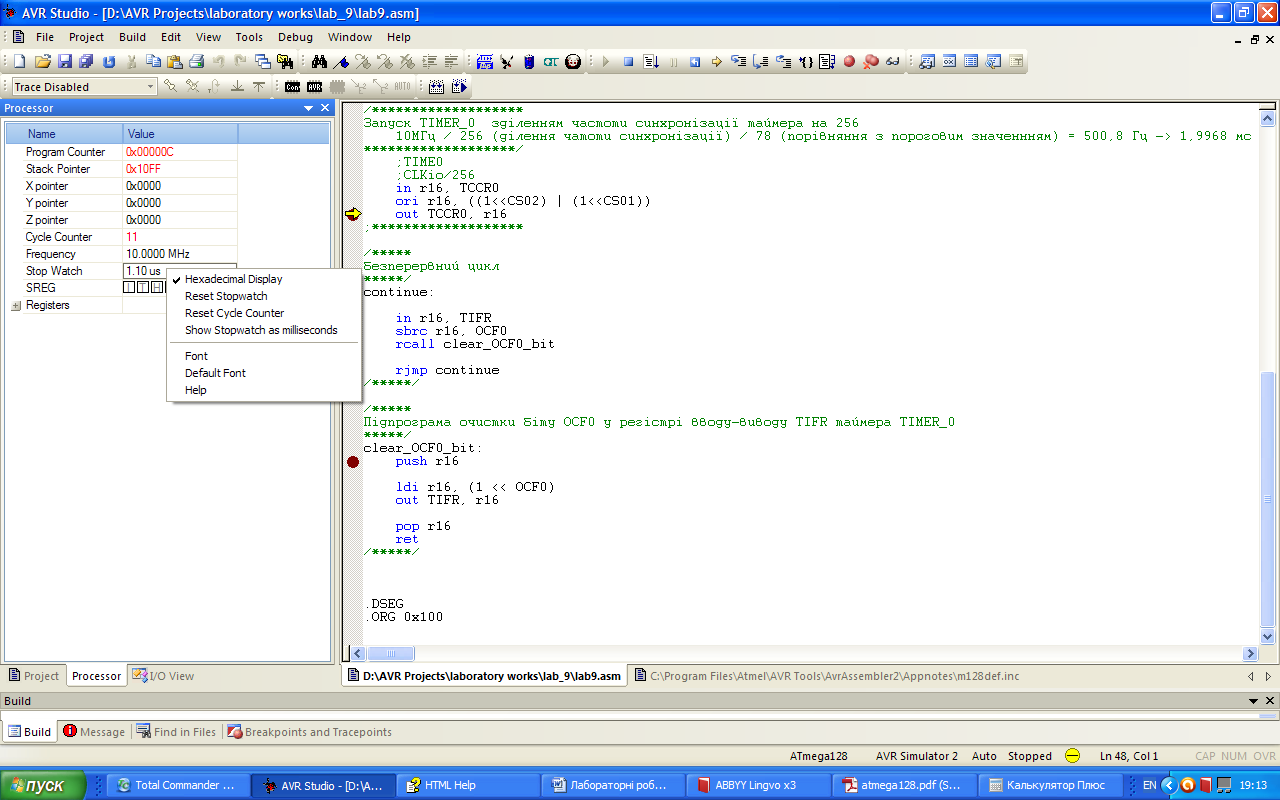

5.12 Правою кнопкою мишки клікнути по полю Stop Watch вікна Processor – контекстне меню, яке зображено нижче

5.13 Якщо після числового значення у полі Stop Watch вікна Processor (яке відповідає за час, який пройшов або з моменту запуску програми, або обнулення часу операцією Reset Cycle Counter з контекстного меню, яке було описане вище) стоїть us, то час відображається у мікросекундах, якщо ms – у мілісекундах. Переключення відображення часу з мікросекунд у мілісекунди виконується операцією Show Stopwatch as milliseconds з контекстного меню, яке описане вище, а з мілісекунди у мікросекунди - Show Stopwatch as microseconds

5.14 Обнулити час у полі Stop Watch вікна Processor командою Reset Cycle Counter, описаною вище і переконатися, що час справді рівний 0. При цьому вибір відображення часу у мікросекундах чи мілісекундах можна вибрати на розсуд виконавця лабораторної роботи (студента)

5.15 Запустити програму на виконання (не покроково) Debug→Run, або функціональною кнопкою F5

5.16 Програма має зупинитися у підпрограмі очищення біту OCF0 у регістрі вводу виводу TIFR

5.17 Переконатися з допомогою поля Stop Watch вікна Processor, що час, за який встановився біт OCF0 у регістрі вводу виводу TIFR становить ≈2 мс

5.18 Декілька разів продовжувати виконання програми (не покроково) Debug→Run, або функціональною кнопкою F5 – переконатися, що програма заходить у підпрограму очистки OCF0 у регістрі вводу виводу TIFR через ≈2 мс.

Лабораторна робота №10 «Вивчення використання переривань мікроконтролера AVR»

Ціль роботи

вивчити принципів роботи переривань AVR мікроконтролера

закріпити знання попередніх лабораторних роботах

Програма виконання роботи

- проініціалізувати таймер на фіксацію проміжку часу у 2 мс (період можна змінити) з генерацією переривань, коли таймер-лічильник зафіксує вказаний період

- дозволити роботу переривань

- при написати обробник переривань від таймера

- у симуляторі переконатися, що період між подіями справді становить вказану величину (2 мс по замовчуванню)54

Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

Переривання (Interrupt – англ.) – це сигнал, що повідомляє процесор про настання якої-небудь події. При цьому виконання поточної послідовності команд призупиняється і керування передається обробнику переривання, який реагує на подію та обслуговує її, після чого повертає управління в перерваний код.

Залежно від джерела виникнення сигналу переривання поділяються на:

Асинхронні або зовнішні (апаратні) — події, які створені зовнішніми джерелами (наприклад, периферійними пристроями) та можуть відбутися в довільний момент, наприклад, сигнал від таймера;

Синхронні або внутрішні — події в самому процесорі як результат порушення якихось умов при виконанні машинного коду: поділ на нуль або переповнення, звернення до неприпустимих адрес або неприпустимий код операції;

Програмні (частковий випадок внутрішнього переривання) — ініціюються виконанням спеціальної інструкції в коді програми. Програмні переривання, як правило використовуються для звернення до функцій вбудованого програмного забезпечення (firmware), драйверів й операційної системи.

Маскування переривань

Залежно від можливості заборони зовнішні переривання поділяються на:

ті, що можна маскувати — переривання, які можна забороняти установкою відповідних бітів у регістрі маскування переривань

ті, що не можна маскувати (англ. Non maskable interrupt, NMI) — обробляються завжди, незалежно від заборон на інші переривання.

Обробники переривань зазвичай пишуться таким чином, щоб час їх обробки був якомога меншим, оскільки під час їх роботи можуть не оброблятися інші переривання, а якщо їх буде багато (особливо від одного джерела), то вони можуть губитися.

Вектор переривання — закріплений за джерелом переривання номер, який ідентифікує відповідний обробник переривань. Вектори переривань об'єднуються в таблицю векторів переривань, що містить адреси обробників переривань. Розташування таблиці залежить від типу та режиму роботи процесора.

Пріоритет переривань вказує яке переривання відбудеться першим (або чи обробник текучого переривання буде перерваним іншим перериванням) за умови перебування обох (обо більше) у черзі на обробку. зазвичай пріоритет переривань визначається номером і по його порядковому номеру визначається яке переривання є більш чи менш пріоритетним.

Вкладеність переривань – дозвіл більш пріоритетному перериванню переривами обробник переривань менш пріоритетного переривання.

AVR мікроконтролери володіють модулем переривань, який дозволяє мікроконтролеру реагувати на асинхронні зовнішні чи внутрішні події.

Гнучкий модуль переривань містить свої керуючі регістри в просторі вводу-виводу і має додатковий біт загального дозволу роботи системи переривань у регістрі статусу (I-біт). У всіх переривань є свій вектор переривання відповідно до таблиці векторів переривань. Переривання мають пріоритет відповідно до позиції їх вектора. Переривання з меншою адресою переривання мають більш високий пріоритет.

Скидання й обробка переривань

AVR-мікроконтролери підтримують декілька різних джерел переривань. Всі переривання, а також скидання мають свій індивідуальний вектор в пам'яті програм. Для кожного переривання є власний біт дозволу. Крім того, є можливість загального дозволу роботи переривань за допомогою управління відповідним бітом в регістрі статусу (I-біт).

Найменші адреси в пам'яті програм за замовчуванням визначені як вектора переривань. Менші адреси володіють більш високим рівнем пріоритету.

Після виникнення переривання біт I загального дозволу переривань апаратно скидається і всі переривання забороняються. Користувач може програмно записати лог. 1 в біт I для дозволу вкладених переривань. В цьому випадку всі дозволені переривання можуть перервати поточну процедуру обробки переривань. Біт I автоматично встановлюється після виконання інструкції виходу з переривання RETI.

Є два основних типи переривань. Перший тип переривань активізується подією, яка призводить до встановлення мітки переривань. Для даних переривань програмний лічильник змінюється на відповідний вектор переривання для виконання процедури його обробки і потім апаратно очищає мітку переривання. Мітки переривання також скидаються шляхом запису лог.1 до відповідного розряду. Якщо виникає умова переривання, але дане переривання заборонено, то мітка встановлюється і запам'ятовується до дозволу цього переривання або скидається програмно. Аналогічно, якщо виникає одне і більше умов переривань при скинутій мітці загального дозволу переривань, то відповідна мітка встановлюється і запам'ятовується до відновлення роботи переривань, а потім переривання будуть виконані у відповідності з пріоритетом.

Другий тип переривань активізується відразу після виконання умови переривання. Дані переривання не обов'язково мають мітки переривань. Якщо умова переривання зникає до його дозволу, то даний запит ігнорується.

Після виходу з переривання AVR-мікроконтроллер повертається до виконання основної програми.

Зверніть увагу, що регістр статусу автоматично не запам'ятовується при виклику процедури обробки переривання і не відновлюється при виході з цієї процедури. Дані дії необхідно виконати програмно.

Приклад обробника переривань у Асамблелі з запам’ятовуванням регістру статусу

/*Збереження регістру статусу у стек*/

in r16, SREG

push r16

…

корисні дії обробника переривань

…

/*Відновлення регістру статусу із стеку*/

pop r16

out SREG, r16

/*Вихід з обробника переривань і перехід на програму, виконання якої було перерване*/

reti

При виконанні інструкції CLI всі переривання забороняються. Запит на переривання не буде відпрацьований після виконання інструкції CLI, навіть якщо воно виникає одночасно з виконанням команди CLI.

Для дозволу переривань використовується інструкція SEI, а наступна за SEI інструкція буде виконана перед відпрацюванням будь-якого відкладеного переривання.

Час реакції на переривання

Реакція на відпрацювання запиту на переривання триває мінімум 4 машинних цикли. Після закінчення цього часу програма продовжує своє виконання з вектора відповідного переривання. Протягом 4 машинних циклів стан програмного лічильника поміщається в стек. Як правило, за адресою вектора переривань зберігається команда переходу на процедуру обробку переривань, а на даний перехід витрачається ще 3 машинних цикли. Якщо запит на переривання виникає в процесі виконання інструкції, що вимагає більш 1 машинних цикли на виконання, то переривання буде оброблено тільки після виконання цієї інструкції. Якщо переривання виникає під час перебування мікроконтролера в режимі сну (SLEEP MODE), то реакція на переривання збільшиться ще на 4 цикли. Дана затримка пов'язана з часом старту з обраного режиму сну.

Вихід з процедури обробки переривання вимагає 4 машинних цикли. Протягом цього часу двобайтовий програмний лічильник витягується з стека, покажчик стека двічі інкрементується і встановлюється біт I в регістрі статусу SREG.

Таблиця векторів переривань для мікроконтролера ATMEGA128

N вектора |

Адреса пам'яті програм |

Джерело |

Умова виникнення переривання |

1 |

$0000 |

Скидання (RESET) |

Зовнішнє скидання, скидання при подачі живлення, скидання при неприпустимому зниженні живлення, скидання сторожовим таймером і скидання через JTAG-інтерфейс |

2 |

$0002 |

IINT0 |

Запит на зовнішнє переривання 0 |

3 |

$0004 |

INT1 |

Запит на зовнішнє переривання 1 |

4 |

$0006 |

INT2 |

Запит на зовнішнє переривання 2 |

5 |

$0008 |

INT3 |

Запит на зовнішнє переривання 3 |

6 |

$000A |

INT4 |

Запит на зовнішнє переривання 4 |

7 |

$000C |

INT5 |

Запит на зовнішнє переривання 5 |

8 |

$000E |

INT6 |

Запит на зовнішнє переривання 6 |

9 |

$0010 |

INT7 |

Запит на зовнішнє переривання 7 |

10 |

$0012 |

TIMER2 COMP |

Спрацювання компаратора таймера-лічильника 2 |

11 |

$0014 |

TIMER2 OVF |

Переповнення таймера-лічильника 2 |

12 |

$0016 |

Timer1 CAPT |

Захоплення фронту таймером-лічильником 1 |

13 |

$0018 |

Timer1 COMPA |

Спрацювання компаратора А таймера-лічильника 1 |

14 |

$001A |

Timer1 COMPB |

Спрацювання компаратора В таймера-лічильника 1 |

15 |

$001C |

Timer1 OVF |

Переповнення таймера-лічильника 1 |

16 |

$001E |

TIMER0 COMP |

Спрацювання компаратора таймера-лічильника 0 |

17 |

$0020 |

TIMER0 OVF |

Переповнення таймера-лічильника 0 |

18 |

$0022 |

SPI, STC |

Завершення послідовної передачі інтерфейсом SPI |

19 |

$0024 |

USART0, RX |

Завершення прийому УСАПП 0 |

20 |

$0026 |

USART0, UDRE |

Регістр даних УСАПП0 вільний |

21 |

$0028 |

USART0, TX |

Завершення передачі УСАПП 0 |

22 |

$002A |

АЦП |

Завершення перетворення АЦП |

23 |

$002C |

EE READY |

Готовність ЕСППЗУ |

24 |

$002E |

ANALOG COMP |

Аналоговий компаратор |

25 |

$0030 |

TIMER1 COMPC |

Спрацювання компаратора З таймера-лічильника 1 |

26 |

$0032 |

TIMER3 CAPT |

Захоплення фронту таймером лічильником 3 |

27 |

$0034 |

TIMER3 COMPA |

Спрацювання компаратора А таймера-лічильника 3 |

28 |

$0036 |

TIMER3 COMPB |

Спрацювання компаратора В таймера-лічильника 3 |

29 |

$0038 |

TIMER3 COMPC |

Спрацювання компаратора З таймера-лічильника 3 |

30 |

$003A |

TIMER3 OVF |

Переповнення таймера лічильника 3 |

31 |

$003C |

USART1, RX |

Завершення прийому УСАПП 1 |

32 |

$003E |

SART1, UDRE |

УСАПП1 вільний |

33 |

$0040 |

USART1, TX |

Завершення передачі УСАПП1 |

34 |

$0042 |

TWI |

Двопровідний послідовний інтерфейс |

35 |

$0044 |

SPM READY |

Готовність запису в пам'ять програм |

У таблиці 24 показано розташування векторів скидання і переривань в залежності від різних установок BOOTRST і IVSEL. Якщо програма не використовує переривання, то вона може бути розміщена рівномірно, використовуючи комірки з адресами векторів переривань для зберігання програмного коду. Можливий також випадок, коли вектор скидання розташовується в секторі прикладної програми, а вектори переривань - в завантажувальному секторі або навпаки.

Таблиця розміщення векторів скидання і переривань

BOOTRST |

IVSEL |

Адреса скидання |

Початкова адресу векторів переривань |

1 |

0 |

$0000 |

$0002 |

1 |

1 |

$0000 |

Адреса скидання в завантажувальному секторі + $0002 |

0 |

0 |

Адреса скидання в завантажувальному секторі |

$ 0002 |

0 |

1 |

Адреса скидання в завантажувальному секторі |

Адреса скидання в завантажувальному секторі + $0002 |

Нижче наведено більшість типових і спільних програмних установок адрес скидання і векторів переривань у ATmega128:

Адреса Інструкція Коментар

jmp RESET; Перехід на обробку скидання

jmp EXT_INT0; Перехід на обробку запиту IRQ0

jmp EXT_INT1; Перехід на обробку запиту IRQ1

jmp EXT_INT2; Перехід на обробку запиту IRQ2

jmp EXT_INT3; Перехід на обробку запиту IRQ3

jmp EXT_INT4; Перехід на обробку запиту IRQ4

jmp EXT_INT5; Перехід на обробку запиту IRQ5

jmp EXT_INT6; Перехід на обробку запиту IRQ6

jmp EXT_INT7; Перехід на обробку запиту IRQ7

jmp TIM2_COMP; Перехід на обробку при виконанні умови порівняння таймера 2

jmp TIM2_OVF; Перехід на обробку при переповненні таймера 2

jmp TIM1_CAPT; Перехід на обробку при захопленні фронту таймером 1

jmp TIM1_COMPA; Перехід на обробку при спрацьовуванні компаратора А таймера 1

jmp TIM1_COMPB; Перехід на обробку при спрацьовуванні компаратора В таймера 1

jmp TIM1_OVF; Перехід на обробку при переповненні таймера 1

jmp TIM0_COMP; Перехід на обробку при виконання умови порівняння таймера 0

jmp TIM0_OVF; Перехід на обробку при переповненні таймера 0

jmp SPI_STC; Перехід на обробку при завершенні передачі SPI

jmp USART0_RXC; Перехід на обробку при завершенні прийому УСАПП0

jmp USART0_DRE; Перехід на обробку при звільненні регістра даних UDR УСАПП0

jmp USART0_TXC; Перехід на обробку при завершенні передачі УСАПП0

jmp ADC; Перехід на обробку при завершенні перетворення АЦП

jmp EE_RDY; Перехід на обробку при готовності ЕСППЗУ

jmp ANA_COMP; Перехід на обробку при спрацьовуванні аналогового компаратора

jmp TIM1_COMPC; Перехід на обробку при спрацьовуванні компаратора З таймера 1

jmp TIM3_CAPT; Перехід на обробку при захопленні фронту таймером 3

jmp TIM3_COMPA; Перехід на обробку при спрацьовуванні компаратора А таймера 3

jmp TIM3_COMPB; Перехід на обробку при спрацьовуванні компаратора В таймера 3

jmp TIM3_COMPC; Перехід на обробку при спрацьовуванні компаратора З таймера 3

jmp TIM3_OVF; Перехід на обробку при переповненні таймера 3

jmp USART1_RXC; Перехід на обробку по завершенні прийому УСАПП1

jmp USART1_DRE; Перехід на обробку при звільненні регістра даних UDR УСАПП1

jmp USART1_TXC; Перехід на обробку при завершенні передачі УСАПП1

jmp TWI; Перехід на обробку переривання по двопровідному послідовному інтерфейсу

jmp SPM_RDY; Перехід на обробку переривання при готовності виконання команди SPM

;

RESET:

ldir16, high (RAMEND); Початок основної програми

out SPH, r16; Установка покажчика стека в кінці ОЗУ

ldi r16, low (RAMEND)

out SPL, r16

sei; Дозвіл переривань

... ... ... ...

(!) Це може бути вам корисно

У випадку, коли використовуються тільки деякі переривання, але прийьому перехід на обробник переривань треба встановити у свій вектор переривань (наперед визначену комірку), то зручно використати такий шаблон:

/**********************************************************************************/

jmp RESET; Перехід на обробку скидання

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp TIM0_COMP; Перехід на обробку при виконання умови порівняння таймера 0

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

jmp NO_INT

;

RESET:

ldir16, high (RAMEND); Початок основної програми

out SPH, r16; Установка покажчика стека в кінці ОЗУ

ldi r16, low (RAMEND)

out SPL, r16

sei; Дозвіл переривань

... ... ... ...

CONTINUE:

... ... ... ...

jmp CONTINUE

/*Обробник неіснуючого переривання*/

NO_INT: reti

/*Обробник переривання від таймеру-лічильнику 0 при досягненні умови порівняння*/

TIM0_COMP:

in r16, SREG

push r16

…

корисні дії обробника переривань

…

/*Відновлення регістру статусу із стеку*/

pop r16

out SREG, r16

/*Вихід з обробника переривань і перехід на програму, виконання якої було перерване*/

reti

... ... ... ...

/**********************************************************************************/

Загальний регістр управління перериваннями задає розміщення таблиці векторів переривань.

Регістр управління микроконтроллером - MCUCR

-

Розряд

7

6

5

4

3

2

1

0

SRE

SRW10

SE

SM1

SM0

SM2

IVSEL

IVCE

MCUCR

Читання/запис

Чт/Зп.

Чт/Зп.

Чт/Зп.

Чт/Зп.

Чт/Зп.

Чт/Зп.

Чт/Зп.

Чт/Зп.

Вих. значення

0

0

0

0

0

0

0

0

Розряд 1 - IVSEL: Вибір вектора переривання

Якщо біт скинутий IVSEL (= 0), то вектори переривань розміщуються на початку флеш-пам'яті. Якщо даний біт встановлений (= 1), то вектори переривань переміщуються в початок завантажувального сектора флеш-пам'яті. Фактична адреса початку завантажувального сектора визначається значенням конфігураційних біт BOOTSZ. Щоб уникнути несанкціонованих змін таблиці векторів переривань необхідно виконати спеціальну послідовність запису при зміні біта IVSEL:

Записати лог. 1 в біт дозволу зміни вектора переривання (IVCE).

Протягом чотирьох машинних циклів записати бажане значення в IVSEL, при цьому записуючи лог.0 в IVCE.

Переривання будуть автоматично відключені при виконанні такої послідовності. Переривання відключаються під час установки IVCE і залишаться відключеними до переходу до інструкції наступного за інструкцією записи в IVSEL. Якщо IVSEL не записаний, то переривання буде знаходитися у відключеному стані 4 такти синхронізації. Стан біта I в регістрі статусу не зачіпається при автоматичному відключенні переривань.

Наприклад: Якщо вектори переривань поміщаються в завантажувальний сектор і біт захисту завантажувального сектора BLB02 запрограмований, то переривання будуть відключені при виконанні програми з секторі прикладної програми. Якщо вектори переривань розміщені в прикладному секторі і біт захисту BLB12 запрограмований, то переривання стають відключеними при виконанні програми в завантажувальному секторі.

Розряд 0 - IVCE: Дозвіл зміни вектора переривання

В біт IVCE повинно бути записано лог. 1, щоб дозволити зміну біта IVSEL. IVCE скидається апаратно через чотири машинних циклу після запису лог. 1 в IVSEL. Установка біта IVCE призведе до відключення переривань, що описано при розгляді біта IVSEL вище.

Опис деяких мнемонік інструкцій, які використовуються у цій лабораторній роботі і не були описані у описах до попередніх лабораторних робіт

JMP – «Перехід»

Інструкція здійснює перехід у межах 4 МЕГА слів простору пам’яті програм..

PC ← k

Синтаксис |

Операнди |

Лічильник команд |

Стек |

JMP k |

-0 ≤ k ≤ 4М |

PC ← k |

Без змін |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

- |

- |

- |

- |

- |

- |

- |

- |

Наприклад:

jmp OK

OK: nop

RETI – «Вихід з переривання»

Інструкція здійснює вихід з поривання. Адреса повернення вигружається зі стеку і біт Глобальний дозвіл переривань (I-біт) встановлюється.

Зверніть увагу на те, що регістр статусу автоматично не записується при вході в обробник переривань і не відновлюється при виході з переривання. Ці операції треба виконати програмно. Вказівник на стек використовує преінкрементації під час виконання інструкції RETI

PC(15:0) ← STACK

Синтаксис |

Операнди |

Лічильник команд |

Стек |

RETI |

Нема |

PC(15:0) ← STACK |

SP ← SP + 2 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

1 |

- |

- |

- |

- |

- |

- |

- |

Біт I:

Встановлюється завжди.

Наприклад:

exit_int:

pop r16

out SREG r16

reti

CLI – «Скидання біту глобального дозволу переривань»

Інструкція здійснює очистку біту Глобального дозволу переривань (I-біт) у регістру статусу (SREG). Генерація всіх переривань буде забороненою. Переривання не будуть генеруватися після цієї інструкції навіть якщо умова їх генерації виникне одночасно з виконанням цієї інструкції.

I ← 0

Синтаксис |

Операнди |

Стек |

CLI |

Нема |

SP ← SP + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

0 |

- |

- |

- |

- |

- |

- |

- |

Біт I:

Очищається завжди.

Наприклад:

cli

SEI – «Встановлення біту глобального дозволу переривань»

Інструкція здійснює встановлення біту Глобального дозволу переривань (I-біт) у регістру статусу (SREG). Наступна інструкція після цієї інструкції буде виконана перед будь-якими перериваннями які очікують на обробку

I ← 1

Синтаксис |

Операнди |

Стек |

SEI |

Нема |

SP ← SP + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

1 |

- |

- |

- |

- |

- |

- |

- |

Біт I:

Встановлюється завжди.

Наприклад:

sei