- •1 Загальні відомості

- •6 Відладка програми

- •7 Налаштування параметрів імітатора

- •ATmega128, aTmega128l 8-розрядний avr-мікроконтролер з внутрішньосистемною програмованою флеш-пам'яттю ємністю 128 кбайт Особливості:

- •Короткий огляд

- •Завдання:

- •Лабораторна робота №2 «Вивчення математичних і логічних операцій і їх вплив на біти-стану мікроконтролера» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №3 «Вивчення методів додавання і віднімання чотирьохбайтних чисел» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Лабораторна робота №5 «Вивчення роботи з пам’яттю даних» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №6 «Вивчення операцій порівняння і реалізація циклічних операцій» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Завдання:

- •Часові діаграми таймера-лічильника 0

- •Опис регістрів 8-розрядного таймера-лічильника 0

- •Асинхронна робота таймера-лічильника 0

- •Дільник частоти таймера-лічильника 0 Дільник частоти таймер-лічильника 0

- •Завдання:

- •Завдання:

- •Набір інструкцій

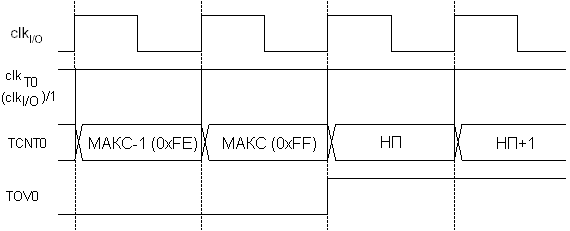

Часові діаграми таймера-лічильника 0

На рисунку часової діаграма роботи таймер-лічильника 0 без дільника частоти тактовий сигнал таймера (clkT0) показаний як сигнал дозволу синхронізації. Рахункова послідовність показана в області максимального значення лічильника (0xFF). На наступних рисунках показані аналогічні тимчасові діаграми, але з дозволеним дільником частоти тактового сигналу.

Представлені діаграми відповідають синхронному по відношенню до системної частоти режиму тактування таймера-лічильника. Однак, вони будуть повністю відповідати асинхронному режиму роботи, якщо замінити clkI/O на сигнал генератора таймера-лічильника.

Часова

діаграма таймера-лічильника без дільника

частоти

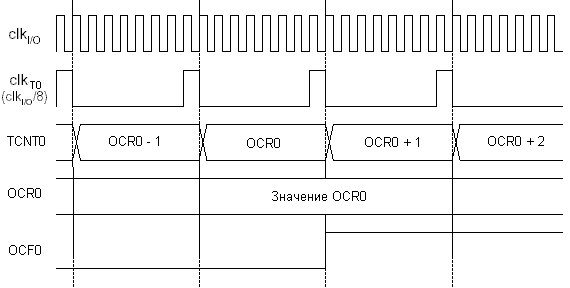

Часова

діаграма таймера-лічильника без дільника

частоти

(fclk_I/O/8)

Часова діаграма таймера-лічильника з

дільником частоти на 8 (fclk_I/O/8)

(fclk_I/O/8)

Часова діаграма таймера-лічильника з

дільником частоти на 8 (fclk_I/O/8)

Часова

діаграма таймера-лічильника з установкою

мітка OCF0 і дільником частоти 8 (fclk_I/O/8)

Часова

діаграма таймера-лічильника з установкою

мітка OCF0 і дільником частоти 8 (fclk_I/O/8)

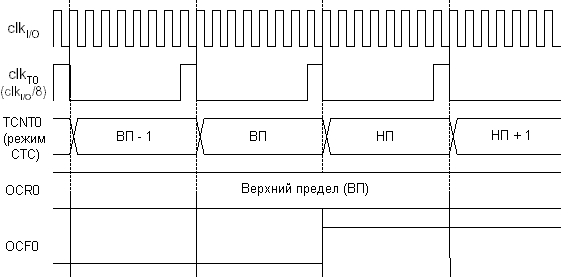

Часова

діаграма таймер-лічильника з дільником

частоти 8 (fclk_I/O/8) в режимі скидання при

збігу

Часова

діаграма таймер-лічильника з дільником

частоти 8 (fclk_I/O/8) в режимі скидання при

збігу

Опис регістрів 8-розрядного таймера-лічильника 0

Регістр управління таймером-лічильником 0 - TCCR0

Розряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

FOC0 |

WGM00 |

COM01 |

COM00 |

WGM01 |

CS02 |

CS01 |

CS00 |

TCCR0 |

Читання/запис |

Чт |

Чт/Зп. |

Чт/Зп |

Чт/Зп |

Чт/Зп |

Чт/Зп |

Чт/Зп |

Чт/Зп |

|

Поч. значення |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Розряд 7 - FOC0: Примусова установка результату порівняння

Функція біта FOC0 активна тільки, якщо за допомогою біт WGM заданий один з режимів, де немає широтно-імпульсної модуляції. Однак з метою сумісності з наступними мікроконтролерами рекомендується під час запису в регістр TCCR0 в позиції даного біта вказувати лог., якщо таймер працює в одному з режимів з широтно-імпульсною модуляцією. Якщо записати лог. 1 в біт FOC0, то це призводить до примусової установки результату порівняння на вході блоку формування вихідного сигналу. Отже, значення записане в COM01, COM00 визначає ефект дії примусової установки результату порівняння. Зверніть також увагу, що біт FOC0 є стробуючим.

Строб FOC0 не генерує жодних переривань, а також не викликає скидання таймера в режимі СТС, де регістр OCR0 задає верхню межу лічби.

Біт FOC0 завжди зчитується як 0.

Розряди 6, 3 - WGM01: 0: Режим роботи таймера-лічильника 0

Дані біти визначають алгоритм лічби лічильника, джерело, яке задає верхню межу рахунку та тип генеруються прямокутних імпульсів. Даним таймером підтримуються наступні режими роботи: нормальний режим, режим скиду при збігу і два режими з широтно-імпульсною модуляцією. У таблиці представлені режими роботи таймера-лічильника 0

Опис біт, які задають режим роботи таймера-лічильника 0

Номер режиму |

WGM01 |

WGM00 |

Найменування режиму роботи таймера-лічильника 0 |

Верхня межа лічби |

Умова оновлення вмісту регістра OCR0 |

Умова установки мітки TOV0 |

0 |

0 |

0 |

Нормальний |

0xFF |

Відразу після запису в регістр |

Досягнення максимального значення (0xFF) |

1 |

0 |

1 |

ШІМ з фазовою корекцією |

0xFF |

Досягнення верхньої межі лічби |

Досягнення мінімального значення (0x00) |

2 |

1 |

0 |

Скидання при збігу (CTC) |

OCR0 |

Відразу після запису в регістр |

Досягнення максимального значення (0xFF) |

3 |

1 |

1 |

Швидка ШІМ |

0xFF |

Досягнення верхньої межі лічби |

Досягнення максимального значення (0xFF) |

Розряди 5:4 - COM01, COM00: Режим формування вихідного сигналу

Дані біти визначають алгоритм зміни сигналу на виводі OC0. Якщо значення даних біт ненульове, то функція виводу OC0 як звичайного порту вводу-виводу замінюється на альтернативну. Однак, слід враховувати, що напрямок цього виводу також управляється через регістр напрямку даних порту В (DDRB). Тому, для дозволу альтернативної функції виводу OC0 також необхідно встановити біт 4 (OC0) в регістрі DDRB для установки вихідного напряму.

Після активізації альтернативної функції призначення біт COM01, COM00 залежить від обраного режиму роботи таймера бітами WGM01, WGM00У таблиці 53 приведено призначення біт COM01, COM00, якщо за допомогою WGM01, WGM00 заданий нормальний режим або режим скидання при збігу (тобто режими без ШІМ).

Таблиця Режими формування вихідного сигналу в режимах роботи таймера 0 без ШІМ

COM01 |

COM00 |

Опис |

0 |

0 |

Функція звичайного порту вводу-виводу. OC0 відключений. |

0 |

1 |

Перемикання (інвертування) OC0 при кожному збігу |

1 |

0 |

Скидання OC0 при кожному збігу |

1 |

1 |

Установка OC0 при кожному збігу |

У таблиці наступній таблиці наведено призначення біт COM01, COM00 для режиму роботи таймера-лічильника 0 з швидкою ШІМ (WGM01: 0).

Зазначення цих бітів для режимів з ШІМ дивіться у опис даного мікроконтролера

Розряди 2:0 - CS02: 0: Настройка частоти синхронізації таймера

За допомогою трьох настроювальних біт є можливість вибрати різні тактові частоти, кратні вхідній частоті синхронізації

Таблиця вибору частоти синхронізації таймера 0

CS02 |

CS01 |

CS00 |

Опис |

0 |

0 |

0 |

Немає синхронізації. Таймер-лічильник 0 зупинений. |

0 |

0 |

1 |

clkT0S/1 (без ділення частоти) |

0 |

1 |

0 |

clkT0S/8 (з діленням частоти) |

0 |

1 |

1 |

clkT0S/32 (з діленням частоти) |

1 |

0 |

0 |

clkT0S/64 (з діленням частоти) |

1 |

0 |

1 |

clkT0S/128 (з діленням частоти) |

1 |

1 |

0 |

clkT0S/256 (з діленням частоти) |

1 |

1 |

1 |

clkT0S/1024 (з діленням частоти) |

Регістр таймера-лічильника - TCNT0

Розряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

TCNT0[7:0] |

TCNT0 |

|||||||

Читання/запис |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

|

Поч. значення |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Регістр таймера-лічильника характеризується двоспрямованістю доступу до 8-розрядному лічильнику таймера 0. Зміна вмісту лічильника (TCNT0) під час лічби пов'язано з ризиком втрати результату порівняння між TCNT0 і регістром OCR0.

Регістр порогу порівняння - OCR0

Розряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

OCR0[7:0] |

OCR0 |

|||||||

Читання/запис |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

Чт./Зп. |

|

Поч. значення |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

Регістр порогу порівняння містить 8-розр. значення, яке безперервно порівнюється цифровим компаратором зі значенням 8-розр. лічильника (TCNT0). Факт збігу значень може використовуватися для генерації переривання по виконанню умови порівняння або для генерації прямокутних імпульсів на виводі OC0.