- •1 Загальні відомості

- •6 Відладка програми

- •7 Налаштування параметрів імітатора

- •ATmega128, aTmega128l 8-розрядний avr-мікроконтролер з внутрішньосистемною програмованою флеш-пам'яттю ємністю 128 кбайт Особливості:

- •Короткий огляд

- •Завдання:

- •Лабораторна робота №2 «Вивчення математичних і логічних операцій і їх вплив на біти-стану мікроконтролера» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №3 «Вивчення методів додавання і віднімання чотирьохбайтних чисел» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Лабораторна робота №5 «Вивчення роботи з пам’яттю даних» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №6 «Вивчення операцій порівняння і реалізація циклічних операцій» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Завдання:

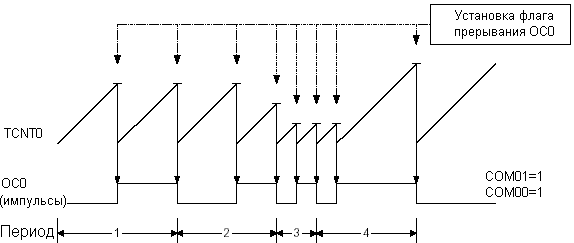

- •Часові діаграми таймера-лічильника 0

- •Опис регістрів 8-розрядного таймера-лічильника 0

- •Асинхронна робота таймера-лічильника 0

- •Дільник частоти таймера-лічильника 0 Дільник частоти таймер-лічильника 0

- •Завдання:

- •Завдання:

- •Набір інструкцій

Завдання:

1. Встановити PORTA (всі вісім ліній вводу-виводу даного порту) на ввід (стан підтягуючого резистора для симулятора не має значення)

2. Встановити PORTB (всі вісім ліній вводу-виводу даного порту) на ввід (стан підтягуючого резистора для симулятора не має значення)

3. Встановити PORTC (всі вісім ліній вводу-виводу даного порту) на вивід (початковий стан: лог. 0)

4. Встановити PORTD (всі вісім ліній вводу-виводу даного порту) на вивід (початковий стан: лог. 0)

5. Реалізувати безперервний цикл

5.1 Зчитує стан PORTA (всі вісім ліній вводу-виводу даного порту відразу) у регістр

5.2 Зчитує стан PORTB (всі вісім ліній вводу-виводу даного порту відразу) у регістр

5.3 Перемножити ці регістри між собою методом без знакової арифметики

5.4 Вивести молодший байт результату множення на PORTC (всі вісім ліній вводу-виводу даного порту відразу)

5.5 Вивести молодший байт результату множення на PORTD (всі вісім ліній вводу-виводу даного порту відразу)

6. Встановлювати різні значення у Симуляторі з допомогою вікна «Перегляд регістрів вводу-виводу» (“I/O View” Alt-5) і спостерігати за правильною роботою програми.

Лабораторна робота №9 «Вивчення програмування таймера мікроконтролера AVR»

Ціль роботи

вивчити принципів роботи з таймерами AVR мікроконтролера

закріпити знання попередніх лабораторних роботах

Програма виконання роботи

- проініціалізувати таймер на фіксацію проміжку часу у 2 мс (період можна змінити)

- при фіксації вказаного періоду роботи скидати програмно цю подію

- у симуляторі переконатися , що період між подіями справді становить вказану величину (2 мс по замовчуванню)

Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

До складу периферії мікроконтролера ATMEGA128 входять:

- Два 8-ми розрядні таймери-лічильники з розділеними дільниками частоти і режимами порівняння

- Два розширені 16-ти розрядні таймери з окремими дільниками частоти і режимами захоплення

- Лічильник реального часу з окремим генератором

8-розрядний таймер-лічильник 0 з функціями широтно-імпульсної модуляції і асинхронного тактування

Таймер-лічильник 0 - модуль багатофункціонального одноканального 8-розрядного таймера-лічильника з апаратним виходом для генерації ШІМ-сигналу і вбудованим асинхронним опціональним тактовим генератором, який оптимізований під використання часового кварцу (32768Гц) для асинхронного по відношенню до системної синхронізації тактування.

Основні властивості:

- одноканальний лічильник

- Режим скидання таймера при успішному порівнянні (автоматичне перезавантаження)

- Широтно-імпульсна модуляція без генерації помилкових імпульсів при записі нового порогу порівняння в OCR0 (подвійна буферизація) і з фазовою корекцією

- генератор частоти

- 10-розрядний дільник частоти

- Генерація переривань про переповненні та виконання умови порівняння (TOV0 і OCF0)

Можливість асинхронного тактування спільно із зовнішнім кварцовим резонатором частотою 32 кГц незалежно від частоти синхронізації вводу-виводу.

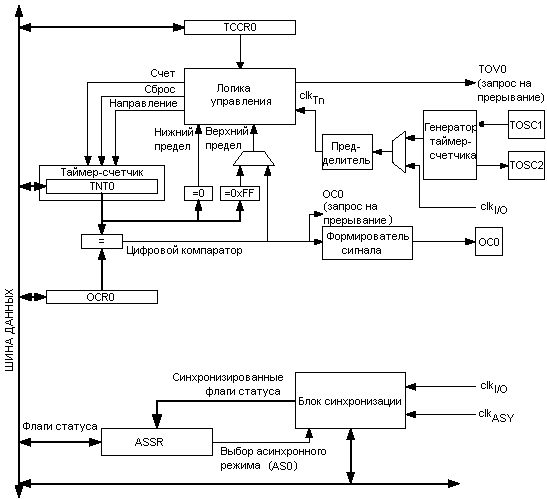

Короткий огляд

Функціональна схема 8-розр. таймера-лічильника представлена на рисунку нижче. Зв'язки з регістрами, до яких здійснює доступ ЦПУ, в т.ч. біти вводу-виводу і лінії вводу-виводу показані жирною лінією.

Регістри (з області вводу-виводу)

Регістр таймера-лічильника (TCNT0) і регістр порогу порівняння (OCR0) - 8-розр. регістри. Сигнали запиту на переривання представлені як мітки переривань таймера в регістрі TIFR. Всі переривання індивідуально маскуються за допомогою регістра маски переривань таймерів (TIMSK). Регістри TIFR і TIMSK не представлені на функціональній схемі, тому що вони спільно використовуються з іншими таймерами мікроконтролера.

Таймер-лічильник може тактуватися через дільник частоти внутрішньо або асинхронно через зовнішні виходи TOSC1/2. Асинхронна робота управляється регістром асинхронного стану (ASSR). Блок синхронізації здійснює вибір, яке тактове джерело використовується для інкрементування (декрементування) стану таймера-лічильника. Якщо джерело тактування не задане, то таймер-лічильник знаходиться в неактивному стані. Вихід логіки вибору синхронізації позначений як синхронізація таймера (clkT0).

Значення регістра порога порівняння з подвійною буферизацією (OCR0) безперервно порівнюється зі значенням таймера-лічильника. Результат порівняння може використовуватися для генерації сигналів з ШІМ або прямокутних імпульсів змінної частоти на виводі OC0. Збіг порога порівняння зі значенням таймера-лічильника призводить до встановлення мітки результату порівняння (OCF0), який може використовуватися для генерації запиту на переривання по результату порівняння.

Визначення

Деякі визначення та їх скорочені найменування, які інтенсивно використовуються в цьому розділі, представлені в таблиці

Таблиця визначень

НМ (нижня межа) |

Лічильник досягає нульового значення (0х00) |

МАКС (максимальне значення) |

Лічильник досягає максимального значення 0xFF (десяткове 255) |

ВМ (верхня межа) |

Лічильник досягає верхньої межі лічби (вершина лічби). Як вершини рахунку може виступати фіксоване значення 0xFF або вміст регістра OCR0. |

Тактові джерела таймера-лічильника 0

Таймер-лічильник 0 може тактуватися внутрішньо синхронно або зовні асинхронно (по відношенню до внутрішньої системної синхронізації). По замовчуванню використовується тактовий сигнал clkT0, еквівалентний тактовому сигналу мікроконтролера clkI/O. Якщо в біт AS0 регістра ASSR записати лог.1 то в якості джерела синхронізації виступає генератор таймера-лічильника, зв’язаний з виводами підключення низькочастотного кварцового резонатора TOSC1 і TOSC2.

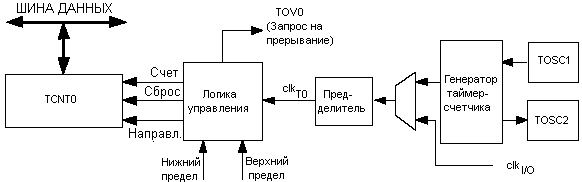

Блок лічби

Основу 8-розр. таймера-лічильника 0 складає програмований двонаправлений лічильник. Рисунок показує функціональну схему лічильника і оточуючих його елементів.

Опис сигналів (внутрішні сигнали):

«Счет» - інкрементується або декрементується TCNT0 на 1.

«Направл.» - Задає напрям лічби: інкрементування (+1, пряма лічба) або декрементування (-1, зворотнаа лічба).

«Сброс» - Скидає вміст TCNT0 (запис лог. 0 в усі розряди).

clkT0 - Синхронізація таймера-лічильника.

«Верхний предел» - Визначає максимальне значення, яке може досягти TCNT0.

«Нижний предел» - Задає мінімальне значення, яке може досягти TCNT0 (нуль).

В залежності від обраного режиму роботи лічильник скидається, інкрементується або декрементується на кожному такті синхронізації (clkT0). Тактовий сигнал clkT0 може бути внутрішнім або зовнішнім, а його частота вибирається за допомогою біт вибору частоти синхронізації CS02-CS00. Якщо джерело синхронізації не задане (CS02-CS00 = 0b000), то таймер зупиняється. Проте стан TCNT0 доступне CPU незалежно від того працює синхронізація таймера чи ні. Запис в регістр таймера через CPU перекриває будь-які дії самого лічильника: скидання або лічбу, тобто має більш високий пріоритет.

Послідовність рахунку визначається установкою біт WGM01 і WGM00, розташованих в регістрі управління таймером-лічильником (TCCR0). Є точний зв'язок між поведінкою лічильника (алгоритмом рахунку) і генерованою на виході OC0 формою сигналу.

Мітка переповнення таймера-лічильника (TOV0) встановлюється відповідно до режиму роботи, який вибирається бітами WGM01, WGM00. Біт TOV0 може використовуватися для генерації переривання CPU.

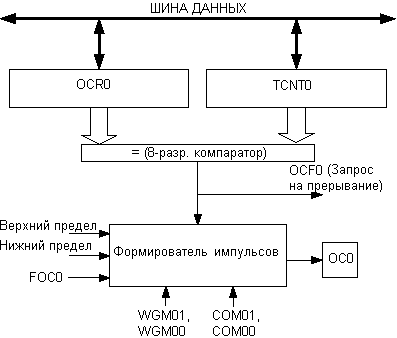

Блок порівняння

8-розрядний цифровий компаратор безперервно виконує порівняння вмісту регістра таймера-лічильника TCNT0 з регістром порогу порівняння OCR0. Кожного разу, коли значення TCNT0 збігається зі значенням OCR0 компаратор встановлює мітку збігу OCF0 наступним тактом синхронізації таймера. Якщо дозволено переривання бітом OCIE0 = 1, то установка мітки збігу викликає запит на переривання. Прапор OCF0 автоматично скидається під час виконання процедури обробки переривання. Альтернативно, прапор OCF0 можна скинути програмно шляхом запису лог. 1 в позицію даного биту. Генератор сигналу використовує сигнал результату порівняння для генерації прямокутних імпульсів по одному з алгоритмів, який вибирається бітами задання режиму роботи таймера WGM01, WGM00 і бітами задання режиму формування вихідного сигналу (COM01, COM00). Верхній і нижній межі дічби використовуються в деяких режимах роботи для виконання спеціальних дій. На рисунку наведена функціональна схема блоку порівняння.

Регістр OCR0 виконаний за схемою подвійної буферизації при використанні режимів з широтно-імпульсною модуляцією (ШІМ). У нормальному режимі і режимі скидання таймеру при збігу (CTC) схема подвійної буферизації відключається. Подвійна буферизація дозволяє синхронізувати оновлення регістра порівняння OCR0 по досягненні верхньої або нижньої межі лічби. Така синхронізація запобігає можливість виникнення несиметричних ШІМ-імпульсів непарної довжини, тим самим гарантуючи відсутність збоїв при генерації прямокутних імпульсів.

Після дозволу подвійної буферизації CPU здійснює доступ до буферного регістру OCR0, а після відключення - безпосередньо адресується до регістру OCR0.

Примусова установка результату порівняння

В режимах генерації імпульсів без ШІМ у формувачі імпульсів результат порівняння може бути встановлений безпосередньо через біт примусової установки результату порівняння FOC0. Примусова установка результату порівняння компаратора не призводить до встановлення мітки OCF0 або скидання/перезавантаження таймера, але впливає на стан виходу OC0, який буде встановлюватися, скидатися або перемикатися (інвертуватися) залежно від обраної установки біт COM01, COM00.

Результат порівняння блокується записом в TCNT0

Якщо CPU здійснює запис в регістр TCNT0, то результат порівняння буде ігноруватися на наступному такті синхронізації таймера, навіть якщо таймер зупинений. Ця функція дозволяє встановити в регістрі OCR0 те ж значення, що і в TCNT0 без генерації запиту на переривання, якщо дозволено тактування таймера-лічильника.

Використання блоку порівняння

Оскільки запис в TCNT0 блокує будь-які дії по результату порівняння на один такт синхронізації таймера незалежно від режиму роботи, то при зміні TCNT0 при використанні каналу порівняння (незалежно працює синхронізація таймера чи ні) необхідно врахувати такі особливості. Якщо в регістр TCNT0 записано значення рівне OCR0, то ігнорування збігу призведе до генерації некоректною форми сигналу. За аналогією слід уникати записи в TCNT0 значення рівного нижньої межі (0x00), якщо лічильник працює як віднімаючий.

Установка OC0 повинна бути виконана перед налаштуванням лінії вводу-виводу на вивід в регістрі напрямки даних. Найлегший шлях установки значення OC0 - використання біта примусової установки результату порівняння (FOC0) в нормальному режимі. Регістр OC0 зберігає його значення, навіть якщо відбувається зміна режиму роботи таймера.

Врахуйте, що біти COM01, COM00 не містять схеми подвійної буферизації і на будь-які зміни реагують миттєво.

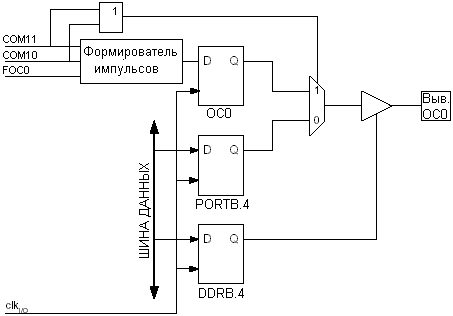

Блок формування вихідного сигналу

Біти завдання режиму формування вихідного сигналу (COM01: 0) мають подвійне призначення. З одного боку біти COM01, COM00 використовуються формувачем сигналу і визначають який логічний стан повинен бути на виході OC0 при виникненні наступного збігу. З іншого боку, біти COM01, COM00 використовуються для дозволу/заборони альтернативної функції виходу порту OC0. На рисунку представлена спрощена логічна схема, на яку впливають біти COM01, COM00. На малюнку показані тільки ті регістри управління портом вводу-виводу (DDR і PORT), на які впливають біти COM01, COM00.

Функція лінії універсального порту вводу-виводу замінюється на функцію виходу формувача сигналу OC0, якщо хоча б один з біт COM01, COM00 встановлений (логіка АБО). Однак, управлінням напрямку виводу OC0 (вхід або вихід) в цьому випадку залишається за відповідним бітом регістра напрямку даних порту В (DDRB.4). Щоб значення регістра OC0 передавалося на вихід OC0 необхідно налаштувати дану лінію на вивід (встановити біт DDRB.4). Управління вводом альтернативної функції не залежить від режиму генерації сигналу.

Схемотехніка вихідної логіки дозволяє ініціалізувати стан регістра OC0 перед дозволом налаштування виводу OC0 в якості виходу. Зверніть увагу, що в деяких режимах роботах є зарезервовані стану біт COM01, COM00.

Режими генерації сигналу

Значення біт COM01: 0 задає різні режими формування вихідного сигналу, які в свою чергу залежать від обраного режиму роботи таймера. Таймер-лічильник 0 може бути переведений в нормальний режим, в режим скидання таймера при збігу або в один з режимів з генерацією ШІМ-сигналів. Загальним для всіх режимів є невиконання будь-яких дій з виводом OC0 при виконанні умови порівняння, якщо обидва біта COM01, COM00 дорівнюють нулю.

Після установки біт COM01, COM00 вони вступають в силу тільки після першого збігу який слідує за цією установкою. Для режимів без ШІМ установки можуть бути негайно активізовані за допомогою стробуючого біту FOC0.

Режими роботи таймера-лічильника 0

Режим роботи таймера, у т.ч. поведінка таймера-лічильника і пов'язаного з ним виходу формувача сигналу, задається комбінацією біт, які задають режим роботи таймера (WGM01, WGM00) і режим формування вихідного сигналу (COM01, COM00).. При цьому біти завдання режиму формування вихідного сигналу не впливають на алгоритм рахунку, тому що алгоритм рахунку залежить тільки від стану біт задання режиму роботи таймера. В режимах з ШІМ біти COM01, COM00 дозволяють включити/відключити інверсію на генеруючому ШІМ-виході (тобто вибрати ШІМ з інверсією або ШІМ без інверсії). Для режимів без ШІМ біти COM01: 0 визначають яку дію необхідно виконати при виконанні умови порівняння: скинути, встановити або інвертувати вихід.

Нормальний режим роботи

Найпростішим режимом роботи є нормальний режим (WGM01, WGM00 = 0b00). В даному режимі лічильник працює як додаючий (інкреметований), при цьому скид лічильника не виконується. Переповнення лічильника відбувається при переході через максимальне 8-розр.. число (верхня межа = 0xFF) до нижньої межі лічби (0x00). У нормальному режимі роботи мітка переповнення таймера-лічильника TOV0 буде встановлений на тому ж такті синхронізації, коли TCNT0 прийме нульове значення. Фактично, мітка переповнення TOV0 є дев'ятим бітом таймера-лічильника за тим винятком, що він тільки встановлюється і не скидається. Однак програмно ця властивість може бути використана для підвищення роздільної здатності таймера, якщо використовувати переривання по переповненню таймера, при виникненні якого мітка TOV0 скидається автоматично. Для нормального режиму роботи не існує яких-небудь особливих ситуацій пов'язаних із записом нового стану лічильника, коли потрібно було б врахувати запобіжні заходи.

Блок порівняння може використовуватися для генерації переривань. Не рекомендується використовувати вихід OC0 для генерації сигналів в нормальному режимі роботи, тому що в в цьому випадку буде витрачена значна частина процесорного часу.

Режим скидання таймера при збігу (CTC)

В режимі СТС (WGM01, WGM00 = 0b10) регістр OCR0 використовується для задання роздільної здатності лічильника. Якщо заданий режим CTC і значення лічильника (TCNT0) збігається зі значенням регістру OCR0, то лічильник обнулюється (TCNT0 = 0). Таким чином, OCR0 задає вершину лічби лічильника, а, отже, і його роздільну здатність. В даному режимі забезпечується більш широкий діапазон регулювання частоти генерованих прямокутних імпульсів. Він також спрощує роботу лічильника зовнішніх подій.

Тимчасова діаграма для режиму СТС показана на рисунку. Значення лічильника (TCNT0) інкрементується до тих пір, поки воно не стане рівним значенню в OCR0, після чого лічильник (TCNT0) обнулюється.

За допомогою мітки OCF0 переривання може генеруватися кожного разу, коли лічильник досягає своєї верхньої межі лічби. Якщо робота переривання дозволена, то процедура обробки переривання може використовуватися для оновлення значення вершини лічби. Однак, задання значення вершини лічби близького до значення нижньої межі лічби, коли лічильник працює без дільника частоти або з малим значенням дільника частоти, необхідно виконувати з особливою обережністю, тому що в режимі СТС немає подвійної буферизації. Якщо значення, записане в OCR0, менше поточного значення TCNT0, то скидання лічильника за умовою збігу настане, коли він досягне максимального значення (0xFF), потім перейде в початковий стан 0x00 і досягне нового значення OCR0.

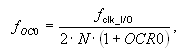

Для генерації сигналу в режимі CTC вихід компаратора OC0 може використовуватися для зміни логічного рівня при кожному збігу, для чого необхідно задати режим перемикання (COM01, COM00 = 0b01). Значення OC0 буде присутній на виводі порту, тільки якщо для даного виводу задано вихідний напрямок. Максимальна частота генерованого сигналу дорівнює fOC0 = fclk_I/O/2, якщо OCR0 = 0x00. Для інших значень OCR0 частоту генерованого сигналу можна визначити за формулою:

де змінна N задає коефіцієнт розподілу дільника частоти (1, 8, 32, 64, 128, 256 або 1024).

Також як і для нормального режиму роботи, мітка TOV0 встановлюється на тому ж такті таймера, коли його значення змінюється з 0xFF на 0x00.

Режим швидкої ШІМ

Режим швидкої широтно-імпульсної модуляції (WGM01, WGM00 = 0b11) дозволяє генерувати високочастотні ШІМ-сигнали.

Опис роботи цього режиму для даного мікроконтролера наведено у повному описі мікроконтролера.48

Режим широтно-імпульсної модуляції з фазовою корекцією (ШІМ ФК)

Режим ШІМ ФК (WGM01, WGM00 = 0b01) дозволяє виконувати фазову корекцію ШІМ-сигналу з високою роздільною здатністю.

Опис роботи цього режиму для даного мікроконтролера наведено у повному описі мікроконтролера.49