- •1 Загальні відомості

- •6 Відладка програми

- •7 Налаштування параметрів імітатора

- •ATmega128, aTmega128l 8-розрядний avr-мікроконтролер з внутрішньосистемною програмованою флеш-пам'яттю ємністю 128 кбайт Особливості:

- •Короткий огляд

- •Завдання:

- •Лабораторна робота №2 «Вивчення математичних і логічних операцій і їх вплив на біти-стану мікроконтролера» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №3 «Вивчення методів додавання і віднімання чотирьохбайтних чисел» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Лабораторна робота №5 «Вивчення роботи з пам’яттю даних» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Лабораторна робота №6 «Вивчення операцій порівняння і реалізація циклічних операцій» Ціль роботи

- •Програма виконання роботи

- •Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

- •Завдання:

- •Завдання:

- •Завдання:

- •Часові діаграми таймера-лічильника 0

- •Опис регістрів 8-розрядного таймера-лічильника 0

- •Асинхронна робота таймера-лічильника 0

- •Дільник частоти таймера-лічильника 0 Дільник частоти таймер-лічильника 0

- •Завдання:

- •Завдання:

- •Набір інструкцій

Завдання:

1. Об’явити дві двобайтні знакові константи:

2. У сегменті пам’яті даних об’явити змінну у яку буде записуватися результат множення

3. Розмістити вхідні величини у регістри мікроконтролера

4. Здійснити побайтне множення (з врахуванням того, які інструкції треба використати MUL, MULS, MULSU) і результати цих множень перемістити у резервні регістри для подальшого опрацювання.

5. Визначити значення третього байту множення

6. Записати перший (молодший) байт результату множення двох двобайтних знакових чисел у ОЗУ мікроконтролера (визначену попередньо змінну в п.2)

7.Сформувати другий байт результату множення двох двобайтних знакових чисел

7.1 Додати відповідні регістри

7.2 При додаванні здійснювати акумулювання всіх переносів у старші розряди

7.3 Записати другий байт множення двобайтним знакових чисел у ОЗУ двох двобайтних знакових чисел у ОЗУ мікроконтролера (визначену попередньо змінну в п.2)

8.Сформувати третій байт результату множення двох двобайтних знакових чисел

8.1 Додати відповідні регістри і переносів при формуванні другого байту результату

8.2 При додаванні здійснювати акумулювання всіх переносів у старші розряди

8.3 Записати третій байт множення двобайтним знакових чисел у ОЗУ двох двобайтних знакових чисел у ОЗУ мікроконтролера (визначену попередньо змінну в п.2)

9.Сформувати четвертий байт результату множення двох двобайтних знакових чисел

9.1 Додати відповідні регістри і переносів при формуванні третього байту результату

9.2 Записати четвертий байт множення двобайтним знакових чисел у ОЗУ двох двобайтних знакових чисел у ОЗУ мікроконтролера (визначену попередньо змінну в п.2)

9. Перевірити виконання програми на двох двобайтних додатних числах, двох від’ємних двобайтних числах, додатного двобайтного числа і від’ємного двобайтного числа.

Лабораторна робота №8 «Вивчення програмування паралельного порту вводу-виводу мікроконтролера AVR»

Ціль роботи

вивчити принципів роботи з паралельною шиною AVR мікроконтролера

закріпити знання попередніх лабораторних роботах

Програма виконання роботи

- Проініціалізувати потрібні порти мікроконтролера

- Прийняти вхідну інформацію з портів настроєних на прийом даних (Порт A і Порт B)

- Перемножити між собою вхідну інформацію

- Результат множення виставити на порти, які настроєні на вивід (Порт C і Порт D)

Додатковий теоретичний матеріал необхідний для виконання лабораторної роботи

Мікроконтролер ATMEGA128 має 53 програмовані лінії вводу/виводу. всі вони об’єднані у порти (кожен порт контролює 8 ліній вводу/виводу)

Опис портів

Порт A |

Порт A - 8-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуючими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту A мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту А будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту A знаходяться в третьому (високоімпедансное) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт А також виконує деякі спеціальні функції ATmega128. |

Порт B |

Порт B - 8-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуючими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту B мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту B будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту B знаходяться в третьому (високоімпедансное) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт B також виконує деякі спеціальні функції ATmega128. |

Порт C |

Порт C - 8-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуючими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту C мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту C будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту C знаходяться в третьому (високоімпедансное) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт C також виконує деякі спеціальні функції ATmega128. |

Порт D |

Порт D - 8-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуючими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту D мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту D будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту D знаходяться в третьому (високоімпедансное) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт D також виконує деякі спеціальні функції ATmega128 |

Порт E |

Порт E - 8-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуючими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту E мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту E будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту E знаходяться в третьому (високоімпедансное) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт E також виконує деякі спеціальні функції ATmega128 |

Порт F |

Порт F діє як аналоговий ввід аналогово-цифрового перетворювача. Порт F також може використовуватися як 8-розр. порт двонаправленого вводу-виводу, якщо АЦП не використовується. До кожної лінії порту може бути підключений вбудований підтягаючий до плюсу резистор (вибирається окремо для кожного біта). Вихідні буфери порту F мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту F діятимуть як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту F знаходяться в третьому (високоімпедансному) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Якщо активізований інтерфейс JTAG, то підтягуючі резистори на лініях PF7 (TDI), PF5 (TMS) і PF4 (TCK) будуть підключені, навіть якщо виконується Скидання. Висновок TDO знаходиться в третьому стані, якщо не введено стан TAP, при якому зсуваються виводяться дані. Порт F також виконує функції інтерфейсу JTAG. |

Порт G |

Порт G - 5-розр. порт двонаправленого вводу-виводу з внутрішніми підтягуютчими до плюсу резисторами (вибираються окремо для кожного розряду). Вихідні буфери порту G мають симетричну вихідну характеристику з однаковими вхідними і вихідними струмами. При вводі, лінії порту G будуть діяти як джерело струму, якщо зовні діє низький рівень і включені підтягуючі резистори. Виходи порту G знаходяться в третьому (високоімпедансному) стані при виконанні умови скидання, навіть якщо синхронізація не запущена. Порт G також виконує деякі спеціальні функції ATmega128. |

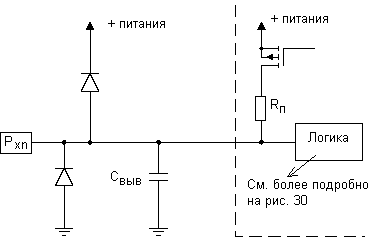

Всі порти вводу-виводу (ПВВ) AVR-мікроконтролерів працюють за принципом читання-модифікація-запис при використанні їх як портів універсального вводу-виводу. Це означає, що зміна напрямку вводу-виводу одної лінії порту командами SBI і CBI буде відбувається без помилкових змін напрями вводу-виводу інших ліній порту. Це поширюється також і на зміну логічного рівня (якщо лінія порту налаштована на вивід) або на включення/відключення підтягуючих резисторів (якщо лінія налаштована на ввід). Кожен вихідний буфер має симетричну характеристику управління з високим вхідними і вихідними струмами. Вихідний драйвер володіє навантажувальною здатністю, яка дозволяє безпосередньо керувати світлодіодними індикаторами. До всіх лініях портів може бути підключений індивідуальний вибірковий підтягаючий до плюсу живлення резистор, опір якого не залежить від напруги живлення. На всіх лініях ПВВ встановлені захисні діоди, які підключені до VCC і Загальному (GND), як показано на малюнку.

Посилання на регістри і біти регістрів в даному описі дані в загальній формі. При цьому, символ "x" замінює найменування ПВВ, а символ "n" замінює номер розряду ПВВ. Однак при написанні програми необхідно використовувати точну форму запису. Наприклад, PORTB3, що означає розряд 3 порту B, в даному документі записується як PORTxn.

Для кожного порту вводу-виводу в пам'яті вводу-виводу зарезервовано три комірки: одна під регістр даних - PORTx, інша під регістр напрямку даних - DDRx і третя під стан входів порту - PINx. Комірка, що зберігає стан на входах портів, доступна тільки для читання, а регістри даних і напрямку даних мають двонаправлений доступ. Крім того, установка біта виключення підтягуючих резисторів PUD регістра SFIOR відключає функцію підтягування на всіх виходах всіх портів.

Нижче наведено опис порту вводу-виводу для універсального цифрового вводу-виводу. Більшість виходів портів підтримують альтернативні функції вбудованих периферійних пристроїв мікроконтролера. Опис альтернативних функцій наведено далі в описі до мікроконтролера..

Зверніть увагу, що для деяких портів дозвіл альтернативних функцій деяких виходів робить неможливим використання інших виходів для універсального цифрового вводу-виводу.

Порт у якості універсального цифрового вводу-виводу

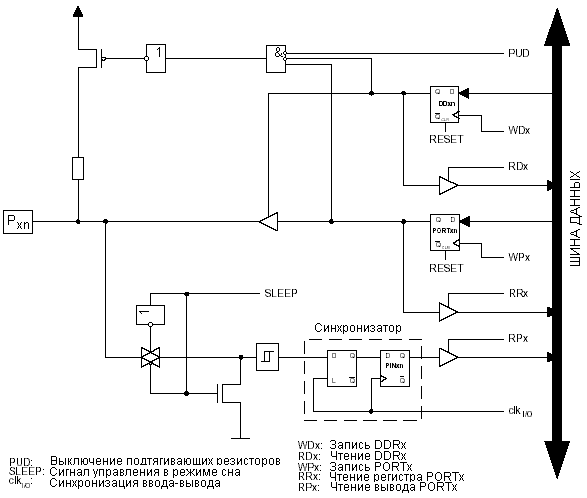

Всі порти є двонаправленими портами вводу-виводу з опціональним підтягуючим резистором. Рисунок ілюструє функціональну схему однієї лінії порту вводу-виводу, позначений як Pxn.

Сигнали WPx, WDx, RRx, RPx і RDx є загальними в межах одного порту. Сигнали clkI/O, SLEEP, і PUD є загальними для всіх портів.

Настройки виходів

Режим і стан для кожного виводу визначається значенням відповідних розрядів трьох регістрів: DDxn, PORTxn і PINxn.

Біти DDxn регістра DDRx визначають спрямованість лінії вводу-виводу. Якщо DDxn = 1, то Pxn конфігурується на вивід. Якщо DDxn = 0, то Pxn конфігурується на ввід.

Якщо PORTxn = 1 при конфігурації лінії порту на ввід, то дозволяється підключення підтягуючого резистора. Для виключення даного резистора необхідно записати в PORTxn лог. 0 або налаштувати лінію порту на вивід. Під час скидання всі лінії портів знаходяться в третьому (високоімпедансному) стані, навіть якщо не працює синхронізація.

Якщо PORTxn = 1 при конфігурації лінії порту на вивід, то стан виходу у логічній одиниці. Якщо PORTxn = 0 при конфігурації лінії порту на вивід, то стан виходу у логічному нулі.

Оскільки одночасний запис у регістри DDRx і PORTx неможливий, то при перемиканні між третім станом ({DDxn, PORTxn} = 0b00) і виведенням лог. 1 ({DDxn, PORTxn} = 0b11) повинно виникнути проміжний стан або з підключеним підтягуючого резистора ({DDxn, PORTxn} = 0b01) або з виводом лог. 0 ({DDxn, PORTxn} = 0b10). Як правило, перехід через стан з підключенням підтягуючого резистора еквівалентно стану виходу лог.1, якщо вихід мікроконтролера зв’язаний з високоімпедансним входом. В іншому випадку, необхідно встановити біт PUD регістра SFIOR для виключення всіх підтягаючих резисторів на всіх портах.

Перемикання між вводом з підтягуючим резистором і виводом низького рівня пов'язане з аналогічною проблемою. Тому, користувач змушений використовувати або третій стан ({DDxn, PORTxn} = 0b00) або вивід лог. 1 ({DDxn, PORTxn} = 0b11) в якості проміжного етапу.

У таблиці підсумовується дію керуючих сигналів на стан виводу.

DDxn |

PORTxn |

PUD (в SFIOR) |

Ввід-вивід |

Підтягуючий резистор |

Коментар |

0 |

0 |

X |

Ввід |

Ні |

Третій стан (Z-стан) |

0 |

1 |

0 |

Ввід |

Так |

Pxn буде джерелом струму при подачі зовнішнього низького рівня |

0 |

1 |

1 |

Ввід |

Ні |

Третій стан (Z-стан) |

1 |

0 |

X |

Вивів |

Ні |

Вивід лог. 0 |

1 |

1 |

X |

Вивів |

Ні |

Вивід лог. 1 |

Зчитування стану входу

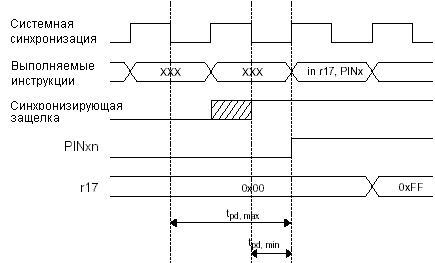

Незалежно від значення біту напряму даних DDxn стан виходу порту може бути опитано через регістровий біт PINxn. Як показано на попередньому рисунку регістровий біт PINxn і попередня йому тригерна «защолка» створюють синхронізатор. Даний підхід дозволяє уникнути метастабільності, якщо зміна стану на виводі сталося коло фронту внутрішньої синхронізації. Однак такий підхід пов'язаний з виникненням затримки. На рисунку представлена тимчасова діаграма синхронізації під час опитування зовні прикладеного до виходу сигналу. Тривалість мінімальної і максимальної затримок на поширення сигналу позначені як tpd, max і tpd, min, відповідно.

У наступних прикладах показано як встановити на лініях 0 і 1 порту В рівень лог. 1, а на лініях 2 і 3 - лог. 0, а також як налаштувати лінії 4 ... 7 на введення з підключенням підтягаючих резисторів на лініях 6 і 7. Результуючий стан ліній зчитуються назад, але, з урахуванням сказаного вище, включена інструкція nop для забезпечення можливості зворотного зчитування щойно назначеного стану деяких виводів.

Приклад коду на Асемблері

...

; Дозволяємо підтягування і встановлюємо високі вихідні рівні

; Визначаємо напрями даних ліній портів

ldi r16, (1 << PB7) | (1 << PB6) | (1 << PB1) | (1 << PB0)

ldi r17, (1 << DDB3) | (1 << DDB2) | (1 << DDB1) | (1 << DDB0)

out PORTB, r16

out DDRB, r17

; Вставляємо інструкцію nop для синхронізації

nop

; Опитування стану виходів порту

in r16, PINB

...

Прим. 1: В програмі на Асемблері використовуються два тимчасових регістра для мінімізації інтервалу часу від настройки підтягаючих резисторів на розрядах 0, 1, 6 і 7 до коректної установки біту напрямку, які дозволяють вивід лог. 0 на лініях 2 і 3 і замінюють високий рівень на розрядах 0 і 1, утворений за рахунок підключення підтягаючих резисторів, на високий рівень потужнострумового драйвера.

Регістри вводу/виводу (які треба знати при виконанні цієї лабораторної роботи)

Адреса |

Номер регістру вводу/виводу47 |

Назва |

Біт 7 |

Біт 6 |

Біт 5 |

Біт 4 |

Біт 3 |

Біт 2 |

Біт 1 |

Біт 0 |

Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128 |

||||||||||

$65 |

|

PORTG |

- |

- |

- |

PORTG4 |

PORTG3 |

PORTG2 |

PORTG1 |

PORTG0 |

$64 |

|

DDRG |

- |

- |

- |

DDG4 |

DDG3 |

DDG2 |

DDG1 |

DDG0 |

$63 |

|

PING |

- |

- |

- |

PING4 |

PING3 |

PING2 |

PING1 |

PING0 |

$62 |

|

PORTF |

PORTF7 |

PORTF6 |

PORTF5 |

PORTF4 |

PORTF3 |

PORTF2 |

PORTF1 |

PORTF0 |

$61 |

|

DDRF |

DDF7 |

DDF6 |

DDF5 |

DDF4 |

DDF3 |

DDF2 |

DDF1 |

DDF0 |

$60 |

|

Резерв |

- |

- |

- |

- |

- |

- |

- |

- |

$5F |

$3F |

SREG |

I |

T |

H |

S |

V |

N |

Z |

C |

$5E |

$3E |

SPH |

SP15 |

SP14 |

SP13 |

SP12 |

SP11 |

SP10 |

SP9 |

SP8 |

$5D |

$3D |

SPL |

SP7 |

SP6 |

SP5 |

SP4 |

SP3 |

SP2 |

SP1 |

SP0 |

Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128 |

||||||||||

$3B |

$1B |

PORTA |

PORTA7 |

PORTA6 |

PORTA5 |

PORTA4 |

PORTA3 |

PORTA2 |

PORTA1 |

PORTA0 |

$3A |

$1A |

DDRA |

DDA7 |

DDA6 |

DDA5 |

DDA4 |

DDA3 |

DDA2 |

DDA1 |

DDA0 |

$39 |

$19 |

PINA |

PINA7 |

PINA6 |

PINA5 |

PINA4 |

PINA3 |

PINA2 |

PINA1 |

PINA0 |

$38 |

$18 |

PORTB |

PORTB7 |

PORTB6 |

PORTB5 |

PORTB4 |

PORTB3 |

PORTB2 |

PORTB1 |

PORTB0 |

$37 |

$17 |

DDRB |

DDB7 |

DDB6 |

DDB5 |

DDB4 |

DDB3 |

DDB2 |

DDB1 |

DDB0 |

$36 |

$16 |

PINB |

PINB7 |

PINB6 |

PINB5 |

PINB4 |

PINB3 |

PINB2 |

PINB1 |

PINB0 |

$35 |

$15 |

PORTC |

PORTC7 |

PORTC6 |

PORTC5 |

PORTC4 |

PORTC3 |

PORTC2 |

PORTC1 |

PORTC0 |

$34 |

$14 |

DDRC |

DDC7 |

DDC6 |

DDC5 |

DDC4 |

DDC3 |

DDC2 |

DDC1 |

DDC0 |

$33 |

$13 |

PINC |

PINC7 |

PINC6 |

PINC5 |

PINC4 |

PINC3 |

PINC2 |

PINC1 |

PINC0 |

$32 |

$12 |

PORTD |

PORTD7 |

PORTD6 |

PORTD5 |

PORTD4 |

PORTD3 |

PORTD2 |

PORTD1 |

PORTD0 |

$31 |

$11 |

DDRD |

DDD7 |

DDD6 |

DDD5 |

DDD4 |

DDD3 |

DDD2 |

DDD1 |

DDD0 |

$30 |

$10 |

PIND |

PIND7 |

PIND6 |

PIND5 |

PIND4 |

PIND3 |

PIND2 |

PIND1 |

PIND0 |

Буде описано пізніше або можна ознайомитися з опису до мікроконтролера ATMEGA128 |

||||||||||

Це корисно!

Для зручності використання AVR Studio при написанні програм для різних мікроконтролерів, у яких регістри вводу/виводу чи розширених регістрів вводу/виводу, а також деяких пере позначень регістрів регістрового файлу (зокрема X, Y і Z), абсолютні адреси яких у різних мікроконтролерах можуть бути різні, але назва і функціональне призначення є однакове – розробниками AVR Studio у папці \Program Files\Atmel\AVRTools\AVRAssembler\Аppnotes\ знаходяться *.inc файли у яких директивами EQU і DEF описані визначені всі регістри і відповідні біти регістрів, а також здійснено деякі визначення.

Для того, щоб включити у проект визначення регістрів мікроконтролера ATMEGA128 треба в проект включити m128def.inc файл.

Опис деяких мнемонік інструкцій, які можуть бути використовані у цій лабораторній роботі і не були описані у описах до попередніх лабораторних робіт

CBI – «Очистка біту в регістрі вводу-виводу»

Інструкція очищує вказаний біт в регістрі вводу-виводу. Ця інструкція виконується тільки на перших 32-ох регістрах області регістрів вводу-виводу – адреси 0÷31

I/O(A,b) ← 0

Синтаксис |

Операнди |

Лічильник команд |

CBI A, b |

0 ≤ A ≤ 31, 0 ≤ b ≤ 7 |

PC ← PC + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

- |

- |

- |

- |

- |

- |

- |

- |

Наприклад:

Приклад 1:

cbi $12, 7 ;Очистка біту 7 в регістрів PORTD

Приклад 2:

.INCLUDE "m128def.inc"

…

cbi PORTD, 7 ;Очистка біту 7 в регістрів PORTD

CBR – «Очистка біту в регістрі»

Інструкція очищує вказаний біт в регістрі Rd. Вона виконує логічне І між вмістимим регістру Rd і інвертованою константою K. Результат буде поміщений у Rd

![]()

Синтаксис |

Операнди |

Лічильник команд |

CBR Rd, K |

16 ≤ Rd ≤ 31, 0 ≤ b ≤ 255 |

PC ← PC + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

- |

- |

- |

<> |

0 |

- |

<> |

- |

![]() Для

тестування знаку

Для

тестування знаку

![]() Очищується

Очищується

![]() Встановлюється

якщо MSB встановлений;

очищується інакше.

Встановлюється

якщо MSB встановлений;

очищується інакше.

![]() Встановлюється,

якщо результат $00; інакше

очищується

Встановлюється,

якщо результат $00; інакше

очищується

Наприклад:

cbr r16, $F0 ;Очистка старшої тетради регістра R16

cbr r18, 1 ;Очистка біта 0 регістра R18

SBI – «Встановлення біту в регістрі вводу-виводу»

Інструкція встановлює вказаний біт в регістрі вводу-виводу. Ця інструкція виконується тільки на перших 32-ох регістрах області регістрів вводу-виводу – адреси 0÷31

I/O(A,b) ← 1

Синтаксис |

Операнди |

Лічильник команд |

SBI A, b |

0 ≤ A ≤ 31, 0 ≤ b ≤ 7 |

PC ← PC + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

- |

- |

- |

- |

- |

- |

- |

- |

Наприклад:

Приклад 1:

sbi $12, 7 ;Встановлення біту 7 в регістрів PORTD

Приклад 2:

.INCLUDE "m128def.inc"

…

cbi PORTD, 7 ;Встановлення біту 7 в регістрів PORTD

SBR – «Встановлення біту в регістрі»

Інструкція встановлює вказаний біт в регістрі Rd. Вона виконує логічне АБО між вмістимим регістру Rd і константою K. Результат буде поміщений у Rd

![]()

Синтаксис |

Операнди |

Лічильник команд |

SBR Rd, K |

16 ≤ Rd ≤ 31, 0 ≤ K ≤ 255 |

PC ← PC + 1 |

Вплив на регістри статусу:

I |

T |

H |

S |

V |

N |

Z |

C |

- |

- |

- |

<> |

0 |

- |

<> |

- |

Для тестування знаку

Очищується

Встановлюється якщо MSB встановлений; очищується інакше.

Встановлюється, якщо результат $00; інакше очищується

Наприклад:

sbr r16, 3 ;Встановлення бітів 0÷3 у регістрі R16

sbr r17, $F0 ;Встановлення старші чотири біти регістра R17