Мультиплексор и демультиплексор.

Во многих случаях возникает необходимость последовательного опроса логических состояний большого числа переменных и передачи их на один выход. Для этой цели служит специальное устройство, называемое мультиплексором.

Мультиплексор передает сигнал с одного из информационных входов xi на единственный выход y, причем номер этого входа равен десятичному эквиваленту двоичного кода на адресных входах ai.

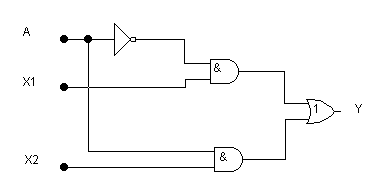

Создадим устройство, передающее на выход У один из двух входных сигналов Х1 или Х2 – мультиплексор 21.

Х

1

1

У

У

Х2

А

Рис.4а.

Рис.4а.

Таблица истинности устройства будет иметь вид:

Адресный вход |

ВыходУ |

0 |

Х1 |

1 |

Х2 |

Исходя из таблицы, построим ФАЛ: У = Х1*А + Х2*А.

Синтезируем устройство, соответствующее такой простой функции:

Рис.4б.

Рис.4б.

Х1

MUX

Х1

MUX

X2 Y

X2 Y

A

Рис.4.в. Условное графическое изображение мультиплексора.

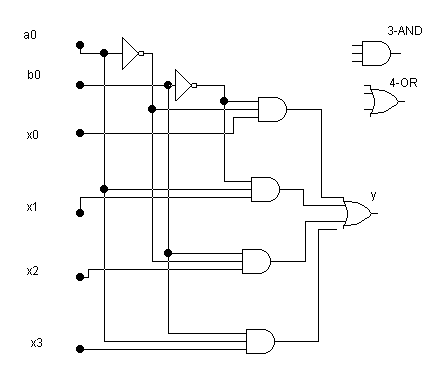

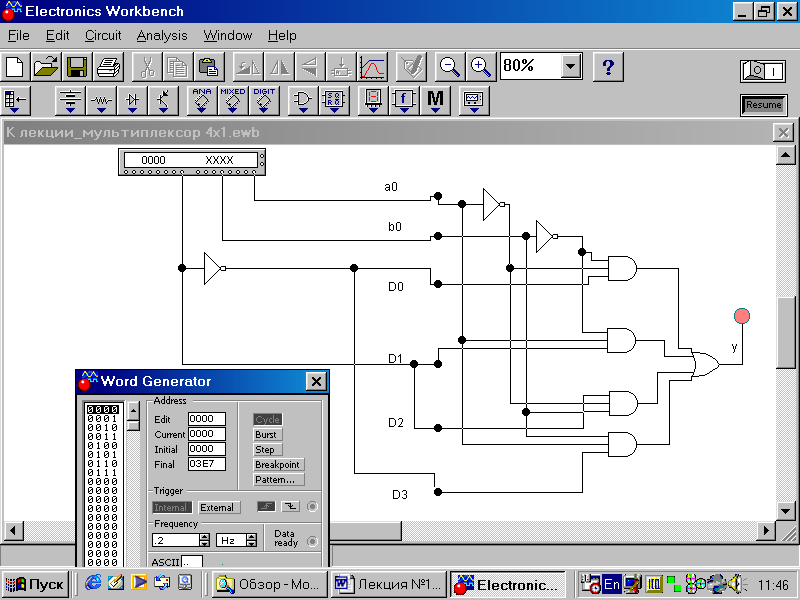

На рис.4с представлена схема мультиплексора на 4 входа.

Рис.4с.

Мультиплексор имеет адресные входы а0 и а1 и 4 информационных входа х0-х3. В зависимости от состояния адресных входов выход мультиплексора соединяется с одним из его информационных входов. Схема построена таким образом, что с выходом соединяется тот вход, индекс которого равен двоичному числу, определяемому переменными а0 и а1. Непосредственно из схемы следует, что

y = a1a0x0 + a1a0x1 + a1a0x2 + a1a0x3

В формуле для у логическое произведение адресных сигналов равно единице только для той входной переменной, индекс которой совпадает с требуемым адресом. Например, если a1 =1, а a0=0, то

y = 1*1*x0 + 1*0*x1 + 0*1*x2 + 0*0*x3

По этому принципу эту схему можно распространить на любое число входных переменных. Если мультиплексор имеет n адресных входов, то ими можно коммутировать 2n информационных входов.

Промышленностью выпускаются следующие мультиплексоры в интегральном исполнении:

|

TTL |

ЭСЛ |

КМОП |

16 входов |

SN 74150 |

|

|

8 входов |

SN 74151 |

МС 10164 |

МС 14512 |

2х4 входа |

SN 74153 |

МС 10174 |

МС14539 |

4х2 входа |

SN 74157 |

|

МС14519 |

Демультиплексор.

Иногда возникает обратная задача – передача одного входного сигнала по нескольким различным адресам. Схемное решение такой задачи приведено на рис.5. На рисунке приведена схема демультиплексора на 4 выхода. Если схема имеет n адресных входов, то она может управлять 2n выходами.

Рис.5.

Промышленностью выпускаются следующие демультиплексоры в интегральном исполнении:

|

TTL |

ЭСЛ |

КМОП |

16 выходов |

SN 74154 |

|

МС 14514 |

10 выходов |

SN 7442 |

|

|

8 выхода |

SN 74S138 |

МС 10162 |

|

2х4 выхода |

SN 74155 |

МС 10172 |

МС14555 |

Если на х подавать логическую 1, то демультиплексор работает как дешифратор. Вход х можно рассматривать как стробирующий вход такого дешифратора.

Кроме функции коммутации входов мультиплексор позволяет реализовать множество ФАЛ.

Пусть ФАЛ задана картой Карно:

x2x3 |

|||||

x1 |

|

00 |

01 |

11 |

10 |

0 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

Запишем ФАЛ

_ _ _ _ _ _

Y = x1x2x3 + x1x2x3 + x1x2x3 + x1x2x3

Сравним ее с формулой мультиплексора для 3-х переменных:

_ _ _ _ _ _ _ _ _ _ _

Y = A0A1A2D0 + A0A1A2D1 + A0A1A2D2 + A0A1A2D3 + A0A1A2D4 + A0A1A2D5 +

_

+ A0A1A2D6 + A0A1A2D7

Из сравнения получим значения коэффициентов Di:

D0 = D3 = D5 = D6 = 1

D1 = D2 = D4 = D7 = 0

Тогда для реализации ФАЛ необходимо на адресные входы A0, A1, A2 подать переменные x1 , x2 , x3 а на информационные входы D0 – D7 подать 0 или 1 в соответствии с их значениями.

0

1

0

1

D0

D0

D1 К8-1

D2

D3

D4

D5 Y

D6

D7

D7

X0 A0

X1 A1

X2 A2

Мы рассмотрели простой случай, когда количество переменных равно количеству адресных входов.

Возможно построение ФАЛ на мультиплексоре даже если количество переменных превышает количество адресных входов.

В общем случае, когда требуется синтезировать КУ, реализующее функцию N аргументов на мультиплексоре с M управляющими входами и 2М информационными входами, М младших переменных из набора Х1, Х2, . . . . ХN следует подать на управляющие входы, а информационные сигналы (настроечные) D0, D1, . . . . D2м нужно представить функциями остальных (N - M) переменных, как показано на рис. Тогда синтез КУ сводится, по сути дела, к синтезу схемы формирования информационных сигналов, которую можно рассматривать как внутреннее более простое КУ.

Xm+1 D0

Xm+1 D0

К8-1

Схема

формиро-

вания

КУ Y

XN

D2m

X0 A0

Xm Am

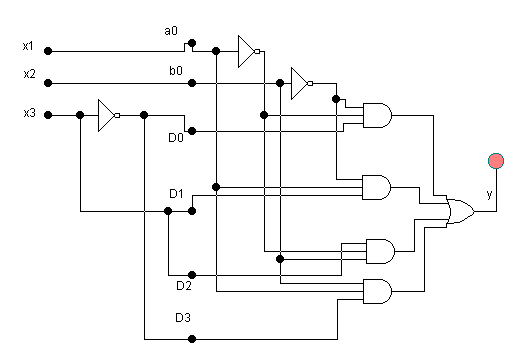

Например, пусть требуется реализовать на мультиплексоре с 2-мя адресными входами (4 информационных) ФАЛ 3-х переменных:

_ _ _ _ _ _

Y = x1x2x3 + x1x2x3 + x1x2x3 + x1x2x3

Воспользуемся методом декомпозиции и представим ФАЛ в виде функции двух переменных, и функции на множестве 0,1, третья переменная.

_ _ _ _

Y = f0(0,0,x3) x1x2 + f1(0,1,x3) x1x2 + f2(1,0,x3) x1x2 + f3(1,1,) x1x2

Вычислим fi

_ _

f0 = x3, f1 = x3 , f2 = x3, f3 = x3

Подаем на управляющие входы х0, х1 а на информационные входы D0-D3 подадим вычисленные значения fi.

Например, пусть требуется реализовать на мультиплексоре с 3-мя адресными входами (8 информационных) ФАЛ 4-х переменных:

_ _ _ _ _ _ _ _

Y = x1x2x3 + x1x2x3 + x2x3x4 + x2x3x4 + x1x3x4 + x1x2x4

Воспользуемся методом декомпозиции и представим ФАЛ в виде функции трех переменных, и функции на множестве 0,1, четвертая переменная. _ _ _ _ _ _ _

Y = f0(0,0,0,x4) x1x2x3 + f1(0,0,1,x4) x1x2x3 + f2(0,1,0,x4) x1x2x3 +

_ _ _ _

f3(0,1,1,x4) x1x2x3 + f4(1,0,0,x4) x1x2x3 + f5(1,0,1,x4) x1x2x3 +

_

f6(1,1,0,x4) x1x2x3 + f7(1,1,1,x4) x1x2x3

Вычислим fi

_ _

f0 = 0, f1 = x4 , f2 = 1, f3 = 0, f4 = x4, f5 = 1, f6 = 1, f7 = x4

Таким образом, для реализации заданной ФАЛ необходимо на 3 адресных входа подать переменные x1, x2, x3 , а на каждый из 8-ми информационных входов – соответствующее значение fi.

0

1

0

1

D0

D1

К8-1

D1

К8-1

D2

D3

X4 D4

D5 Y

_ D6

X4 ` D7

X0 A0

X1 A1

X2 A2