- •Раздел I. Схемотехника матричных схем (темы 1-12)

- •Раздел II. Аналоговая схемотехника

- •4. Примеры микросхем цифровых узлов (схем с памятью)

- •(Уго – условное графическое, или функциональное, обозначение)

- •Внимание. Данная временная диаграмма:

- •5. О нумерации разрядов двоичного кода

- •6. Принцип работы простейших сдвигающих регистров

- •7. К цифровым устройствам (цу) относятся также запоминающие устройства (зу)

- •8. Пример микросхемы памяти (микросхемы зу) – к155ру2 Задание для портфолио № 1 – уго к155ру2 (зарисовать)

- •Обозначение и назначение сигналов

- •64 Бит, или 16 четырехразрядных слов.

- •10. Организация зу –

- •Варианты организации памяти с информационной емкостью 16 бит:

- •Контрольная работа № 1а. Варианты 1а-1, 1а-2, …, 1а-5

- •Варианты организации памяти с информационной емкостью 64 бит:

- •Контрольная работа № 1б. Варианты 1б-1, 1б-2, …, 1б-6

- •11. Типы запоминающих элементов (зэ) озу, или элементов памяти

- •Обычные триггеры и регистры.

- •2) Специальные экономичные триггерные зэ. Сколько радиоэлементов содержит обычный триггер? Задание для портфолио № 2 – три схемы триггера (на базе ттл)

- •12. Классификация полупроводниковых зу

- •О классификации зу

- •13. Типы выходов цифровых элементов

- •13.4. Использование буферных элементов (буферов) типа тс

- •(В двух вариантах обозначений) Задание для портфолио № 4 – типы буферных каскадов с тс

- •13.5. Выход с открытым коллектором (стоком)

- •В обозначениях элементов с ок или ос после символа функции ставится ромб с черточкой снизу

- •Выход с программированием тс-ос

- •Примеры буферных элементов в серии к155

- •Вариант обозначений типов выходов (выходных сигналов) ттл-совместимых микросхем

- •14. Регистровые файлы (будут подробно рассмотрены в теме 02)

- •Задание для портфолио № 5 – схема регистрового файла ир26 (организация 4×4). У этого задания будет продолжение

- •1 7. Схемотехническое (физико-технологическое) исполнение микросхем памяти

13. Типы выходов цифровых элементов

Цифровые элементы (логические, запоминающие, буферные) могут иметь выходы следующих типов:

- логический выход,

- выход с открытым коллектором ОК (с открытым стоком ОС),

- выход с третьим состоянием, или с тремя состояниями (ТС, или z),

- выход с открытым эмиттером ОЭ (с открытым истоком).

Наличие четырех типов выходов объясняется различными условиями работы элементов в логических цепях, магистрально-модульных системах и т. д.

Дополнительная разновидность:

- выход с программированием ТС-ОС (с тремя состояниями или с открытым стоком),

РАССМОТРИМ ТИПЫ ВЫХОДОВ ПОДРОБНЕЕ

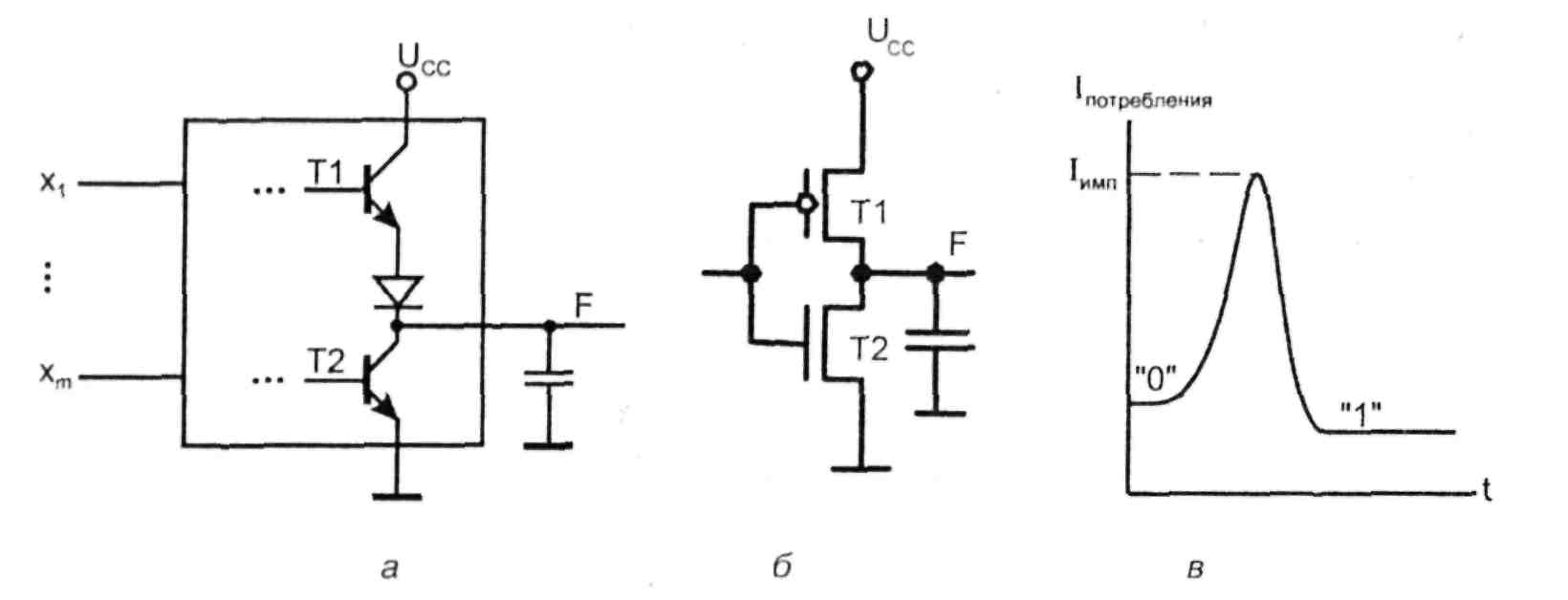

13.1. Стандартный элемент ТТЛ (с логическим выходом)

Totem-pole – выходной двухтранзисторный каскад

totem-pole output каскадный выход каскодный выход

Рис. Схемы логических выходов цифровых элементов:

а – ТТЛ, б – КМОП (нижний транзистор n-типа, верхний – p-типа),

в – график изменения потребляемого ими тока в процессе переключения

UCC – это EП

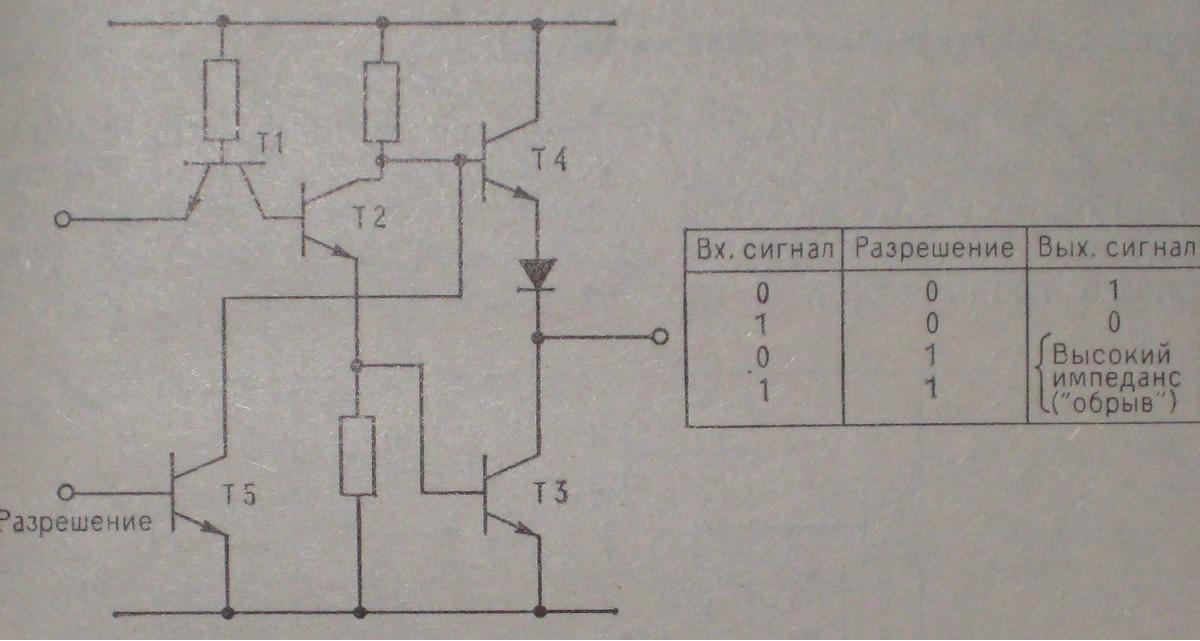

13.2. Элемент ТТЛ с тремя состояниями выходного сигнала (коротко – элемент ттл с тремя состояниями выхода, трехстабильный элемент ТТЛ, не путать с элементом памяти)

Задание для портфолио № 3 – элемент ТТЛ с ТС

(схема и таблица истинности)

Элементы с тремя состояниями выхода (выходами типа ТС или Z) кроме логических состояний 0 и 1 имеют состояние "отключено", в котором ток выходной цепи пренебрежимо мал. В это состояние (третье или Z-состояние) элемент переводится специальным управляющим сигналом, обеспечивающим запертое состояние обоих транзисторов выходного каскада (Т3 и Т4 на рис.). Сигнал управления элементом типа ТС (сигнал Разрешение на рис.) обычно обозначается как ОЕ (Output Enable). При наличии разрешения (в данной схеме ОЕ = 0) элемент работает как обычно, выполняя свою логическую операцию, а при его отсутствии (ОЕ = 1) переходит в состояние “отключено”. Вместо OE могут использоваться также обозначения этого входа V или VZ.

Таблица истинности ТТЛ-инвертора с тремя состояниями выходного сигнала

Входной сигнал |

Разрешение |

Выходной сигнал |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

Высокий импеданс (“обрыв”) |

1 |

1 |

Варианты УГО инвертора с тремя состояниями выхода

Управляющий вход обозначается V (#V) или VZ (#VZ)

![]()

![]()

Варианты УГО повторителя с тремя состояниями выхода

Пример – микросхема К155 ЛП8, содержащая 4 буферных элемента с ТС, т.е., с возможностью выхода на общую шину (***без инверсии).

Рис. Микросхема К155 ЛП8

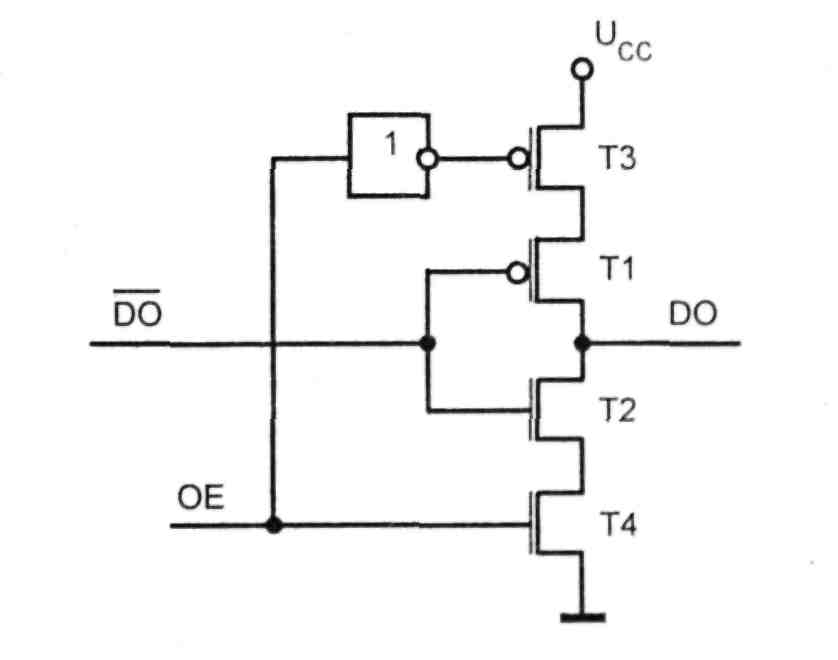

13.3. СХЕМА КМОП-ИНВЕРТОРА

С ТРЕМЯ СОСТОЯНИЯМИ ВЫХОДА

На рис. показан выходной каскад с третьим состоянием, используемый в схемотехнике КМОП. Высокий уровень сигнала ОЕ в этой схеме означает разрешение работы, он открывает транзисторы Т3 и Т4 и, тем самым, позволяет нормально работать инвертору на транзисторах TI и Т2, через который данные DO передаются на выход. При низком уровне сигнала ОЕ транзисторы Т3 и Т4 заперты и выход DO находится в состоянии "отключено".

Рис. КМОП-инвертор с тремя состояниями выхода