- •В нинішній час великий розвиток отримали цифрові методи обробки інформації, та цифрові системи на основі сучасної елементної бази.

- •3. Під системою числення розуміють спосіб подання будь-якого числа за допомогою деякого алфавіту символів, названих цифрами.

- •Лекція 2.

- •Лекція 3

- •Лекція 5

- •Основні поняття алгебри логіки

- •Лекція 6

- •Лекція 7

- •2. Логічні функції мінімізуються за допомогою аксіом та законів ал. При цьому отримують спрощені логічні вирази, на основі яких розробляються логічні схеми.

- •Лекція 9

- •Лекція 10

- •2. Шифратором, або кодером, називають комбінаційний логічний пристрій для перетворення чисел з десяткової сч в двійкову.

- •Лекція 11

- •Лекція 12

- •2 Багатоступеневі(каскадні) дешифратори

- •Лекція 13

- •3 Двохступінчатий дешифратор на основі матричного.

- •4 Дешифратори в інтегральному виконуються на базі об’єднання матриць дешифраторів.

- •Лекція 14

- •2. Умовне графічне позначення мультиплексора та логічна схема, що відповідає такій фал зображені на рисунках 14.1 та 14.2 відповідно.

- •Лекція 15

- •Лекція 16

- •2. Розглянемо функцію алгебри логіки, що описує операцію арифметичного складання двох однорозрядних двійкових кодів х1 та х0. Алгоритм її виконання пояснюється наступною таблицею істинності:

- •Лекція 17

- •2. Функціонування однорозрядного суматора визначається системою фал

- •Лекція 18

- •Лекція 19

- •Лекція 20

- •Лекція 22

- •Лекція 23

- •3. Класифікація зп. За функціями, які виконуються, зп можна класифікувати на:

- •6. Динамічні озп. В динамічних озп інформація зберігається у вигляді заряду на конденсаторі.

- •Лекція 24

- •Масочні пзп. До масочних пзп відносять пзп, інформація в яких записується безпосередньо при їх виготовленні.

- •Програмовані пзп. Програмовані пзп відносяться до класу пристроїв, що програмуються лише один раз, безпосередньо їх споживачем.

- •Лекція 25

- •3 Методи перетворення інформації.

- •Лекція 26

- •Лекція 27

- •2. Загальна структурна схема пліс. Розглянемо загальне питання технічної реалізації системи фал, заданої у вигляді диз’юнктивної нормальної форми. Для цього розглянемо систему фал виду:

- •Література

Лекція 9

Тема: Синтез комбінаційних схем.

План.

Загальні відомості.

Етапи синтезу комбінаційних схем.

1. Комбінаційними називаються функціональні вузли (блоки), логічний стан виходів яких залежить тільки від комбінації логічних сигналів на входах в певний момент часу.

Комбінаційні вузли та блоки цифрових систем або збираються з окремих ІС, що виконують функції елементів І-НІ, АБО-НІ, І-АБО-НІ, «Виключне» АБО та ін., або виготовляються у вигляді систем ІС, або входять до складу ВІС і НВІС.

2. Вихідними даними (технічним завданням) для проектування

комбінаційного вузла є його функціональний опис і вимоги до основних електричних параметрів. Функціональний опис комбінаційного вузла зазвичай задається у вигляді таблиці істинності або алгебраїчного виразу. Процес проектування розбивається на декілька послідовних етапів:

1) вибір елементної бази та способу реалізації;

2) мінімізація заданої логічної функції;

3) перетворення мінімізованої логічної функції та синтез логічної схеми;

4) синтез електричної схеми;

5) аналіз та оптимізація електричної схеми.

Вибір елементної бази (ТТЛ, ЕСЛ, КМДТТЛ або їхньої модифікації) визначається вимогами, пропонованими до електричних параметрів комбінаційного вузла: швидкодією, потужністю, що споживається, завадостійкістю та ін. Аналіз логічних елементів, і отримані на його основі рекомендації з їхнього застосування дозволяють проектувальнику після оцінних розрахунків вибрати той або інший варіант схеми базового елемента виходячи з вимог технічного завдання. При цьому визначається також можливий спосіб реалізації проектованого вузла:

елементна реалізація на базі готових схем логічних елементів, що випускають серійно у вигляді МІС або входять до складу функціональних бібліотек для проектування БІС і НВІС;

компонентна реалізація – шляхом розробки оригінальної схеми, яка найбільшою мірою задовольняє вимоги технічного завдання.

Елементна база та спосіб реалізації проектованого пристрою можуть бути визначені в технічному завданні, наприклад шляхом визначення серії мікросхеми, на базі якої даний пристрій повинне бути побудований.

Мінімізація логічної функції виконується за допомогою одного з методів. У результаті для заданої функції виходить одне або кілька мінімізованих виразів, звичайно представлених у диз'юнктивній нормальній формі

При використанні деяких типів базових елементів логічна функція F повинна бути представлена в інверсно-диз'юнктивній формі. В цьому випадку мінімізується функція F (інверсна заданої), шляхом інверсії якої виходить інверсна МДНФ заданої функції F.

Перетворення отриманої МДНФ відбувається так, щоб

представити її у вигляді комбінації операцій, що виконуються базовими елементами, на яких буде реалізований проектований пристрій. Базові елементи найчастіше виконують функції І-НІ, АБО-НІ, І-АБО-НІ. При цьому перетворення МДНФ виконується наступним чином.

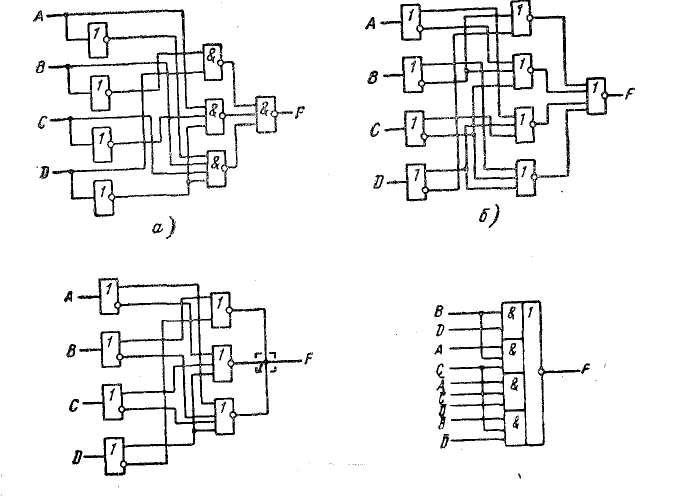

При реалізації на елементах І-НІ отримана МДНФ перетворюється в інверсно-кон׳юнктивну форму за допомогою подвійної інверсії та перетворення інверсії диз'юнкції імплікант у кон׳юнкцію їхніх інверсій за допомогою теореми де Моргана. Наприклад:

f=bd+acd+abcd=bd*acd*abcd.

B результаті отримано вираз, що містить тільки операції І-НІ, що безпосередньо реалізується логічною схемою з відповідним чином з'єднаних елементів І-НІ(рис.9.1,а)

При реалізації на елементах АБО-НІ використається інверсна МДНФ, що перетворюється в інверсно-диз'юнктивну форму шляхом подвійної інверсії кожної імпліканти та перетворення їх у диз'юнкцію вхідних змінних або їхніх інверсій за допомогою теореми де Моргана. Наприклад:

F =

BD+

ABC+ACD+ BCD =BD*АВС*ACD*DCD

=

BD+

ABC+ACD+ BCD =BD*АВС*ACD*DCD

В отриманому логічному виразні містяться тільки операції АБО-НІ, тому він реалізується логічною схемою з елементів АБО-НІ (рис.11.1,6).

Якщо при об'єднанні виходів елементів АБО-НІ виконується операція «Монтажне» АБО, то в якості вихідної використається МДНФ функція, імпліканти якої перетворюються в інверсії диз'юнкцій (диз׳юнктивно-інверсна форма за допомогою подвійної інверсії та перетворення де Моргана.

Відповідна логічна схема показана на рисунку11.1,в.

При реалізації на елементах І-АБО-НІ також використовується інверсна МДНФ, що безпосередньо виконується одним елементом даного типу (рис. 11.1,г).

в) г)

Рисунок 9.1. – Реалізація комбінаційної схеми на елементах І-НІ

(а), АБО -НІ (б), АБО-НІ, «Монтажне» АБО (в), І-АБО-НІ (г)

Після перетворення МДНФ виконується синтез логічної схеми шляхом відповідного з'єднання обраних логічних елементів, на входи яких подаються логічні змінні або їхні інверсії. Якщо необхідні інверсії змінних не поступають від попередніх логічних схем, то на вході проектованого вузла або блоку додатково включається каскад інверторів (рис. 11.1,а). Часто вхідні каскади виконують функції інверторів-повторювачів, змінні на виходах яких представляються як в інверсному, так і в прямому вигляді (рис. 11.1,6,в). Включення таких каскадів знижує вимоги до навантажувальної здатності попередніх схем. Ці каскади можуть також служити як транслятори логічних рівнів, забезпечуючи захист від вхідних перешкод та дозволяючи використовувати для реалізації логічних функцій більш швидкодіючі елементи.

Виходячи з викладеного, будь-яка логічна функція може бути реалізована за допомогою двох послідовно з'єднаних каскадів з елементів І-НІ чи АБО-НІ (рис.11.1). Число елементів у першому каскаді та відповідно число входів елементів у другому каскаді дорівнює числу імплікант у МДНФ або інверсної МДНФ. Число входів елементів першого каскаду дорівнює числу змінних, що входять у ці імпліканти. Для виконання заданої функції можуть знадобитися елементи з більшим числом входів М, тоді як логічні елементи бібліотек для проектування ВІС, зазвичай мають М = 4...5. Щоб реалізувати такі функції, необхідно виконати декомпозицію МДНФ або інверсної МДНФ.

При компонентній реалізації синтезується оригінальна електрична схема всього вузла, що проектується, або елементів, що входять у його склад. При синтезі можна використати метод струмових графів. В результаті для кожного отриманого варіанта МДНФ створюється кілька варіантів реалізації електричної схеми.

Таким чином, на даному етапі звичайно формуються декілька схемотехнічниих варіантів вузла, що проектується.

Аналіз синтезованих схем виконується з метою перевірки відповідності їх параметрів вимогам технічного завдання та вибору найбільш вдалого схемного варіанта. На даному етапі визначаються основні характеристики отриманих схем (у першу чергу споживана потужність і затримка перемикання), а також перевіряється виконання наведених у технічному завданні обмежень на такі параметри, як завадостійкість, коефіцієнт розгалуження, робочий діапазон температур і напруг живлення.