- •Севастопольский национальный технический университет

- •Часть 2 "Архитектура компьютеров"

- •Севастополь

- •Содержание

- •"Структурная схема микропроцессорного модуля и блок центрального процессора"

- •1. Цели занятия

- •2. Основные теоретические положения.

- •3. Программа занятия

- •Примеры типовых схем мп систем

- •5. Контрольные вопросы

- •"Оперативные запоминающие устройства статического и динамического типов"

- •1. Цели занятия

- •2. Основные теоретические положения.

- •3. Программа занятия

- •Примеры подключения зу к шинам мп системы

- •Контрольные вопросы

- •"Подключение устройств ввода/вывода данных"

- •1. Цели занятия

- •2. Основные теоретические положения.

- •3. Программа занятия

- •Примеры подключения и программирования интерфейсных схем

- •Контрольные вопросы

- •"Режимы прерывания и прямого доступа к памяти"

- •1. Цели занятия

- •2. Основные теоретические положения.

- •3. Программа занятия

- •4. Примеры типовых схем мп систем

- •5. Контрольные вопросы

- •6. Рекомендуемая литература

Примеры типовых схем мп систем

На рисунке 1.3 изображена схема типового микропроцессорного модуля, который позволяет ему работать во всех режимах, т.е. программно-управляемом, прямого доступа в память и обслуживания прерываний, а также осуществлять обмен данными с внешними устройствами, как в последовательном, так и в параллельном (побайтном) виде. Для этого в модуль введены соответствующие контроллеры прямого доступа в память (ПДП) и прерываний и последовательный и параллельный адаптеры связи.

|

Рисунок 1.3 – Схема универсального МП модуля

|

Выбор сигналов внешних устройств, по которым производится прерывание выполнения текущей программы процессора, осуществляется разработчиком микропроцессорной системы. Такими сигналами могут быть, например, сигналы готовности внешнего устройства, запроса передачи от модема, заполнения регистра приема последовательного интерфейса, отсутствия бумаги в принтере, сигнал ошибки и пр.

5. Контрольные вопросы

Назовите управляющие сигналы микропроцессора и их назначение.

Поясните детально работу микропроцессорного модуля в различных режимах работы: программно-управляемом, прямого доступа в память и обслуживания прерываний.

С какой целью на микропроцессор подают несколько тактовых сигналов в течение одного тактового интервала?

Поясните физику работы цепочки, формирующей сигнал сброса.

Можно ли в генераторе тактовых импульсов заменить кварцевый резонатор каким либо другим, более дешевым элементом и почему этого не делают?

Что представляет собой системный контроллер МП модуля и каковы его функции?

С какой целью в МП системах применяют шинные формирователи?

В чем состоит различие шинных формирователей в МП системах на основе процессоров 8080 и 8086?

Практическое занятие 2

"Оперативные запоминающие устройства статического и динамического типов"

1. Цели занятия

Углубление и закрепление полученных теоретических знаний по способам организации памяти в ЭВМ, способов подключения к процессорам ПЗУ и ОЗУ статического и динамического типов, получение практических навыков программирования процедур на языке ассемблера тестирования ПЗУ и ОЗУ.

2. Основные теоретические положения.

Основная память компьютера состоит из запоминающих устройств (ЗУ) двух видов – оперативного (ОЗУ) и постоянного (ПЗУ). ОЗУ предназначено для хранения переменных данных, допуская модификацию своего содержимого в ходе выполнения процессором вычислительных операций. ОЗУ может работать в режимах записи, хранения и чтения информации.

Постоянное ЗУ содержит информацию, которая не изменяется в процессе выполнения программы, а также не исчезает после выключения питания.

В современных вычислительных системах для построения ОЗУ и ПЗУ наиболее часто применяются полупроводниковые интегральные микросхемы. Микросхемы ОЗУ по типу используемых элементов памяти (ЭП) делятся на статические и динамические. В статических ОЗУ в качестве ЭП применяются статические триггеры на МДП-транзисторах (реже применяются триггеры на биполярных транзисторах). В микросхемах динамического ОЗУ элементы памяти выполнены на основе электрических конденсаторов, сформированных внутри полупроводникового кристалла. Такие ЭП не могут долгое время сохранять заряд, который неизбежно уменьшается ввиду наличия тока утечки. Поэтому ДОЗУ нуждаются в периодическом восстановлении информации (регенерации). В английской транскрипции оперативные ЗУ с произвольным доступом обозначаются RAM (Random Access Memory), а динамические ОЗУ − DRAM.

Микроконденсатор в интегральном исполнении занимает площадь значительно меньше D-триггера статической памяти. По этой причине, при одинаковых размерах кристалла, информационная емкость DRAM выше, чем у RAM. Из-за большой емкости ДОЗУ им требуется больше адресных линий, что привело бы к существенному увеличению габаритных размеров корпуса микросхемы ДОЗУ. Чтобы не допустить этого, адресные линии внутри микросхемы разбиваются на две группы. Адрес ячейки памяти подается в ДОЗУ последовательно двумя половинами по одним и тем же линиям в сопровождении управляющих сигналов RAS\ (строб адреса строки) и CAS\ (строб адреса столбца). Поэтому адрес на системной шине, формируемый МП, должен мультиплексироваться, одновременно вырабатываться управляющие сигналы RAS и CAS. Микросхема ДОЗУ будет выбрана только при условии RAS = CAS = 0. Структурно ДОЗУ состоит из матрицы накопителя, состоящей их элементов памяти, регистра адреса, дешифраторов адресов строк и столбцов, усилителей считывания и регенерации, усилителей ввода/вывода и схемы управления.

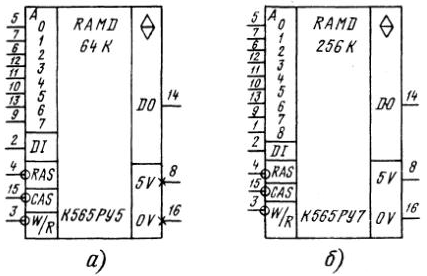

Первые БИС динамических ОЗУ имели однобитовую организацию (рисунок 2.1) и для построения 8-битового ОЗУ использовалось 8 микросхем однобитовых ДОЗУ, для 16-битового – 16 и т.д. Одноименные адресные линии однобитовых микросхем, а также линии RAS и CAS соединялись параллельно, а выходные и входные линии данных использовались для передачи соответствующих разрядов слова.

-

Рисунок 2.1 – Схемы одноразрядных БИС динамических ОЗУ

на 64 кбита (а) и 256 кбита (б)

В режиме регенерации ДОЗУ работает по циклу "считывание-модификация-запись", находясь при этом отключенной от входной и выходной шин данных благодаря сигналу CAS=1. В этом случае адресованными оказываются только строки и регенерация информации происходит во всех ячейках памяти строки матрицы ДОЗУ. Для перезаписи ячеек ОЗУ достаточно перебирать строку за строкой и выполнять «фиктивную» (без вывода данных на магистраль данных памяти) команду чтения. В этом случае каждая ячейка строки перезапишется через схему предзаряда, а данные не попадут в буферы выхода данных. На модификацию ячейки при считывании расходуется два такта синхронизации. Для сокращения времени регенерации уменьшают число строк, реализуя накопители на неквадратных матрицах,

Во время регенерации микросхема ДОЗУ закрыта для обращения. Это время составляет несколько процентов от общего времени работы микросхемы памяти. Для надежного хранения информации необходимо производить регенерацию по всему диапазону строк с периодом не более 2 мс.

Из изложенного следует, что использование динамического ОЗУ требует довольно сложной схемы управления. Если учесть, что обращение к ОЗУ со стороны процессора и обращение со стороны схемы регенерации не зависят друг от друга, следовательно, могут возникать одновременно, то необходима схема, обеспечивающая упорядоченность этих обращений. Для этих целей существуют схемы, управляющие работой динамических ОЗУ − контроллеры динамического ОЗУ, реализованные в виде одной микросхемы. Их использование позволяет значительно упростить построение памяти на динамических ОЗУ. Контроллер динамической памяти обеспечивает мультиплексирование адреса системной шины, выработку нескольких управляющих сигналов CAS и RAS (для селекции модулей ДОЗУ), а также внутреннюю (по таймеру) или внешнюю регенерацию.