- •Схемотехника и мп техника

- •Понятие адресного пространства. Совмещенные и параллельные адресные пространства: основные архитектурные и схемотехнические признаки.

- •Клавиатурные алгоритмы: варианты алгоритмов с указанием особенностей и применения.

- •1.2.3 Многоклавишные алгоритмы

- •Iord#. Данные из порта считываются процессором во внутренний шинный буфер.

- •Input/output) с успехом применяются и в интерфейсе ide (ata). Эти режимы используют инструкции

- •Ввод/вывод в режиме прямого доступа к памяти (пдп) (dma): схемотехнические особенности для различных архитектур системы. Области применения режима.

- •Аппаратные реализации шины для интерфейса «Токовая петля 20 мА». Особенности построения и основные ограничения.

- •Xon/xoff. Если двунаправленный обмен не требуется, используют только одну линию данных, а для

- •Последовательная передача в асинхронном режиме: основные характеристики. Понятие стартового и стопового битов, их уровни. Назначение и устройство схемы автофазировки.

- •Виды модуляции, используемые в модемах: сравнительный анализ с точки зрения помехоустойчивости и скорости передачи.

- •2.2. Модели управляющих автоматов

- •2.3.2. Граф-схемы алгоритмов

- •2.3.3. Графы переходов

- •5.1. Программные модели автоматов

- •1 Case (англ.) — случай. Построения произвольной гса с последующим ее структурированием и

- •5.1.2. Использование конструкции s w I t c h при реализации

Iord#. Данные из порта считываются процессором во внутренний шинный буфер.

· Процессор генерирует шинный цикл записи в память, выставляя адрес ячейки и формируя сигнал

MEMWR#. Данные из внутреннего шинного буфера записываются в память.

· Эти шаги автоматически повторяются с изменением адреса памяти. Количество повторов

определяется содержимым регистра СХ, направление изменения адреса (инкремент-декремент) —

флагом DF. Во время передачи всего блока процессор занят.

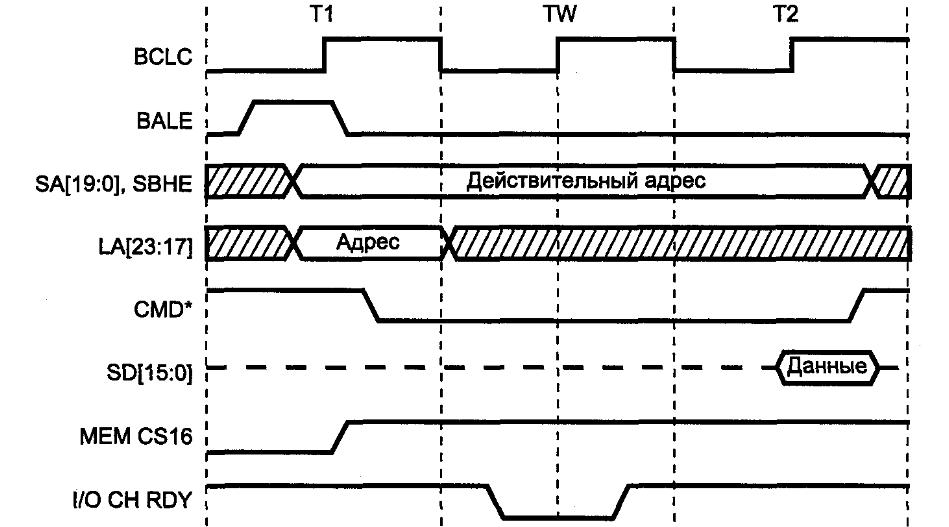

Обобщенные временные диаграммы циклов чтения или записи памяти или ввода/вывода

приведены на рис. 2.25. Здесь условный сигнал CMD* изображает один из сигналов:

· SMEMRD#, MEMRD# - в цикле чтения памяти;

· SMEMWR#, MEMWR# - в цикле записи памяти;

· IORD# - в цикле чтения порта ввода/вывода;

· IOWR# - в цикле записи порта ввода/вывода.

Сигнал BCLC соответствует сигналу Bclock, сигналы SA(19: 0) – сигналам Addr (19: 0) а сигналы

SD(15 : 0) – сигналам Data(15 : 0).

В каждом из рассматриваемых циклов активными (с низким уровнем) могут быть только сигналы

(сигнал) лишь из одной строки данного списка. (В циклах прямого доступа к памяти это правило не

соблюдается.) По адресованному ему спаду сигнала чтения устройство должно выдать на шину

данных содержимое адресуемой ячейки и удерживать его, пока не произойдет подъем данного

сигнала. Во время циклов записи процессор выставляет действительные данные несколько позже

начала (спада) сигнала записи, и устройство должно для себя фиксировать эти данные в конце цикла

по подъему сигнала записи. Обращение к портам ввода/вывода отличается тем, что сигналы LA[32:17]

не используются.

Рис. 2.25. Временные диаграммы циклов чтения или записи на шине ISA

Высокоскоростные режимы программного обмена PIO (Programmed

Input/output) с успехом применяются и в интерфейсе ide (ata). Эти режимы используют инструкции

блочной пересылки REP-INS/OUTS (используются в процессорах начиная с i80286), при которых

процессор способен пересылать байт или слово между портом и областью памяти, затрачивая

минимальное количество тактов системной шины. Скорость такого обмена превышает скорость

стандартного канала прямого доступа (DMA) Поскольку эту полную скорость периферийные

устройства воспринять обычно не могут, контроллер интерфейса «притормаживает» обмен до

разумных скоростей, определяемых режимом обмена. Параметры этих режимов, называемых PIO

Mode (Programmed input/output Mode — режимы программного ввода/вывода). В режимах 0, 1 и 2 синхронизация с устройством не предусматривается — считается, что оно

должно успевать. Старшие режимы, кроме указанных ограничителей скорости сверху, используют и

117

сигнал готовности от устройства. Режим PIO задается при инициализации контроллера интерфейса

АТА. Обмен в режиме PIO (Programmed Input/Output — программируемый ввод-вывод) выполн-

яется в виде следующих друг за другом операций чтения или записи в пространстве ввода-

вывода по адресу регистра данных. Традиционные режимы 0, 1 и 2 имеют временные пара-

142

метры, задаваемые только хост-адаптером. Для прогрессивных режимов АТА-2 (PIO Mode 3

и выше) устройство может затормозить обмен сигналом готовности IORDY. Программный

обмен на все время передачи блока занимает и процессор, и шину ИВВ хоста.

Ввод/вывод в режиме прерываний: схемотехнические особенности формирования запроса.

Программный ввод-вывод с прерываниями программы является основным способом

организации ввода-вывода в ПЭВМ, мини- и микроЭВМ для ПУ малого и среднего быстродействия.

Для синхронизации процессов в ЦП и ПУ используется механизм прерываний, а управление

передачами данных и управляющей информации для ПУ осуществляется программно. Данные

передаются между регистрами ПУ и ЦП; пересылку данных в ОП осуществляет ЦП по адресу,

который он определил при выполнении программы драйвера. После выполнения каждой команды в

ЦП (рис. 3.4) производится анализ запроса прерываний, а при его наличии проверяется — разрешено

ли данное прерывание. При наличии разрешенного прерывания ЦП инициирует его обслуживание.

Маскирование прерываний позволяет защищать от прерываний так называемые критические

секции программы пользователя, т.е. такие участки программы, на выполнение которых не должно

оказывать влияние изменение содержимого памяти, вызываемое процессом ввода.

Запрос прерывания может формироваться не только ПУ, но и по специальной команде ЦП. Все

запросы прерываний обрабатываются последовательно в соответствии с приоритетами. При

инициировании обработки прерываний вначале определяется источник запроса; если источником

запроса прерываний является ПУ, то управление передается соответствующему драйверу.

Существует несколько способов определения, от какого ПУ поступил запрос на прерывание; эти

способы сводятся к различным вариантам аппаратного и программного опроса ПУ. В результате

такого опроса программе обработки прерываний становится доступным адрес ПУ, по которому

вычисляется начальный адрес программы-драйвера; ей и передается управление. С этой целью в

большинстве микроЭВМ и ПЭВМ для каждого ПУ в основной памяти предусматривается по две

ячейки, хранящие векторы прерываний. Совокупность этих ячеек для всех ПУ образует область

«векторов». Вектор прерывания однозначно определяется адресом ПУ. В его ячейках хранится адрес

перехода к программе-драйверу для обслуживания данного ПУ а ,иногда информация о состоянии

программы и возврата. При программном вводе-выводе каждое прерывание позволяет передать между

ОП и ПУ один байт или одно слово данных. Параллельная работа ЦП и ПУ происходит только в

интервале между прерываниями. Обработка прерываний приводит к большим непроизводительным

затратам времени ЦП, что не позволяет использовать такую организацию ввода-вывода для быстрых

ПУ.