- •Схемотехника и мп техника

- •Понятие адресного пространства. Совмещенные и параллельные адресные пространства: основные архитектурные и схемотехнические признаки.

- •Клавиатурные алгоритмы: варианты алгоритмов с указанием особенностей и применения.

- •1.2.3 Многоклавишные алгоритмы

- •Iord#. Данные из порта считываются процессором во внутренний шинный буфер.

- •Input/output) с успехом применяются и в интерфейсе ide (ata). Эти режимы используют инструкции

- •Ввод/вывод в режиме прямого доступа к памяти (пдп) (dma): схемотехнические особенности для различных архитектур системы. Области применения режима.

- •Аппаратные реализации шины для интерфейса «Токовая петля 20 мА». Особенности построения и основные ограничения.

- •Xon/xoff. Если двунаправленный обмен не требуется, используют только одну линию данных, а для

- •Последовательная передача в асинхронном режиме: основные характеристики. Понятие стартового и стопового битов, их уровни. Назначение и устройство схемы автофазировки.

- •Виды модуляции, используемые в модемах: сравнительный анализ с точки зрения помехоустойчивости и скорости передачи.

- •2.2. Модели управляющих автоматов

- •2.3.2. Граф-схемы алгоритмов

- •2.3.3. Графы переходов

- •5.1. Программные модели автоматов

- •1 Case (англ.) — случай. Построения произвольной гса с последующим ее структурированием и

- •5.1.2. Использование конструкции s w I t c h при реализации

Схемотехника и мп техника

ОЭВМ (MCS), ЦСП (DSP), ПСНК (PSoC). Основные признаки и характеристики, области применения.

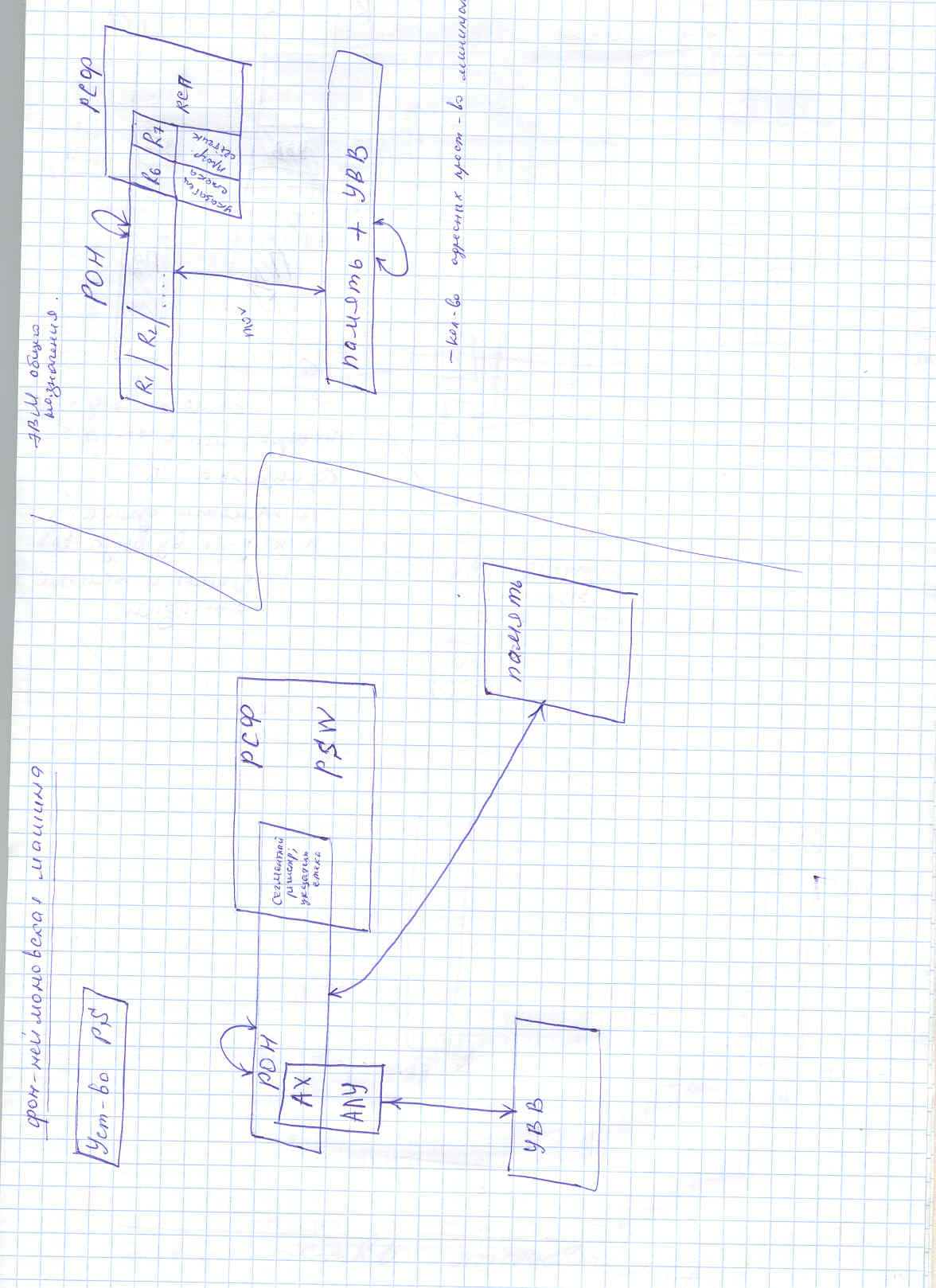

IBM PS – микропроцессорное устройство

Отдельная микросхема – процессор

Набор дополнительных микросхем (все микросхемы отдельно – есть объем

- состав меняется

Микроконтроллер – однокристальная ЭВМ

ОЭВМ = MCS, когда надо чем-то управлять.

Первый процессор сделал Intel

Архитектура MCS-51, MCS-52

Микропроцессор – построенное на одном кристалле программно-управляемое устройство, осуществляющее процесс обработки информации и управление им. Микропроцессоры появились, когда микросхемы приобрели уровень интеграции, при котором набор блоков, необходимых для программной реализации алгоритмов, удалось разместить на одном кристалле. Первый микропроцессор содержал 2300 транзисторов, работал на тактовой частоте 100 кГц и выполнял команду в среднем за 10 тактов. Современные микропроцессоры содержат до миллиардов транзисторов, работают на гигагерцовых частотах и выполняют команды за один такт или даже быстрее.

Программа реализуется микропроцессорной системой, основными частями которой являются:

- Микропроцессор;

- Память;

- Интерфейсные схемы и контроллеры для взаимодействия с внешними устройствами.

Соответственно областям применения целесообразно выделить классы:

- простые микропроцессоры;

- сложные микропроцессоры высокой производительности.

Первый класс ориентирован на применение в системах управления техническими объектами и технологическими процессами, причем чаще всего в качестве встроенных блоков. Микроконтроллер – объединение в одной микросхеме микросхемы процессора и дополнительные микросхемы – энергозависимая и оперативная память, порты ввода/вывода, аналогово-цифровые и цифроаналоговые преобразователи и т.д. (удобнее, где речь идет о встраиваемой технике) - удобно для измерительных приборов. Сложные микропроцессоры высокой производительности с разрядностью 32 или 64 разрядов характерны для универсальных компьютеров. На универсальных компьютерах решаются разнообразные задачи, в том числе требующие большой вычислительной мощности. Это ведет к усложнению архитектур процессоров, введению параллелизма вычислений, кэшированию памяти, усложнению шинных структур и т.д. Система в целом реализуется на нескольких кристаллах. В частности, основной процессор стали дополнять сопроцессором (в первую очередь для арифметики с плавающей точкой). Построены на БИС /СБИС. Основные архитектуры процессоров ОМК

В современных ОМК применяются следующие архитектуры процессоров :

RISC — (Reduced Instruction Set Computer) – процессор из которого убрали все команды которые выполняются больше чем один такт.

- минимум 16 регистров

- быстродействие (за счет того, что убрали некоторые команды)

CISC — (Complex Instruction Set Computer) традиционная архитектура с расширенным набором команд.

DSP (Цифровой сигнальный процессор) – сплошной поток данных, одинаковая операция

Блоки DSP (Digital Signal Processing) содержат большое число умножителей, сумматоров/вычислителей и аккумуляторов, благодаря чему при обработке сигналов достигается высокий уровень параллелизма и, соответственно, производительности. К основным направлениям обработки сигналов относятся: фильтрация, спектральный анализ, нелинейные преобразования.

Типы сигналов. В теоретических исследованиях и технике применяются сигналы трех типов:

- аналоговые;

- дискретные;

- цифровые.

В системах DSP аналоговые сигналы являются входными, поступающими от физических объектов, или выходными, поступающими на такие объекты. Аналоговый сигнал характеризуется непрерывностью существования. В любой момент времени можно считывать значение сигнала, причем оно может принимать любые значения в пределах диапазона от минимума до максимума.

Дискретный сигнал, соответствующий аналоговому, отображается совокупностью отчетов, взятых через равные интервалы времени (имеется в виду равномерная дискретизация, применяются и более сложные ее виды).

В цифровом сигнале отсчеты выражаются числами ограниченной разрядности и, следовательно, соответствуют аналоговым значениям лишь приближенно.

Структура DSP-блока

Рассмотрим DSP-блоки микросхемы Stratix фирмы Altera. Эти блоки сгруппированы на кристалле в два столбца. Каждый блок находится в окружении массива программируемой логики, которая может быть использована для дополнительных операций при построении устройств из нескольких блоков. У разных представителей семейств от 6 до 28 блоков. Блоки DSP могут выполнять операции умножения с возможностью накопления (суммирования) или вычитания результатов при разрядностях операндов 9, 18, или 36. При размерности 9х9 можно реализовать в одном блоке до 8 умножителей, при 18х18 – четыре и при 36х36 – один. Суммарно в старшей микросхеме может быть создано до 224 умножителей размерностью 9х9. Блоки DSP дают по 2*109 операций умножения-накопления в секунду, и если использовать все 28 блоков старшего представителя семейства, то будет достигнута вычислительная мощность в 56*109 операций MAC в секунду. Блоки содержат также 18-разрядные сдвигающие регистры. Максимальная частота работы блоков составляет 250 МГц. На вторые входы умножителей должны подаваться значения коэффициентов, взвешивающих отсчеты. Эти коэффициенты загружаются в нижние регистры каналов, причем загрузка может производиться последовательно (сверху-вниз через нижние регистры каналов) или параллельно, поскольку все регистры имеют и входы параллельной загрузки. В пределах одного блока при 18-разрядных операндах реализуются 4 умножителя и ассоциированные с ними схемы. Результаты умножений поступают далее на блоки суммирования/вывода, состоящие из сумматоров/вычитателей/аккумуляторов, суммирующих схем, мультиплексоров выбора выхода и выходных регистров. Архитектура сигнальных процессоров, по сравнению с микропроцессорами настольных компьютеров, имеет некоторые особенности:

Гарвардская архитектура (разделение памяти команд и данных), как правило модифицированная;

Большинство сигнальных процессоров имеют встроенную оперативную память, из которой может осуществляться выборка нескольких машинных слов одновременно. Нередко встроено сразу несколько видов оперативной памяти, например, в силу Гарвардской архитектуры бывает отдельная память для инструкций и отдельная — для данных.

Некоторые сигнальные процессоры обладают одним или даже несколькими встроенными постоянными запоминающими устройствами с наиболее употребительными подпрограммами, таблицами и т. п.

Аппаратное ускорение сложных вычислительных инструкций, то есть быстрое выполнение операций, характерных для цифровой обработки сигналов, например, операция «умножение с накоплением» (MAC) (Y := X + A × B) обычно исполняется за один такт.

«Бесплатные» по времени циклы с заранее известной длиной. Поддержка векторно-конвейерной обработки с помощью генераторов адресных последовательностей.

Детерминированная работа с известными временами выполнения команд, что позволяет выполнять планирование работы в реальном времени.

Сравнительно небольшая длина конвейера, так что незапланированные условные переходы могут занимать меньшее время, чем в универсальных процессорах.

Экзотический набор регистров и инструкций, часто сложных для компиляторов. Некоторые архитектуры используют VLIW.

По сравнению с микроконтроллерами, ограниченный набор периферийных устройств — впрочем, существуют «переходные» чипы, сочетающие в себе свойства DSP и широкую периферию микроконтроллеров. Области применения

Коммуникационное оборудование:

Уплотнение каналов передачи данных;

Кодирование аудио- и видеопотоков;

Системы гидро- и радиолокации;

Распознавание речи и изображений;

Речевые и музыкальные синтезаторы;

Анализаторы спектра;

Управление технологическими процессами;

Другие области, где необходима быстродействующая обработка сигналов, в том числе в реальном времени. Основные параметры ЦСП

Тип арифметики. ЦСП делятся на процессоры, обрабатывающие данные с фиксированной точкой и обрабатывающие данные с плавающей точкой. Устройства с плавающей точкой удобнее в применении, но они заметно сложнее по устройству и более дороги;

Разрядность данных. Большинство ЦСП с фиксированной точкой обрабатывают данные с разрядностью 16 бит, процессоры с плавающей точкой — 32 бита. Многие модели могут обрабатывать данные с двойной точностью.

Быстродействие. Быстродействие как интегральную характеристику определить достаточно сложно, поэтому скорость работы характеризуют несколькими параметрами, а также временем решения некоторых реальных задач.

Тактовая частота и Время командного цикла. Для современных ЦСП тактовая внутренняя частота может отличаться от внешней, поэтому могут указываться два значения. Время командного цикла указывает на время выполнения одного этапа команды, то есть время одного цикла конвейера команд. Так как команды могут исполняться за разное количество циклов, а также с учётом возможности одновременного исполнения нескольких команд, этот параметр может характеризовать быстродействие ЦСП достаточно приближённо.

Количество выполняемых команд за единицу времени. Различное время исполнения команд, а также исполнение нескольких команд одновременно не позволяют использовать этот параметр для надёжной характеристики быстродействия.

Количество выполняемых операций за единицу времени (MIPS). Данный параметр учитывает одновременную обработку нескольких команд и наличие параллельных вычислительных модулей, поэтому достаточно хорошо может указывать на быстродействие ЦСП. Некоторой проблемой здесь остаётся то, что понятие «операции» чётко не формализовано.

Количество выполняемых операций с плавающей точкой за единицу времени. Параметр аналогичен предыдущему и используется для процессоров с плавающей точкой.

Количество выполняемых операций MAC за единицу времени. Данная команда, с одной стороны, является базовой для многих вычислений, а с другой — достаточно проста. Поэтому время её исполнения можно использовать в том числе и для оценки общей производительности ЦСП.

Виды и объём внутренней памяти. Объём внутренней оперативной памяти показывает, сколько данных ЦСП может обработать без обращения к внешней памяти, что может характеризовать общее быстродействие системы а также возможность работать «в реальном времени». Тип ПЗУ определяет возможности по программированию устройства. Модели с обычным ПЗУ подходят для крупносерийного производства, ППЗУ (однократно программируемое) удобно для небольших тиражей, а применение Flash-памяти позволяет менять программу устройства многократно во время эксплуатации. На данный момент не очень мощные DSP чаще всего снабжены достаточно большой Flash-памятью (её цена неуклонно снижается) и заметным объёмом RAM и поэтому могут являться самодостаточными без добавления внешней памяти и на этапе разработки и на этапе производства, что повышает конкурентоспособность таких DSP в ряде сегментов рынка. Мощные DSP как правило полагаются на внешнюю память подключённую по достаточно быстрым шинам а размещение там Flash-памяти может быть технически проблематичным, например, из-за заметного выделения тепла.

Адресуемый объём памяти. Объём адресуемой внешней памяти характеризуется шириной внешней шины адреса.

Способ начальной загрузки.

Количество и параметры портов ввода-вывода. Данный параметр показывает возможности ЦСП по взаимодействию с внешними по отношению к нему устройствами.

Состав внутренних дополнительных устройств. В число внутренних могут входить разнообразные по назначению устройства, например, общего применения — таймеры, контроллеры ПДП и т. д., а также проблемно-ориентированные — АЦП, кодеки, компрессоры данных и другие.

Напряжение питания и потребляемая мощность. Данная характеристика особенно важна для ЦСП, встраиваемых в переносные устройства. Обычно предпочтительнее низковольтные устройства (1,8-3,3В), которые имеют быстродействие аналогично 5В процессорам, но заметно экономнее в плане потребления энергии. Многие устройства имеют режимы экономии при простое, либо позволяют программно отключать часть своих устройств.

Состав и функциональность средств разработки и поддержки.

Перечень языков программирования, для которых есть компиляторы под данную систему;

Наличие и возможности средств отладки готовых программ;

Доступность документации и технической поддержки;

Наличие библиотек стандартных подпрограмм и математических функций;

Наличие, доступность и возможности совместимых устройств — АЦП, ЦАП, контроллеры питания и т. д.

Допустимые параметры окружающей среды.

Другие, в зависимости от назначения.

Часто используются также интегральные характеристики ЦСП, например показатель «мощность/ток/быстродействие», например ma/MIPS (миллиампер на 1 млн инструкций в секунду), что позволяет оценить реальную потребляемую мощность в зависимости от сложности задачи, решаемой процессором в указанный момент.

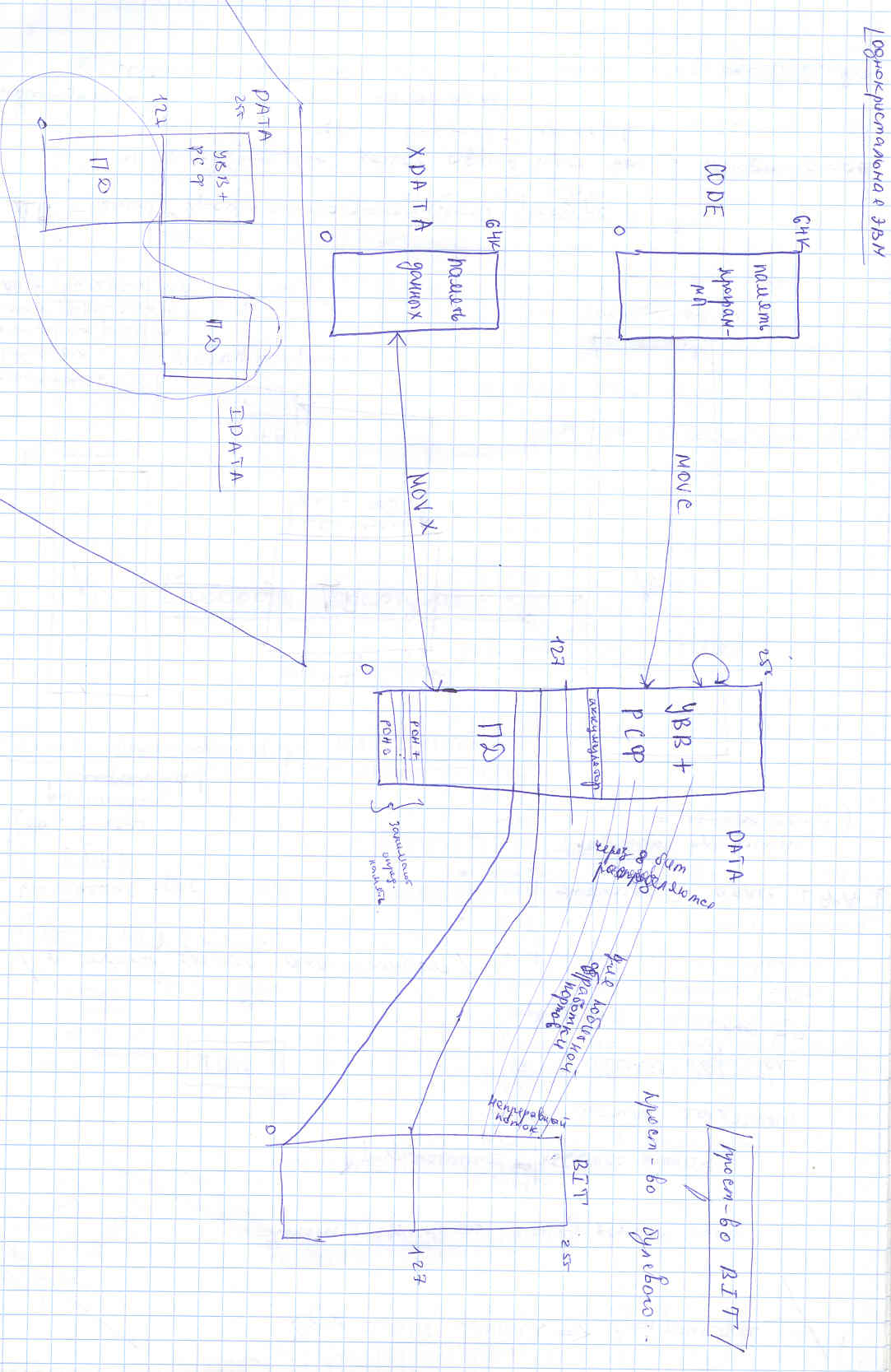

Выбор ЦСП целиком определяется назначением разрабатываемой системы. Например, для массовых мобильных устройств важна дешевизна процессора, низкое энергопотребление, в то время как стоимость разработки системы отходит на второй план. С другой стороны, для измерительного оборудования, систем обработки звуковой и видеоинформации важны эффективность процессора, наличие развитых инструментальных средств, многопроцессорность и т. д. Цифровые сигнальные процессоры строятся на основе т. н. «Гарвардской архитектуры», отличительной особенностью которой является то, что программы и данные хранятся в различных устройствах памяти — памяти программ и памяти данных. В отличие от архитектуры фон Неймана, где процессору для выборки команды и двух операндов требуется минимум три цикла шины, ЦСП может производить одновременные обращения как к памяти команд, так и к памяти данных, и указанная выше команда может быть получена за два цикла шины. В реальности, благодаря продуманности системы команд и другим мерам, это время может быть сокращено до одного цикла. В реальных устройствах память команд может хранить не только программы, но и данные. В этом случае говорят, что ЦСП построен по модифицированной гарвардской архитектуре.

Память команд и память данных обычно располагаются на кристалле ЦСП. В связи с тем, что эта память имеет относительно небольшой объём, возникает необходимость в использовании внешних (относительно кристалла процессора) запоминающих устройств. Для таких устройств раздельные шины команд и данных не используются, так как это потребовало бы значительно увеличить количество внешних выводов кристалла, что дорого и непрактично. Поэтому взаимодействие ЦСП с внешними запоминающими устройствами происходит по одному комплекту шин без разделения на команды и данные. Следует также заметить, что обращение к внешней памяти всегда занимает значительно больше времени, чем к внутренней, поэтому в приложениях, критичных ко времени исполнения, такие обращения необходимо минимизировать.

Пример DSP:

Функциональные параметры процессора 1892ВМ3T(МС-12):

Цифровой сигнальный процессор (DSP):

"Гарвардская" RISC - подобная архитектура с оригинальной системой команд и преимущественно однотактным исполнением инструкций;

SISD (Single Instructions Single Data) организация потоков команд и данных;

Стандартный набор инструкций, процедуры обработки и пересылки совмещаются;

3-ступенчатый конвейер по выполнению 32- и 64-разрядных инструкций;

Расширенные возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой, либо в одном из форматов с плавающей точкой - 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат). Обеспечение при этом компромиссного выбора между точностью и производительностью. Аппаратные меры повышения точности и динамического диапазона (блочная плавающая точка; режим насыщения; инструкции преобразования форматов);

Аппаратная поддержка программных циклов;

Память программ PRAM объемом 16 Кбайт;

Двухпортовые памяти данных XRAM и YRAM объемом 96 и 48 Кбайт соответственно;

Пиковая производительность DSP:

240 млн. оп/с 32-битных операций с плавающей точкой (IEEE 754);

1440 млн. оп/с 8-битных операций с фиксированной точкой;

640 млн. оп/с 16-битных операций с фиксированной точкой;

320 млн. оп/с 32-битных операций с фиксированной точкой.

Порт внешней памяти (MPORT):

Шина данных - 32 разряда, шина адреса - 32 разряда;

Встроенный контроллер управления статической памятью типа SRAM, FLASH, ROM, а также синхронной памятью типа SDRAM;

Программное конфигурирование типа памяти и объема ее сегмента;

Программное задание циклов ожидания;

Формирование сигналов выборки 4 сегментов памяти;

Обеспечение обслуживания 4 внешних прерываний.

Периферийные устройства:

12 - канальный контроллер прямого доступа в память (DMA). 4 внешних запроса прямого доступа. Специальные режимы синхронизации. Поддержка 2-мерной и разрядно-инверсной адресации. Режим передачи Flyby, подобный реализованному в ADSP-TS201: внешнее устройство - внешняя память;

два порта обмена последовательным кодом (SPORT) совместимые с ADSP21160 (разработка фирмы ADI);

четыре линковых порта (LPORT) совместимые с ADSP21160. Имеется режим работы в качестве портов ввода-вывода общего назначения (GPIO);

универсальный асинхронный порт (UART) типа 16550;

32-разрядный интервальный таймер (IT);

32-разрядный таймер реального времени (RTT);

32-разрядный сторожевой таймер (WDT).

Дополнительные возможности и особенности:

Узел фазовой автоподстройки частоты (PLL) c умножителем/делителем входной частоты;

Встроенные средства отладки программ (OnCD);

Порт JTAG в соответствии со стандартом IEEE 1149.1;

Рассеиваемая мощность, мВт, около 1200 (максимальная); режимы энергосбережения: 700 - при неработающем DSP-ядре (режим Stop); 70 - при программном уменьшении тактовой частоты в 16 раз; 30 - при программном отключении тактовой частоты (включение тактовой частоты осуществляется по внешним прерываниям);

Корпус: пластиковый корпус PQFP-240.

«Система на кристалле» (СНК или SOC) = MCS+ DSP – это узкоспециализированная микросхема (пример, чип банковской карты, зональный пропуск, карточка в метро)

«Программируемая система на кристалле»(PSOC)

Термин «система на кристалле» появился применительно к мегавентильным микросхемам, поскольку на них можно разместить целую систему (процессор, память, интерфейсные схемы и др.). «Программируемые системы на кристале» выпущены около 10 лет назад. Их современные варианты содержат уже десятки-сотни миллионов эквивалентных вентилей (миллиарды транзисторов), а их тактовые частоты составляют сотни мегагерц/ или даже превышают гигагерц. Системы на одном кристалле имеют улучшенные технические и экономические качественные показатели. Интеграция функциональных блоков в одном кристалле повышает быстродействие и надежность систем, уменьшает потребляемую ими мощность и стоимость.

IP-ядра. Блочное и платформенное проектирование

IP-блоки для схем программируемой логики могут быть представлены в разной форме. Различают варианты:

- soft-ядра – это файлы, определяющие конфигурирование некоторой области кристалла таким образом, что в ней создается устройство заданного типа. Эти файлы можно интегрировать в описание проектируемого устройства на языке HDL(Hardware Description Language);

- firm-ядра – это вариант, близкий к предыдущему, его применяют для блоков, быстродействие которых особенно важно. В этих ядрах задание схемы является более жестким, чем в файле поведенческого описания, свойственного soft-ядрам, поскольку в описании firm-блока предопределены некоторые схемные межсоединения;

- hard-ядра представляют собой реализованные на кристалле области с фиксированными функциями(устройства).

Типы программируемых «систем на кристалле»

Все программируемые «системы на кристалле» подобны друг другу тем, что синтезируются с помощью ядер. Из практических соображений целесообразно выделить два типа PSOC:

- однородные

- блочные

Системы однородного типа. Это системы на микросхемах высшей сложности и производительности, в которых применяются преимущественно soft-ядра, реализуемые схемотехнически однотипными ресурсами в тех или иных областях кристалла благодаря их программируемости. Такие системы ориентированы главным образом на телекоммуникации, сетевые приложения, обработку изображений и речи и другие мультимедийные задачи. Эти системы назовем однородными, имея в виду идентичность логических ресурсов, размещенных на кристалле и применяемых для построения требуемых устройств.

Системы блочного типа

Это системы умеренной сложности и производительности, ориентированные на задачи управления техническими объектами и технологическими объектами и технологическими процессами. В таких системах наряду с синтезируемыми ядрами широко применяются hard-ядра, т.е. на кристалле выделяются области с фиксированными функциями, не содержащие средств программирования структуры. С учетом структуры эти системы можно назвать блочными. Кроме того, согласно главной области применения подобные системы можно назвать микроконтроллерными. Программируемая часть блочных PSOC обычно имеет архитектуру FPGA.

Системы на кристалле серии PSoC(Programmable System on Chip), в которых сочетаются конфигурируемые цифровые и аналоговые программируемые блоки. В серии PSOC выпущены три семейства: PSOC 1 с процессором M8C (тактовая частота 24 МГц), PSOC 3 с процессором 8051 (67 МГц) и PSOC 5 с процессором ARM Cortex-M3 (80 МГц). Семейство этой серии, обладающее архитектурными новшествами и большими возможностями относительно своих предшественников - PSOC 5. В этом семействе некоторые аналоговые компоненты, реализованные на кристалле, тем не менее обладают разрешающей способностью, соответствующей 20 двоичным разрядам, используемое 32-разрядное ядро процессора ARM Cortex-M3 работает на частоте до 80 МГц, схема потребляет ультранизкую мощность. Сочетание процессора с хорошо развитыми гибкими гибкими средствами аналоговой и цифровой обработки данных, а также обширными средствами их ввода-вывода, придает системе PSOC 5 широкую область применений в промышленных, потребительских, медицинских и других приложениях. Подсистема процессора строится вокруг 32-разрядного ядра ARM Cortex-M3 с трехступенчатым конвейером, работающего на частотах до 80 МГц. В подсистеме имеется контроллер вложенных векторных прерываний, контроллер прямого доступа к памяти (24 канала), а также контроллер флэш-кэша, который ускоряет работу с памятью, а также способствует снижению потребляемой мощности, благодаря более редким обращениям к основной флэш-памяти. Подсистема памяти снабжена устройствами типа программной памяти флэш (256 Кбайт), EEPROM с байтовой записью (2 Кбайта для пользовательских данных), SRAM (64 Кбайта). Подсистема отладки и программирования широко использует интерфейс JTAG (4 линии) или Serial Wire Debug (2 линии). Допустимая работы микросхемы от стандартных источников напряжений 1,8 В + 5%; 2,5 В+10%; 3,3 В + 10%; 5 В + 10% или непосредственно от батарей разных типов. Имеется встроенный конвертор, благодаря которому можно питать схему от источников столь малых напряжений, как 0,5 В, и вырабатывать нестандартные напряжения. Возможны четыре режима малого потребления мощности: активный ( с током потребления 2 мА при частоте тактирования 6 МГц), ожидания (с током 20 мкА и временем выхода в активный режим менее 1 мкс), спящий (2 мкА и менее 12 мкс) и hibernate (буквальный перевод – находящийся в зимней спячке) с параметрами 300 пА и менее 100 мкс).