- •Аналоговые и цифровые интегральные микросхемы

- •Введение

- •1. Технология изготовления интегральных микросхем

- •1.1. Общие сведения об интегральных микросхемах

- •1.2. Пленочные и гибридные интегральные микросхемы

- •1.3. Полупроводниковые интегральные микросхемы

- •2. Аналоговые Интегральные микросхемы

- •2.1. Основные сведения об операционных усилителях

- •Выводы операционного усилителя

- •2.3. Основные параметры операционных усилителей

- •2.4. Режим суммирующей точки

- •2.5. Повторитель напряжения

- •2.6. Неинвертирующий усилитель

- •2.7. Инвертирующий усилитель

- •2.8. Усилитель с дифференциальным входом

- •2.9. Усилитель с дифференциальным выходом (балансный)

- •2.10. Влияние отрицательной обратной связи на коэффициент усиления

- •2.11. Инвертирующий сумматор

- •2.12. Неинвертирующий сумматор

- •2.13 Интегратор

- •2.14. Дифференциатор

- •2.15. Схема логарифмического преобразователя

- •2.16. Схема умножения

- •2.17. Схема деления

- •2.18. Источники неизменного тока

- •2.19. Источники напряжения

- •2.20. Генератор колебаний прямоугольной формы

- •2.21. Генератор сигналов треугольной формы

- •2.22. Интегральные схемы стабилизаторов напряжения

- •2.22.1. Типы стабилизаторов напряжения

- •2.22.2. Линейные стабилизаторы напряжения последовательного действия (с переходным регулирующим элементом)

- •2.23. Специализированные интегральные схемы

- •2.23.1. Компараторы

- •2.23.2. Триггер Шмита

- •11.2. Токоразностный усилитель

- •2.25. Таймеры

- •2.26. Измерительные усилители

- •11.5. Изолирующие усилители

- •3.1.2. Параметры цифровых интегральных микросхем

- •3.2. Цифровые микросхемы транзисторно-транзисторной логики (ттл)

- •3.2.1. Основы схемотехники элементов ттл

- •3.3. Стандартные микросхемы серии ттл

- •3.4. Логические элементы

- •3.5. Триггеры

- •3.6. Мультивибраторы

- •3.7. Буферные элементы

- •3.8. Счетчики

- •3.9. Мультиплексоры

- •3.10. Регистры

- •3.11. Шифраторы и дешифраторы

- •3.12. Сумматоры

- •4. Микропроцессоры

- •4.1. Общие сведения о микропроцессорной технике

- •4.2. Классификация микропроцессоров

- •4.3. Основные характеристики микропроцессора

- •4.4. Структура типового микропроцессора

- •4.5. Логическая структура микропроцессора

- •Список используемой литературы

2.22.2. Линейные стабилизаторы напряжения последовательного действия (с переходным регулирующим элементом)

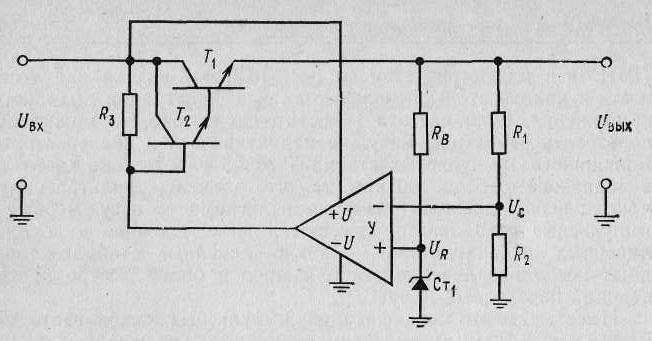

На рис. 43 показана обычная схема стабилизатора напряжения последовательного действия.

Рис. 43. Стабилизатор последовательного действия.

Это схема с замкнутой обратной связью. Здесь Т1 представляет собой проходной регулирующий транзистор, Т2 выполняет роль усилителя тока для Т1. Так как большинство мощных, последовательно включаемых транзисторов имеет довольно малое значение h21Э (порядка 20 – 30), то транзисторы Т1 и Т2 включены по схеме Дарлингтона. Выход транзистора Т1 на нагрузку берется с эмиттера, так что Т1 и Т2 обеспечивают усиление по току, а не по напряжению. Резисторы R1 и R2 образуют делитель напряжения, с которого снимается часть выходного стабилизируемого напряжения Uвых. Это напряжение сравнивается с опорным (Uоп), получаемым от стабилитрона (Ст) с помощью ОУ. Входное напряжение ОУ представляет собой разность между опорным напряжением и напряжением U*вых:

U*вх = Uоп – U*вых = UСт – U*вых [R2 /(R1 + R2)]. (20)

Это напряжение U*вх усиливается усилителем и воздействует на проходной транзистор так, чтобы скорректировать любые изменения выходного напряжения, возникающие как под влиянием изменения входного напряжения, так и тока нагрузки. Стабилизаторы последовательного действия работают следующим образом: если Uвых уменьшается либо под влиянием уменьшения Uвх, либо увеличения тока нагрузки, то U*вых также уменьшается, а Uоп остается постоянным. Разность Uоп – U*вых возрастает, поскольку напряжение на инвертирующем входе ОУ становится отрицательным по отношению к Uоп. Выходное напряжение ОУ становится положительным, что вызывает изменение напряжения на эмиттерах Т1 и Т2 в положительном направлении до тех пор, пока не восстановится приближенное равенство U*вых ≈ Uоп. Последнее будет иметь место в случае, когда Uвых достигнет значения, которое было до изменения нагрузки или входного напряжения. Выходное напряжение ОУ вызывает дополнительное отпирание Т1 и Т2, что в свою очередь приводит к такому увеличению тока нагрузки, которое компенсирует падение Uвых. При этом напряжение коллектор – эмиттер UКЭ Т1 уменьшается и таким образом компенсирует снижение выходного напряжения. В случае, когда Uвх возрастает или Iн уменьшается, процесс в системе протекает в обратном направлении.

Так как UКЭ Т1 = Uвх – Uвых и весь ток нагрузки протекает через Т1, то к. п. д. схемы непосредственно зависит от величины UКЭ Т1. Например, если стабилизатор напряжения последовательного действия обеспечивает 15 В стабилизированного напряжения при нестабилизированном входном напряжении 30 В, то максимальный к. п. д. = Рвых/Рвх = 50 %. Для получения высокого к. п. д. необходимо, чтобы разность Uвх – Uвых была по возможности меньшей, однако при этом существует предел. Для обеспечения линейности разность Uвх – Uвых должна быть больше, чем UБЭ Т1 + UБЭ Т2 + UКЭ Т1 мин. Для большинства мощных транзисторов напряжение UКЭ ≈ 2В достаточно для обеспечения линейности. Поэтому для надежной линейной работы Т1 и Т2 в линейном режиме необходимо, чтобы Uвх – Uвых ≥ 3,5 В. Нестабилизированное входное напряжение обычно имеет пульсации, и поэтому Uвх. мин должно быть выше примерно на 3,5 В, чем Uвых.

Для этого типа стабилизаторов напряжения могут быть использованы многие типы ОУ. Операционный усилитель в данном случае имеет однополюсный источник питания, причем нестабилизированное напряжение используется как + U, а земля как – U. Выходное напряжение ОУ должно быть достаточным для того, чтобы устанавливались требуемые значения стабилизированного выходного напряжения и падений напряжения между базой и эмиттером транзисторов Т1 и Т2.

Если ОУ имеет вывод «земля», то для того, чтобы установить на этом выводе напряжение, равное примерно Uвых/2, следует использовать делитель напряжения или стабилитрон, питаемые стабилизируемым выходным напряжением. Величина Uвых ограничена максимальным значением напряжения питания ОУ.

Если R1 на рис. 43 представляет собой потенциометр, то выходное напряжение может устанавливаться в диапазоне от (Uвх – 3,5 В) до напряжения чуть выше UСт1 Очевидно, выход источника питания не может быть установлен меньшим, чем UСт1 так как Uоп должно быть всегда чуть больше U*вых. Если предположить, что коэффициент усиления по напряжению пары Дарлингтона равен единице, то коэффициент усиления разомкнутой цепи, состоящей из ОУ, T1 и Т2, равен коэффициенту усиления А операционного усилителя. При отсутствии Uвх к усилителю прикладывается только UСт, цепь обратной связи для стабилизатора образуется делителем R1, R2. При этом выходное напряжение Uвых = AUСт. В развернутом виде

Uвых = UСт [A/(1 + Aβ)], но β = R2/(R1 + R2), а А>>(R1 + R2)/R2.

Поэтому Uвых ≈ UСт [(R1 + R2)/R2]. (21)

Таким образом, когда прикладывается Uвх, Uвых будет изменяться до тех пор, пока U*вых = Uоп, как будто бы схема стабилизации в целом представляет собой неинвертирующий операционный усилитель.

Уравнение, связывающее изменение выходного напряжения стабилизатора с изменением входного напряжения, имеет вид

ΔUвых / ΔUвх = (Rн /RК)[(R1 + R2)/AR2], (22)

где Rн – сопротивление нагрузки, RK – динамическое сопротивление коллектора, А – коэффициент усиления ОУ в разомкнутом состоянии по напряжению, R1 и R2 – резисторы, образующие делитель напряжения, с которого снимается U*вых.

Если в качестве последовательного регулирующего элемента используется пара Дарлингтона, то RК транзистора Т1 увеличивается до RК Т1 эфф = RК Т1 h21Э Т2, где h21Э Т2 – коэффициент усиления по току в схеме с общим эмиттером для управляющего транзистора в паре Дарлингтона.

Уравнение изменения выходного напряжения в зависимости от изменения выходного тока будет иметь вид

ΔUвых / ΔUвх = (Rн /А)[(R1 + R2)/R2]. (23)