- •Аналоговые и цифровые интегральные микросхемы

- •Введение

- •1. Технология изготовления интегральных микросхем

- •1.1. Общие сведения об интегральных микросхемах

- •1.2. Пленочные и гибридные интегральные микросхемы

- •1.3. Полупроводниковые интегральные микросхемы

- •2. Аналоговые Интегральные микросхемы

- •2.1. Основные сведения об операционных усилителях

- •Выводы операционного усилителя

- •2.3. Основные параметры операционных усилителей

- •2.4. Режим суммирующей точки

- •2.5. Повторитель напряжения

- •2.6. Неинвертирующий усилитель

- •2.7. Инвертирующий усилитель

- •2.8. Усилитель с дифференциальным входом

- •2.9. Усилитель с дифференциальным выходом (балансный)

- •2.10. Влияние отрицательной обратной связи на коэффициент усиления

- •2.11. Инвертирующий сумматор

- •2.12. Неинвертирующий сумматор

- •2.13 Интегратор

- •2.14. Дифференциатор

- •2.15. Схема логарифмического преобразователя

- •2.16. Схема умножения

- •2.17. Схема деления

- •2.18. Источники неизменного тока

- •2.19. Источники напряжения

- •2.20. Генератор колебаний прямоугольной формы

- •2.21. Генератор сигналов треугольной формы

- •2.22. Интегральные схемы стабилизаторов напряжения

- •2.22.1. Типы стабилизаторов напряжения

- •2.22.2. Линейные стабилизаторы напряжения последовательного действия (с переходным регулирующим элементом)

- •2.23. Специализированные интегральные схемы

- •2.23.1. Компараторы

- •2.23.2. Триггер Шмита

- •11.2. Токоразностный усилитель

- •2.25. Таймеры

- •2.26. Измерительные усилители

- •11.5. Изолирующие усилители

- •3.1.2. Параметры цифровых интегральных микросхем

- •3.2. Цифровые микросхемы транзисторно-транзисторной логики (ттл)

- •3.2.1. Основы схемотехники элементов ттл

- •3.3. Стандартные микросхемы серии ттл

- •3.4. Логические элементы

- •3.5. Триггеры

- •3.6. Мультивибраторы

- •3.7. Буферные элементы

- •3.8. Счетчики

- •3.9. Мультиплексоры

- •3.10. Регистры

- •3.11. Шифраторы и дешифраторы

- •3.12. Сумматоры

- •4. Микропроцессоры

- •4.1. Общие сведения о микропроцессорной технике

- •4.2. Классификация микропроцессоров

- •4.3. Основные характеристики микропроцессора

- •4.4. Структура типового микропроцессора

- •4.5. Логическая структура микропроцессора

- •Список используемой литературы

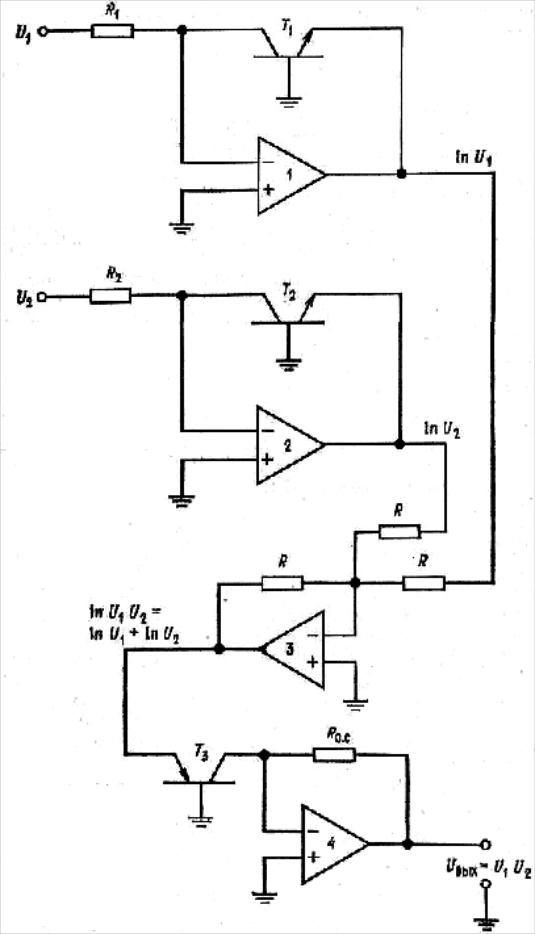

2.16. Схема умножения

Для построения схемы умножения можно, имея возможность получать значения логарифмов сомножителей, использовать следующее соотношение: ln(a×b) = lna + lnb. Схема умножения строится, как показано на рис. 35. Логарифмы величин U1 и U2 суммируются для получения величины, равной lnU1 + lnU2. Затем для нахождения величины U1U2 находится антилогарифм от полученной суммы. Схема может иметь больше двух входов, однако для каждого входа требуется свой логарифмический усилитель.

Выходное напряжение каждого логарифмического усилителя равно

Uвых1 = (kT/q) ln (U1/R1) – (kT/q) lnIо1,

Uвых2 = (kT/q) ln (U2/R2) – (kT/q) lnIо2.

Выходное напряжение сумматора равно

Uвых3 = (kT/q)[ ln (U1/R1) + ln (U2/R2) - lnI01 – lnIо2].

Выходное напряжение всей схемы равно

Uвых4 = Rо.с Iо3 antilog[ln (U1/R1) + ln (U2/R2) – lnIо1 – lnIо2] =

= Rо.с Iо3 antilog[ln (U1U2/R1R2 Iо1 Iо2)]=(Rо.с Iо3 / R1R2 Iо1 Iо2)U1U2.

Если Rо.с Iо3 = R1R2 Iо1 Iо2, то

Uвых4 = U1U2. (15)

Величины Iо должны быть соизмеримы, и они очень близки к значениям обратного тока IЭБО при малом обратном напряжении, приложенном к переходу эмиттер – база. Схема может быть собрана с использованием диодов вместо транзисторов как в логарифмическом, так и в антилогарифмическом усилителях. Предполагается, что все усилители, используемые в схеме, полностью скорректированы.

Выпускаются готовые схемы умножения, стабильно работающие в широком диапазоне изменения внешних условий и температур. Эти схемы являются сложными и тщательно выполненными

Рис. 35. Схема умножения аналоговых сигналов

устройствами. Их примерная блок-схема приведена на рис. 35. Некоторые умножители, называемые двухквадрантными, могут работать только при одной полярности сигналов на одном из входов; другие, называемые, четырехквадрантными, работают при любой полярности сигналов на обоих входах.

Умножители используются в схемах модуляторов, демодуляторов, фазовых детекторов, в аналоговых вычислительных устройствах, используемых при управлении технологическими процессами, при генерировании нелинейных колебаний и для линеаризации выходных сигналов преобразователей (датчиков) в системах сбора данных, причем это лишь некоторые из возможных применений умножителей.

2.17. Схема деления

Учитывая, что (ln a/b) = ln a – ln b, можно использовать тот же принцип, что и в устройстве умножения, для построения схемы деления. Единственным отличием от схемы умножения является использование дифференциального усилителя вместо инвертирующего сумматора. Схема блока деления приведена на рис. 36.

Рис. 36. Схема деления аналоговых сигналов

Сигналы на выходах логарифмических усилителей будут, равны

Uвых1 = (kT/q)[ ln (U1/R1) – lnIо1],

Uвых2 = (kT/q)[ ln (U2/R2) – lnIо2].

Для получения U1/U2 выходное напряжение логарифмического усилителя 1 подается на неинвертирующий вход, а выход логарифмического усилителя 2 – на инвертирующий вход дифференциального усилителя. Напряжение на выходе последнего будет равно

Uвых3 = (kT/q)[ ln (U1/R1) – lnIо1 – ln (U2/R2) + lnIо2].

Приняв, как обычно, Iо1 ≈ Iо2 и R1 = R2, получим

Uвых3= (kT/q)[ln(U1/R1) – ln(U2/R2)]= (kT/q) ln(U1R2/U2R1)= (kT/q)ln(U1/U2).

На выходе антилогарифмического преобразователя напряжение будет равно

Uвых4 = R Iо3 antilog[ ln (U1/U2)] = R Iо3U1/U2. (16)

Если величина Iо3 такова, что произведение Rо.с Iо3 может быть принято равным единице, то Uвых4 = U1/U2.

Область применения этих схем фактически та же, что и для устройств перемножения.