- •Поняття про інформацію

- •Основні переваги цифрової техніки

- •Основні поняття алгебри логіки

- •Базові положення алгебри логіки

- •Способи представлення логічних функцій:

- •Прості логічні функції і, або, не. Логічні елементи

- •Асинхронний rs-тригер

- •Асинхронний rs- тригер на ле і-не

- •Синхронізація

- •Перетворення тригерів

- •Основні поняття

- •Двійкова, вісімкова і шіснадцяткова системи числення

- •Прямий зворотний і доповнений код чисел

- •Спеціальні коди комп'ютерної схемотехніки

- •Визначення і класифікація лічильників

- •Двійкові лічильники

- •Асинхронні лічильники

- •Синхронні лічильники з наскрізним переносом

- •Недвійкові лічильники

- •Imc лічильників

- •Регістри

- •Класифікація регістрів

- •Нагромаджувальні регістри

- •Регістри зсуву

- •Дешифратор

- •Мультиплексори

- •Цифровий компаратор. Призначення. Будова

- •Класифікація запам'ятовуючих пристроїв

- •Будова комірок пам'яті озп

- •Архітектура імс озп

- •Організація матриці динамічної пам'яті

- •Постійні запам'ятовуючі пристрої (пзп)

- •Флеш-пам'ять

- •Програмовані логічні матриці

- •Програмування плм

- •Основні параметри ацп і цап

- •Принцип роботи і основні схеми цифро-аналогового перетворювача

- •Основні принципи аналого-цифрового перетворення

- •Паралельний ацп

- •Балансний ацп

- •Ацп послідовного наближення

- •Інтегруючий ацп

- •Нове покоління ацп

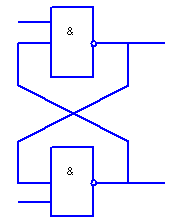

Асинхронний rs- тригер на ле і-не

Якщо в схемі защіпки замість інверторів використати ЛЕ І-НЕ - така схема також буде працювати як тригер. Щоб зрозуміти його роботу пригадаємо таблицю істинності елементу - І-НЕ.

-

Х1

Х2

Х3

0

0

1

0

1

1

1

0

1

1

1

0

Таблиця 4.4- Таблиця істинності І-НЕ.

З таблиці істинності І-НЕ видно що Y змінюється коли хоча б на одному з входів появляється 0. Тобто в цьому випадку нуль (низький рівень) вважається активним. Розглянемо роботу схеми зображеної на рис. 4.5, а.

Рисунок 4.5.а

Коли на верхній вхід тригера подати 0, а на нижній 1, верхній елемент DDI встановлюється в стан "1" незалежно від рівня на нижньому вході DDI. На нижньому елементі DD2 на входах дві одиниці - таким чином на виході DD2 Q = "0". З

вищесказаного можна зробити висновок, що верхній вхід S, нижній R, а активний рівень "0".

-

S(t)

R(t)

Q(t+1)

0

0

забор.

0

1

1

1

0

0

1

1

Q(t)

Таблиця 4.5-Мінімізована таблиця переходів.

Якщо на верхній і на нижній входи подати низький рівень напруги, то згідно з логікою роботи ЛЕ на обох виходах будуть одиниці, тобто це заборонений стан

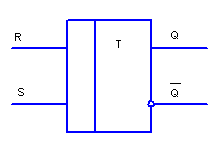

Позначення ІМС на рис. 4.5. б.

Рисунок 4.5.б

Надходження активного рівня сигналу на вхід RS- тригера встановлює тригер у відповідний стан, повторне надходження активного сигналу на той самий вхід не змінює стан тригера. Для зміни стану необхідно подати активний сигнал на другий вхід. Одночасне надходження активних рівнів сигналів на входи R і S тригера неприпустиме.

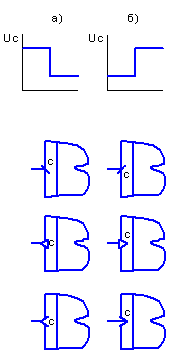

Синхронізація

Під час роботи складних цифрових схем дуже важливим є узгодження в часі різних подій, що відбуваються з різними вузлами схеми. Наприклад, дані з порта вводу повинні бути подані саме в той момент коли мікросхема пам'яті готова їх записати, або переключення кількох схем що виводять результат на шину повинно відбутись одночасно, щоб не викликати помилки. Для узгодження в часі (синхронізації) в цифрових схемах існує спеціальний пристрій - генератор тактових імпульсів, а кожна з мікросхем має спеціальний тактовий вхід "Clock" (або вхід синхронізації). Всі події в даній ІМС відбуваються, коли надходить синхроімпульс.

Тактовий вхід може бути прямим або інверсним. У першому випадку тригер реагує на перепад напруги на тактовому вході з нульового на одиничний, в другому - на перепад з одиничного значення на нульове.

Тобто тактові входи тригерів є прямі (по фронту синхроімпульсу) і інверсні (по спаду) На рисунку 4.6 показані різні способи позначення тактових входів а) переключення по фронту, б) переключення по спаду синхроімпульсу.

Рисунок 4.6

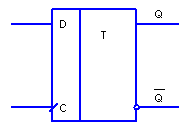

D - тригер

D- тригер має два входи: інформаційний вхід D і вхід синхронізації С.

Стан прямого виходу тригера повторює інформацію на вході D, зразу після надходження синхроімпульсу на вхід синхронізації С. Тобто вхід D визначає, яка саме інформація повинна заноситись в тригер, а вхід С визначає момент запису цієї інформації.

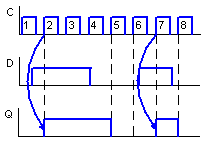

Роботу D-тригера краще пояснити за допомогою часових діаграм (рис. 4.7, а).

Рисунок 4.7.а

Коли на D надходить вхідний імпульс високого рівня, то тригер має встановитись в одиничний етан (високий рівень на виході Q), але стан тригера не змінюється до появи на вході С переднього фронту другого синхроімпульсу - тільки тоді тригер встановлюється в одиничний стан.

Стан тригера знову зміниться коли на D = "0", а на С передній фронт сьомого синхроімпульсу.

Назва D-тригер походить від англійського (dеlаy - затримка. Як відбувається затримка видно з рисунку 4.7.б.

Рисунок 4.7.б

Тривалість затримки визначається періодом синхроімпульсів.

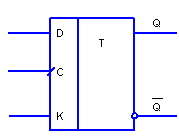

JK - тригер, Т-тригер

Універсальний Ж-тригер відрізняється від КЬ-тригера тим, що не має стану невизначеності. Коли } = 1, К =0 - з приходом синхроімпульсу тригер встановлюється в одиничний стан. Коли І =0 і К =1 - з приходом синхроімпульсу тригер встановлюється в нульовий стан. Коли 3 = 1, К = 1 - з приходом кожного синхроімпульсу стан тригера змінюється на протилежний. Таблиця переходів JK- тригера виглядає подібно до RS, проте у JK- тригера нема стану заборони.

-

J(t)

K(t)

Q(t+1)

0

0

Q(t)

0

1

1

1

0

0

1

1

Q(t)

Таблиця 4.6- Мінімізована таблиця JK – тригера.

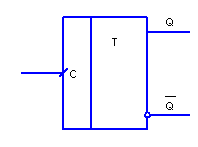

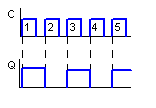

Т-тригер змінює свій стан з приходом кожного імпульсу, працює як подільник частоти вхідного сигналу' на два. Позначення і часові діаграми роботи Т-тригера показані на рис.4.8.

Рисунок 4.8

Рисунок 4.9.а

Рисунок 4.9.б