- •Поняття про інформацію

- •Основні переваги цифрової техніки

- •Основні поняття алгебри логіки

- •Базові положення алгебри логіки

- •Способи представлення логічних функцій:

- •Прості логічні функції і, або, не. Логічні елементи

- •Асинхронний rs-тригер

- •Асинхронний rs- тригер на ле і-не

- •Синхронізація

- •Перетворення тригерів

- •Основні поняття

- •Двійкова, вісімкова і шіснадцяткова системи числення

- •Прямий зворотний і доповнений код чисел

- •Спеціальні коди комп'ютерної схемотехніки

- •Визначення і класифікація лічильників

- •Двійкові лічильники

- •Асинхронні лічильники

- •Синхронні лічильники з наскрізним переносом

- •Недвійкові лічильники

- •Imc лічильників

- •Регістри

- •Класифікація регістрів

- •Нагромаджувальні регістри

- •Регістри зсуву

- •Дешифратор

- •Мультиплексори

- •Цифровий компаратор. Призначення. Будова

- •Класифікація запам'ятовуючих пристроїв

- •Будова комірок пам'яті озп

- •Архітектура імс озп

- •Організація матриці динамічної пам'яті

- •Постійні запам'ятовуючі пристрої (пзп)

- •Флеш-пам'ять

- •Програмовані логічні матриці

- •Програмування плм

- •Основні параметри ацп і цап

- •Принцип роботи і основні схеми цифро-аналогового перетворювача

- •Основні принципи аналого-цифрового перетворення

- •Паралельний ацп

- •Балансний ацп

- •Ацп послідовного наближення

- •Інтегруючий ацп

- •Нове покоління ацп

Флеш-пам'ять

Флеш-пам'ять (Flash-Memory) по типу елементів пам'яті і основним принципам роботи подібна пам'яті типу EPROM, проте ряд архітектурних і структурних особливостей дозволяють виділити її в окремий клас.

Розробка Флеш-пам'яті вважається кульмінацією розвитку схемотехніки пам'яті з електричним стиранням інформації.

Термін Flash пов'язаний з характерною особливістю цього виду пам'яті

можливістю одночасного стирання всього її об'єму. Ще до появи Флеш-пам'яті при зберіганні секретних даних використовувалися пристрої, які при спробах несанкціонованого доступу до них автоматично стирали записану в них інформацію і називалися пристроями типу Flash (спалах, мить). Ця наша перейшла і до пам'яті, що має властивість швидкого стирання всього масиву даних одним сигналом.

Характерними технічними засобами для покращення характеристик флеш-пам'яті порівняно з іншими є наявність внутрішніх мікропроцесорних засобів для організації керування роботою пам'яті, створення внутрішнього конвеєру операцій, організацію переривання процесів запису при звернені центрального процесора для читання (Erase Suspend). Без цього виникали б тривалі простої процесора, оскільки запис займає достатньо великий час.

Крім флеш-пам'ять містять в самій ІМС всі технічні засоби для програмування, а також пристосовані до роботи при різних напругах живлення (5В; 3,3 В та ін.).

Програмовані логічні матриці

Для комп'ютеризованих інтегрованих і робототехнічних систем характерним є схеми з тисячами і навіть мільйонами логічних елементів. Використання IMC малої степені інтеграції в таких випадках недоцільно, вони займають багато місця, споживають енергію живлення і зменшують надійність систем.

Тому для складних задач було вирішено використовувати ВІС і НВІС. При цьому загострилася проблема зниження універсальності для ІС із жорсткою структурою - довелося б робити багато різних типів ІС при зниженні обсягу виробництва кожного, що непомірно збільшило б їхню вартість, тому що високі витрати на проектування ВІС/НВІС відносилися б до невеликого об'єму їхнього випуску.

Вихід з виниклого протиріччя був знайдений на шляху переносу спеціалізації мікросхем в область програмування.

Є два підходи до розв'язку цієї задачі:

а) мікропроцесорні системи

б) матриці із програмованою структурою (ПЛМ).

Мікропроцесор виконує команди, що входять у його систему команд. Змінюючи послідовність команд (програму), можна вирішувати різні задачі на тому самому мікропроцесорі. Інакше кажучи, у цьому випадку структура апаратних засобів не зв'язана з характером розв'язуваної задачі. Це забезпечує мікропроцесорам масове виробництво з відповідним зниженням вартості.

У випадку ПЛМ користувачу у вигляді ВІС/НВІС із програмованою структурою пропонується схема, що містить безліч логічних блоків, комутацію між якими призначає сам системотехнік. Промисловість має можливість виробляти ВІС масовим тиражем, не адресуючись до окремих споживачів. Розробник програмує структуру ІС відповідно своєму проекту.

У НВІС із програмованою структурою обробка інформації відбувається без розбивки цього процесу на послідовно виконувані елементарні дії. Задача розв'язується "загалом", її характер визначає структуру пристрою.

Складність пристрою залежить від складності розв'язуваної задачі, чого немає в мікропроцесорних системах, де складність задачі впливає лише наї програму, а не на апаратні засоби її виконання.

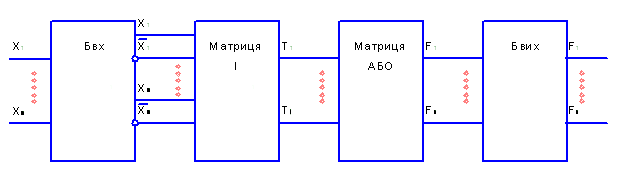

Рисунок 8.9

Загальна структура ПЛМ представлена на рисунку 8.9. Основою їх служить послідовність програмованих матриць елементів І і АБО. В структуру Входять також блоки вхідних і вихідних буферних каскадів (Бвх і Бвих).

Вхідні буфери, якщо не виконують складніші дії, перетворять однофазні вхідні сигнали в парафазні і формують сигнали необхідної потужності для живлення матриці елементів І.

Вихідні буфери забезпечують необхідну здатність навантаження виходів, дозволяють або забороняють вихід ПЛМ на зовнішні шини .

Основними параметрами ПЛМ є число входів т, число термів f і число виходів п.

Змінні XI... Хm подаються через Бвх на входи елементів І (кон'юнкторів), і в матриці І утворюються f термів. Під термом тут мають па увазі кон'юнкцію, що зв'язує вхідні змінні, представлені в прямій або інверсній формі. Число формованих термів рівно числу кон'юнкторів або, що теж саме, числу виходів матриці І.

Терми подаються далі на входи матриці АБО, тобто на входи диз'юнкторів, формуючих вихідні функції. Число диз'юнкторів рівно числу функцій m, що виробляються.

Таким чином. ПЛМ реалізує диз'юнктивну нормальну форму (ДНФ) відтворних функцій (дворівневу логіку). ПЛМ здатна реалізувати систему ш логічних функцій від пі аргументів, що містить не більше f термів. Відтворні функції є комбінаціями з будь-якого числа термів, формованих матрицею І. Які саме терми будуть вироблені і які комбінації цих термів складуть вихідні функції, визначається програмуванням ПЛМ.

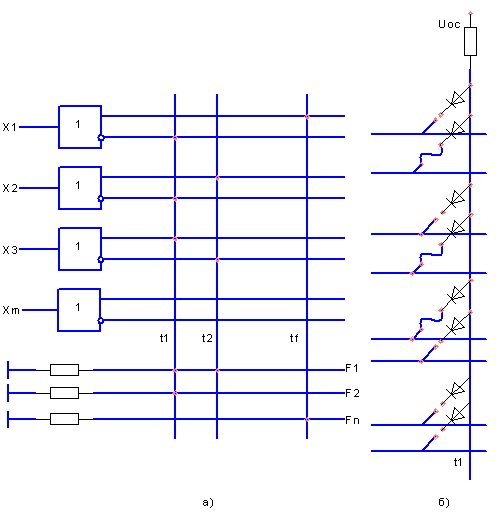

Рисунок 8.10

На рис. 8.10,а) в спрощеному вигляді (без буферних елементів) показані схемотехніка біполярної ПЛМ К556РТ1 з програмуванням перепалювання» перемичок. Показаний фрагмент для відтворення системи функцій

![]()

![]()

![]()

розмірністю 4, 7, 3. Параметрами (m, f, n) мікросхеми К556РТ1 є 16, 48,8.

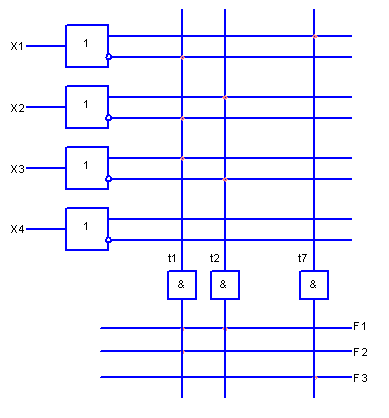

Елементами зв'язків в матриці ї служать діоди, що сполучують горизонтальні і вертикальні шини, як показано на рис. 8.10,6) де показані колі утворення терма t1. Спільно з резистором і джерелом живлення кола Ucc терм утворюють діодні схеми І, описані в темі 2. Для спрощення рисунку ПЛМ можна не показувати шини живлення і резистори, використати позначення елементів І (рис. 8.11).

Рисунок 8.11

До програмування всі перемички цілі, і діоди зв'язку розміщені у всіх вузлах координатної сітки. При будь-якій комбінації аргументів на виході бутс нуль, оскільки на вхід схеми подаються одночасно прямі і інверсні значення аргументів.

При програмуванні в схемі залишають тільки необхідні елементи зв'язку, ;і непотрібні знищують шляхом перепалювання перемичок. В даному випадку на вхід кон'юнктора подані XI, Х2 і ХЗ. Високий рівень вихідної напруги (логічна одиниця) з'явиться тільки за наявності високих напруг на всіх входах, до яких підключені діоди.

Елементами зв'язку в матриці АБО служать діоди які зібрані по схемі АБО (див. тему 2), або транзистори (рис.8.10,б), включені по схемі емітерного повторювача, які утворюють схему АБО відносно виходу (горизонтальної лінії). На рис. 8.10,б показано утворення функції F 1. При зображенні запрограмованих матриць наявність елементів зв'язків (цілі перемички) відмічається точкою у відповідному вузлі.