- •Поняття про інформацію

- •Основні переваги цифрової техніки

- •Основні поняття алгебри логіки

- •Базові положення алгебри логіки

- •Способи представлення логічних функцій:

- •Прості логічні функції і, або, не. Логічні елементи

- •Асинхронний rs-тригер

- •Асинхронний rs- тригер на ле і-не

- •Синхронізація

- •Перетворення тригерів

- •Основні поняття

- •Двійкова, вісімкова і шіснадцяткова системи числення

- •Прямий зворотний і доповнений код чисел

- •Спеціальні коди комп'ютерної схемотехніки

- •Визначення і класифікація лічильників

- •Двійкові лічильники

- •Асинхронні лічильники

- •Синхронні лічильники з наскрізним переносом

- •Недвійкові лічильники

- •Imc лічильників

- •Регістри

- •Класифікація регістрів

- •Нагромаджувальні регістри

- •Регістри зсуву

- •Дешифратор

- •Мультиплексори

- •Цифровий компаратор. Призначення. Будова

- •Класифікація запам'ятовуючих пристроїв

- •Будова комірок пам'яті озп

- •Архітектура імс озп

- •Організація матриці динамічної пам'яті

- •Постійні запам'ятовуючі пристрої (пзп)

- •Флеш-пам'ять

- •Програмовані логічні матриці

- •Програмування плм

- •Основні параметри ацп і цап

- •Принцип роботи і основні схеми цифро-аналогового перетворювача

- •Основні принципи аналого-цифрового перетворення

- •Паралельний ацп

- •Балансний ацп

- •Ацп послідовного наближення

- •Інтегруючий ацп

- •Нове покоління ацп

Цифровий компаратор. Призначення. Будова

Компаратори (схеми порівняння) призначені для порівняння двох двійкових чисел за модулем, знаком і порядком. Операції, які виконують ці схеми, включають: рівність і нерівність двох чисел і знак нерівності. Для кожної з цих операцій у схемі порівняння передбачено вихід, на якому з'являється напруга, що дорівнює за значенням логічній "1", якщо виконується умова операції. Розглянемо принцип будови схеми, яка порівнює два однорозрядні числа а і b. Перша операція, яку реалізує така схема, має встановлювати рівність цих чисел: а = b. Друга визначає випадок а > b, а третя випадок коли а < b.

Складання схеми компаратора починають з складання таблиці істинності що будується згідно алгоритму заданому у визначені.

З таблиці 7.5 видно, що схема яку визначає третя колонка результатів може були побудована на схемі виключне АБО-НЕ ("Нерівнозначність"), а перша і друга визначають схеми що будуються на базі законів логічного синтезу.

Таблиця 7.5

a |

b |

a>b |

a<b |

а =b |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

Запишемо булеві рівняння згідно законів алгебри логіки. Нехай У1 відповідає випадку коли “а=b”Y2 - коли “а<b”YЗ – коли “а>b”.

![]()

![]()

![]()

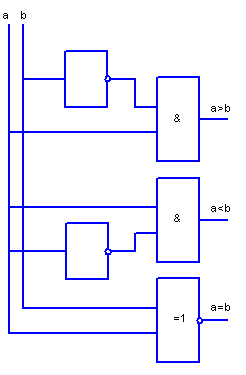

За рівняннями складаємо електронну схему (рис.7.9,а).

Рисунок 7.9.а

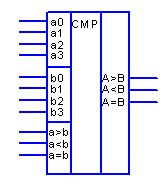

На рисунку 7.9.б показано позначення мікросхеми чотирьохрозрядного компаратора К561ИМ1.

Рисунок 7.9.б

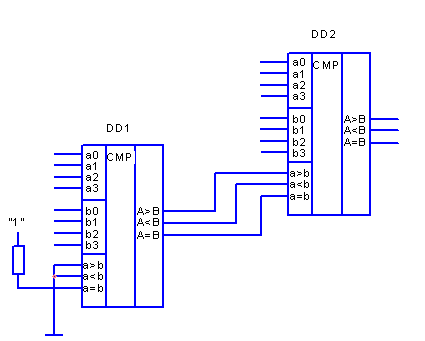

Порівнянням багаторозрядних чисел виконується за таким алгоритмом: спочатку порівнюються найстарші розряди в нашому випадку а3 і bЗ. Якщо один з них більше то на цьому порівняння закінчується наприклад аЗ=1, а bЗ=0 тоді на виході а>b виникає високий рівень напруги незалежно від інших входів. Якщо старші розряди рівні між собою порівнюються молодші і т.д. Якщо рівні значення в усіх розрядах - на виходах повторюються сигнали на входах розширення. При необхідності порівняння багаторозрядних (більше чотирьох розрядів) чисел входи розширення а>b, а<b і а =b використовують для підключення мікросхем молодших розрядів. Якщо в мікросхемі старших розрядів всі розряди рівні між собою виходи встановляться в залежності від того яке співвідношення молодших розрядів DD2

У мікросхемі що порівнює наймолодші розряди необхідно правильно під'єднати входи розширення, так щоб при рівності всіх розрядів на виході виникала комбінація:

"а>b"=0 , "а<b"=0 і "а=b" = 1. цього досягають виконавши під'єднання, як на рис. 7.10.

Рисунок 7.10

ПРИСТРОЇ ПАМ'ЯТІ І ПРОГРАМОВАНІ ЛОГІЧНІ МАТРИЦІ(ПМЛ)

У багатьох сучасних цифрових пристроях і комп'ютерних системах використовуються різноманітні запам'ятовуючі пристрої (ЗП), їх називають електронною пам'яттю.