- •Поняття про інформацію

- •Основні переваги цифрової техніки

- •Основні поняття алгебри логіки

- •Базові положення алгебри логіки

- •Способи представлення логічних функцій:

- •Прості логічні функції і, або, не. Логічні елементи

- •Асинхронний rs-тригер

- •Асинхронний rs- тригер на ле і-не

- •Синхронізація

- •Перетворення тригерів

- •Основні поняття

- •Двійкова, вісімкова і шіснадцяткова системи числення

- •Прямий зворотний і доповнений код чисел

- •Спеціальні коди комп'ютерної схемотехніки

- •Визначення і класифікація лічильників

- •Двійкові лічильники

- •Асинхронні лічильники

- •Синхронні лічильники з наскрізним переносом

- •Недвійкові лічильники

- •Imc лічильників

- •Регістри

- •Класифікація регістрів

- •Нагромаджувальні регістри

- •Регістри зсуву

- •Дешифратор

- •Мультиплексори

- •Цифровий компаратор. Призначення. Будова

- •Класифікація запам'ятовуючих пристроїв

- •Будова комірок пам'яті озп

- •Архітектура імс озп

- •Організація матриці динамічної пам'яті

- •Постійні запам'ятовуючі пристрої (пзп)

- •Флеш-пам'ять

- •Програмовані логічні матриці

- •Програмування плм

- •Основні параметри ацп і цап

- •Принцип роботи і основні схеми цифро-аналогового перетворювача

- •Основні принципи аналого-цифрового перетворення

- •Паралельний ацп

- •Балансний ацп

- •Ацп послідовного наближення

- •Інтегруючий ацп

- •Нове покоління ацп

Регістри

Регістром називають послідовнісний пристрій, призначений для записування, тимчасового зберігання і перетворення двійкової інформації.

Будь-який регістр складається із з'єднаних в певній послідовності тригерів і в багатьох випадках логічних елементів для керування ними Кожний тригер призначений для введення, зберігання і виведення одного розряду двійкового числа. Загальне число тригерів у регістрі визначає його розрядність. Якщо, наприклад, регістр складається з чотирьох тригерів, то він призначений для зберігання чотири розрядних двійкових чисел.

Залежно від призначення всі регістри поділяють на три групи: нагромаджувальні. зсувні, перетворювальні.

Регістр призначений для виконання наступних операцій:

прийом n- розрядного коду числа з іншого цифрового пристрою або вузла ЕОМ;

передача коду числа в інший вузол;

зберігання коду числа;

перетворення прямого коду числа в зворотний або додатковий і навпаки;

зсув ліворуч або праворуч коду числа на необхідне число розрядів;

перетворення послідовного коду в паралельний і навпаки:

порозрядне логічне складання двох чисел;

Класифікація регістрів

По можливості зміщення інформації розрізнюють:

регістри зсуву,

нагромаджувальні регістри (регістри без зсуву).

По кількості тактів управління, необхідних для запису інформації:

однотактні регістри (з прийомом інформації в парафазному коді),

двотактні (зі скиданням перед записом інформації),

багатотактні регістри зсуву.

Регістри зсуву класифікуються за способом прийому і передачі інформації:

послідовні (прийом і передача коду слова відбувається послідовно, розряд за розрядом);

паралельні (з одночасним прийомом або передачею кодів всіх розрядів):

послідовно-паралельні (прийом і передача слова проводиться групами по декілька розрядів, наприклад, байтами).

Нагромаджувальні регістри

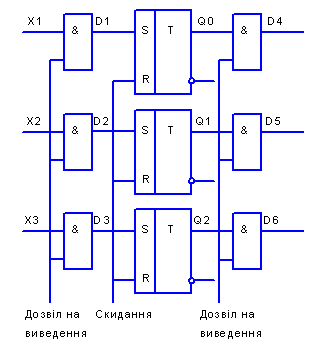

Нагромаджувальні регістри призначені для введення, зберігання і виведення багаторозрядних двійкових чисел. Числа в такий регістр надходять паралельним кодом, що означає подання електричних напруг., які за значенням відповідають логічній «1» або логічному «0», на всі входи регістра одночасно. На рис.6.10 подано один з можливих варіантів побудови трирозрядного паралельного регістра, що складається з К5-тригерів і логічних елементів І.

Рисунок 6.10

Двійкова інформація, потрібна для запису в регістр, надходить на інформаційні входа XI, Х2, ХЗ. Перед записуванням цієї інформації треба встановити початковий нульовий стан усіх тригерів. Для цього на керуючий вхід «Скидання», з'єднаний з R-входами тригерів, подають імпульс, логічну «1». Виходячи з принципу роботи RS-тригера, така дія призведе до встановлення нульового стану на прямих виходах Q1. Q2, Q3. Під час подання електричного імпульсу на керуючий вхід «Дозвіл на введення» двійкове число через логічні елементи D1, D2, DЗ пропускається на входи S тригерів.

При цьому ті тригери, на входи Б яких надходить одиничний розряд двійкового числа, встановлюються в одиничний стан, а ті тригери, на входи S яких надходить нульовий розряд, будуть у нульовому стані. Таким чином, двійкова інформація з входів XI, Х2, ХЗ записується на прямі виходи тригерів Q1, Q2, Q3 і зберігається там до чергових дій на керуючі входи.

Двійкова інформація на виходи регістра видається через логічні елементи D4, D5, D6 після приходу імпульсу на керуючий вхід «дозвіл на виведення».