- •Поняття про інформацію

- •Основні переваги цифрової техніки

- •Основні поняття алгебри логіки

- •Базові положення алгебри логіки

- •Способи представлення логічних функцій:

- •Прості логічні функції і, або, не. Логічні елементи

- •Асинхронний rs-тригер

- •Асинхронний rs- тригер на ле і-не

- •Синхронізація

- •Перетворення тригерів

- •Основні поняття

- •Двійкова, вісімкова і шіснадцяткова системи числення

- •Прямий зворотний і доповнений код чисел

- •Спеціальні коди комп'ютерної схемотехніки

- •Визначення і класифікація лічильників

- •Двійкові лічильники

- •Асинхронні лічильники

- •Синхронні лічильники з наскрізним переносом

- •Недвійкові лічильники

- •Imc лічильників

- •Регістри

- •Класифікація регістрів

- •Нагромаджувальні регістри

- •Регістри зсуву

- •Дешифратор

- •Мультиплексори

- •Цифровий компаратор. Призначення. Будова

- •Класифікація запам'ятовуючих пристроїв

- •Будова комірок пам'яті озп

- •Архітектура імс озп

- •Організація матриці динамічної пам'яті

- •Постійні запам'ятовуючі пристрої (пзп)

- •Флеш-пам'ять

- •Програмовані логічні матриці

- •Програмування плм

- •Основні параметри ацп і цап

- •Принцип роботи і основні схеми цифро-аналогового перетворювача

- •Основні принципи аналого-цифрового перетворення

- •Паралельний ацп

- •Балансний ацп

- •Ацп послідовного наближення

- •Інтегруючий ацп

- •Нове покоління ацп

Двійкові лічильники

Схеми лічильників побудовані на базі тригерів. Число тригерів, необхідних для побудови лічильника, визначається по формулі: n=log2 Кпер, де Кпер коефіцієнт переліку (модуль).

Іншою важливою характеристикою є швидкодія. Швидкодія лічильника в значній мірі визначається будовою кіл переносу. Швидкодія характеризується часом встановлення коду і розрізнювальною здатністю.

Час встановлення коду на виході лічильника tвст тобто інтервал часу між моментом надходження вхідного імпульсу і моментом закінчення самого тривалого перехідного процесу в лічильнику.

В двійковому лічильнику з послідовним переносом tвст лічильника визначається часом спрацювання тригерів лічильника tтр і кількістю розрядів лічильника n.

Розрізнювальна здатність лічильника визначається мінімальним часом ti між двома вхідними імпульсами, при якому лічильник працює надійно.

Асинхронні лічильники

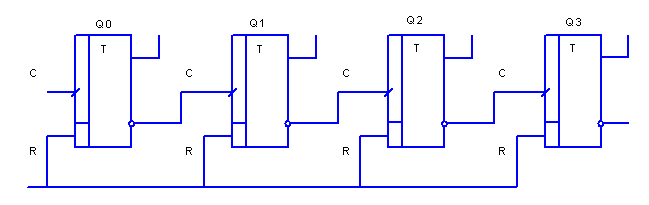

Найпростіші схеми двійкових лічильників виконуються шляхом послідовного з'єднання тригерів з лічильними входами. Т-тригер є лічильником з К=2. Для побудови лічильника з К=2n потрібно n таких тригерів. Розглянемо як приклад схему асинхронного двійкового лічильника з послідовним переносом:

Схема представлена на рис.6.2 відображає внутрішню структуру лічильника позначення якого наведено на рис. 6.1.

Рисунок 6.2

Якщо на лічильний вхід кожного наступного тригера лічильника подавати сигнал не з інверсного виходу, а з прямого виходу попереднього тригера, то лічильник буде виконувати операцію віднімання рис. 6.3.

![]()

Рисунок 6.3

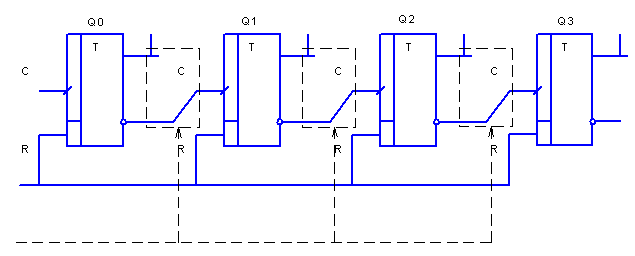

Лічильники, здатні виконувати функції додавання і віднімання, називаються реверсивними. Для цього в наведеній на рис. 6.3 схемі між виходами кожного попереднього каскаду і входами наступного необхідно вмонтувати електронний перемикач який переключається під впливом зовнішнього сигналу " +/-".

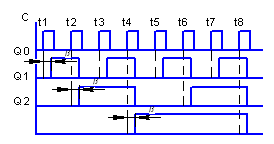

Основним недоліком лічильників з послідовним переносом є низька швидкодія. Часові діаграми роботи лічильника будуть мати наступний вигляд (рис. 6.4), дещо відмінний від ідеальних, наведених на рис.6.1

Тривалість затримки наростає від тригера до тригера, а на певному каскаді, де затримка буде спів розмірна з тривалістю імпульсу можлива втрата інформації.

Рисунок 6.4

Синхронні лічильники з наскрізним переносом

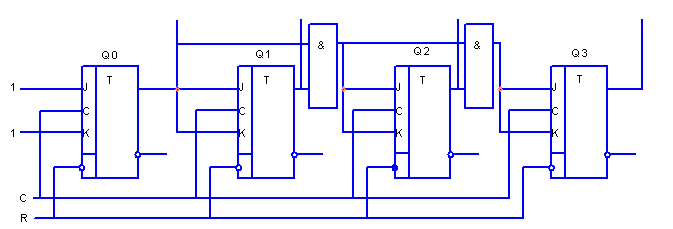

Швидкодію лічильних схем можна підвищити завдяки спеціальній організації кіл переносу і подачі лічильних імпульсів на всі розряди лічильника одночасно (Рис.6.5). Як правило, в таких схемах лічильні імпульси виконують роль імпульсів синхронізації, тому лічильники, що розглядаються нижче відносяться до класу синхронних.

Рисунок

6.5

Рисунок

6.5

У схемі з наскрізним переносом перемикання кожного наступного розряду лічильника на JK-тригерах можливе в тому випадку, якщо на його інформаційних входах J і К присутня "І". В іншому випадку тригер знаходиться в режимі запам'ятовування.

В наведеній нижче таблиці розглянуті зміни станів на входах тригерів на момент надходження синхроімпульсів, імпульси надходять одночасно на всі тригери схеми.

В початковий момент часу всі виходи

Q0=0 Q1=0 Ql=0 Q2=0 q2=0 Q3=0

лічильника в нульовому стані, до переключення готовий тільки перший JK- тригер

Після надходження першого імпульсу

Q0=1 Q1=0 ql=0 Q2=0 q2=0 Q3-0

на вхід С, перший тригер переключається в одиничний стан, після чого до переключения готові вже два тригера оскільки на входах J і К другого каскаду також " 1 "

Після другого імпульсу перший тригер

Q0=0 Ql=l ql=0 Q2=0 q2=0 Q3=0

знов переходить y нульовий стан і другий тригер тепер не готовий до переключення, знову готовий до переключення тільки пертий каскади

Після надходження третього імпульсу

Q0=1 Ql = l ql=l Q2=0 q2=0 Q3=0

ситуація змінюється, па входах елемента І дві одиниці, тому на йото виході Ql - логічна одиниця і до переключення готові всі три перші каскади

Після надходження четвертого імпульсу

Q0=0 Q1=0 ql=0 Q2=l q2=0 Q3=0

переключаються зразу три готових до переключення тригера

Для побудови даного лічильника використовувалися багато входові JK-тригери. З схеми видно, що із зростанням порядкового номера тригера збільшується число входів J і К до необхідних для організації схеми. Оскільки число входів тригера і його навантажувальна здатність обмежені, то розрядність лічильника з паралельним переносом звичайно не перевищує чотирьох. При побудові лічильників більшої розрядності розряди лічильника розбивають на групи по чотири тригера, і всередині коленої групи будують кола паралельного переносу.