- •Оглавление

- •Введение

- •Методы разработки алгоритмов и программ имитационных моделей комбинационных схем и последовательных автоматов с памятью

- •Методы разработки алгоритмов имитационных моделей комбинационных схем

- •Непосредственнее решение функций алгебры логики

- •Метод бинарных функций

- •Решение функции алгебры логики методом адресных переходов

- •Элементы памяти полупроводниковых устройств

- •Классификация триггерных устройств

- •Триггер как элементарный последовательный автомат

- •Наиболее популярные методы разработки алгоритмов и программ имитационных моделей с памятью

- •Асинхронные триггеры

- •Асинхронный rs-триггер

- •Асинхронные s-, r- и e-триггеры

- •Асинхронный d-триггер

- •Асинхронные т-триггеры

- •Асинхронные jk-триггеры с импульсным управлением

- •Асинхронные потенциально управляемые jk-триггеры

- •Синхронные (тактируемые) триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Синхронный jk-триггер

- •Универсальные d- и jk-триггеры

- •Примеры схем, построенных с применением jk-триггера к155тв1

- •Пример разработки имитационной модели триггерного устройства

- •Непосредственное решение уравнений, описывающих работу триггерной установки

- •Использование графа состояний триггерного устройства для разработки алгоритма

- •Применение таблицы переходов для решения поставленной задачи

- •Реализация дискретных устройств на микроконтроллерах pic16

- •Введение в программирование микроконтроллеров pic16

- •Краткие сведения об архитектуре микроконтроллеров pic16 и принципе их работы

- •Язык ассемблера pic16

- •Команды пересылки

- •Арифметические команды

- •Булевы операции

- •Битовые операции

- •Операции условного, безусловного переходов и вызова подпрограмм

- •Общий вид программы и типовые приемы программирования

- •Битовая арифметика

- •Ветвление

- •Вызов подпрограммы

- •Использование среды mplab

- •Моделирование комбинационных автоматов

- •Метод непосредственного вычисления фал

- •Метод бинарных функций

- •Метод адресных переходов (табулирование функций)

- •Приложение а. Исходные тексты примеров а.1. Применение метода непосредственного вычисление фал

- •А.2. Применение метода бинарных программ

- •А.3. Применение метода адресных переходов а.3.1. Способ размещения таблицы в пзу

- •А.3.2. Способ размещения таблицы в озу

- •А.4. Модуль hdw_init

- •Приложение б. Краткий справочник инструкций pic16

- •Библиография

- •Имитационное моделирование дискретных устройств

- •620034, Екатеринбург, ул. Колмогорова, 66.

Асинхронные jk-триггеры с импульсным управлением

Асинхронный триггер JK является двухвходовым, отличается от RS-триггера только тем, что при J=K=1 переключается в противоположное состояние, а при J=K=0 он сохраняет предыдущее состояние.

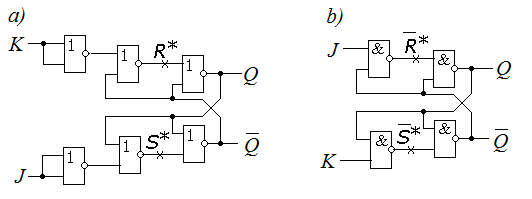

Схемы JK-триггеров с импульсным управлением, построенных в базисах ИЛИ-НЕ и И-НЕ, приведены на рис. 1,35, граф состояний триггера представлен на рис. 1.36.

Рис. 1.35. Асинхронные JK-триггеры с импульсным управлением

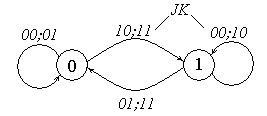

Рис. 1.36. Граф состояний асинхронного JK-триггера

с импульсным управлением

Асинхронные JK-триггеры с импульсным управлением управляются короткими импульсами. Продолжительность импульса должна находиться в следующих пределах:

2tзд.ср. ≤ tи ≤ 3tзд.ср.,

где tзд.ср. –время срабатывания логического элемента.

Если продолжительность импульса будет меньше продолжительности срабатывания элемента, умноженного на два, триггер может работать неустойчиво. При длительном появлении единиц на входах триггера он перейдёт в режим генерации импульсов.

Примечание. Счётные триггеры, используемые в диспетчерских централизациях ЧДЦ, «Нева», «Луч» и др., на JK-входах имеют конденсаторы и могут быть описаны подобным образом.

Асинхронные потенциально управляемые jk-триггеры

Потенциально управляемые асинхронные JK-триггеры допускают длительную подачу сигнала на их входах. Эти триггеры являются двухтактными (MS-триггерами). При этом вспомогательный триггер изменяет своё состояние в момент появления единиц на его входах, а основной триггер переключается после появления на входах нулей. Подача единиц на входы J и K приведет к переключению JK-триггера в противоположное состояние. Таким образом, соединив входы J и K, можно получить Т-триггер.

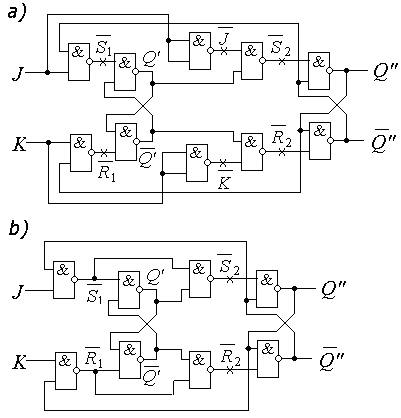

Варианты схем асинхронного потенциально управляемого JK-триггера, построенного в базисе И-НЕ, изображены на рис. 1.37.

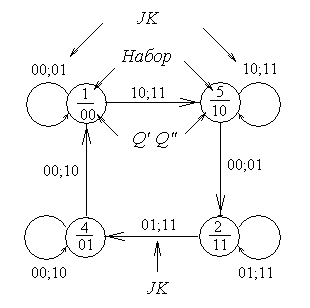

На рис. 1.38 представлен граф состояний потенциального JK-триггера, изображённого на рис. 1.37 а. На рис. 1.39 приведены карты Карно этого же триггера.

Рис. 1.37. Варианты схем асинхронного JK-триггера

в базисе И-НЕ

Рис. 1.38. Граф потенциального асинхронного JK-триггера

Набор – номер строки таблицы переходов.

Ниже приведена таблица состояний рассматриваемых триггеров.

Таблица 1.8

Таблица состояний асинхронного потенциально

управляемого JK-триггера

Набор |

Входные перемен. |

Текущее состояние |

Новое состояние |

Контрольные точки |

||||||

Jn |

Kn |

Q’n |

Q”n |

Q’n+1 |

Q”n+1 |

R1 |

S1 |

R2 |

S2 |

|

0 |

0 |

0 |

0 |

0 |

(0) |

(0) |

0 |

Ø |

1 |

Ø |

1 |

0 |

0 |

0 |

1 |

(0) |

0 |

0 |

Ø |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

(1) |

1 |

Ø |

1 |

0 |

1 |

3 |

0 |

0 |

1 |

1 |

(1) |

(1) |

Ø |

1 |

Ø |

1 |

4 |

0 |

1 |

0 |

0 |

(0) |

(0) |

1 |

Ø |

1 |

Ø |

5 |

0 |

1 |

0 |

1 |

(0) |

(1) |

1 |

Ø |

Ø |

1 |

6 |

0 |

1 |

1 |

0 |

(1) |

1 |

Ø |

1 |

0 |

1 |

7 |

0 |

1 |

1 |

1 |

0 |

(1) |

1 |

0 |

Ø |

1 |

8 |

1 |

0 |

0 |

0 |

1 |

(0) |

0 |

1 |

1 |

Ø |

9 |

1 |

0 |

0 |

1 |

(0) |

0 |

1 |

Ø |

1 |

0 |

10 |

1 |

0 |

1 |

0 |

(1) |

(0) |

Ø |

1 |

1 |

Ø |

11 |

1 |

0 |

1 |

1 |

(1) |

(1) |

Ø |

1 |

Ø |

1 |

12 |

1 |

1 |

0 |

0 |

1 |

(0) |

0 |

1 |

1 |

Ø |

13 |

1 |

1 |

0 |

1 |

(0) |

(1) |

1 |

Ø |

Ø |

1 |

14 |

1 |

1 |

1 |

0 |

(1) |

(0) |

Ø |

1 |

1 |

Ø |

15 |

1 |

1 |

1 |

1 |

0 |

(1) |

1 |

0 |

Ø |

1 |

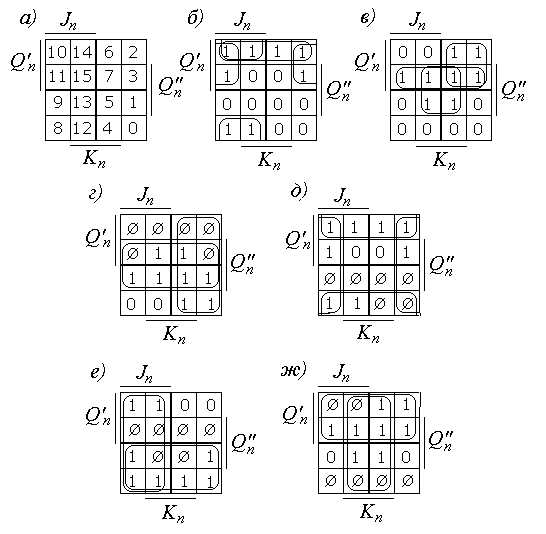

Рис. 1.39. Карты Карно потенциально управляемого JK-триггера

а) – эталонная, б) – для Q’n+1, в) – для Q”n+1, г)– для R1, д) – для S1,

е) – для R2, ж) – для S2