- •Оглавление

- •Введение

- •Методы разработки алгоритмов и программ имитационных моделей комбинационных схем и последовательных автоматов с памятью

- •Методы разработки алгоритмов имитационных моделей комбинационных схем

- •Непосредственнее решение функций алгебры логики

- •Метод бинарных функций

- •Решение функции алгебры логики методом адресных переходов

- •Элементы памяти полупроводниковых устройств

- •Классификация триггерных устройств

- •Триггер как элементарный последовательный автомат

- •Наиболее популярные методы разработки алгоритмов и программ имитационных моделей с памятью

- •Асинхронные триггеры

- •Асинхронный rs-триггер

- •Асинхронные s-, r- и e-триггеры

- •Асинхронный d-триггер

- •Асинхронные т-триггеры

- •Асинхронные jk-триггеры с импульсным управлением

- •Асинхронные потенциально управляемые jk-триггеры

- •Синхронные (тактируемые) триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Синхронный jk-триггер

- •Универсальные d- и jk-триггеры

- •Примеры схем, построенных с применением jk-триггера к155тв1

- •Пример разработки имитационной модели триггерного устройства

- •Непосредственное решение уравнений, описывающих работу триггерной установки

- •Использование графа состояний триггерного устройства для разработки алгоритма

- •Применение таблицы переходов для решения поставленной задачи

- •Реализация дискретных устройств на микроконтроллерах pic16

- •Введение в программирование микроконтроллеров pic16

- •Краткие сведения об архитектуре микроконтроллеров pic16 и принципе их работы

- •Язык ассемблера pic16

- •Команды пересылки

- •Арифметические команды

- •Булевы операции

- •Битовые операции

- •Операции условного, безусловного переходов и вызова подпрограмм

- •Общий вид программы и типовые приемы программирования

- •Битовая арифметика

- •Ветвление

- •Вызов подпрограммы

- •Использование среды mplab

- •Моделирование комбинационных автоматов

- •Метод непосредственного вычисления фал

- •Метод бинарных функций

- •Метод адресных переходов (табулирование функций)

- •Приложение а. Исходные тексты примеров а.1. Применение метода непосредственного вычисление фал

- •А.2. Применение метода бинарных программ

- •А.3. Применение метода адресных переходов а.3.1. Способ размещения таблицы в пзу

- •А.3.2. Способ размещения таблицы в озу

- •А.4. Модуль hdw_init

- •Приложение б. Краткий справочник инструкций pic16

- •Библиография

- •Имитационное моделирование дискретных устройств

- •620034, Екатеринбург, ул. Колмогорова, 66.

Асинхронный d-триггер

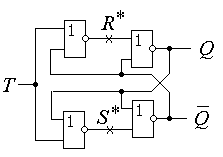

Схема D-триггера и его граф приведены на рис. 1.29 и 1.30. Этот триггер опрокидывается при подаче на вход единицы и возвращается в исходное состояние при появлении на входе нуля.

Рис. 1.29. Асинхронный D-триггер

Рис.1.30. Граф D-триггер

Подобные триггеры используются для формирования прямоугольных импульсов в случаях, когда на входы подаются аналоговые сигналы.

Асинхронные т-триггеры

Схема асинхронного Т-триггера с импульсным управлением представлена на рис. 1.31. Этот триггер имеет только один вход управления. Состояние Т-триггера изменяется на противоположное в момент поступления единицы на его вход. Продолжительность импульса управления должна находиться в следующих пределах: 2tзд.ср. ≤ tи ≤ 3tзд.ср. Если продолжительность импульса меньше указанной, возможна неустойчивая работа триггера. При превышении указанной продолжительности импульса триггер переходит в режим генерации (tзд.ср. – время рабатывания логического элемента).

Рис. 1.31. Т- триггер с импульсным управлением

в базисе ИЛИ-НЕ

Переключение Т – триггера осуществляется подачей короткой единицы на его вход. Устойчивое состояние триггера сохраняется сколь угодно долго при подаче на его вход нуля.

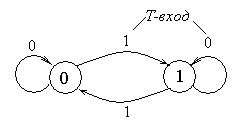

Граф состояний Т – триггера с импульсным управлением показан на рис. 1.32. Переход триггера из одного состояния в другое осуществляется подачей короткой единицы, устойчивое состояние сохраняется при наличии на входе нуля.

Рис. 1.32. Граф состояний Т-триггера с импульсным управлением

Примечание. Примером подобных триггеров могут служить триггеры, на входах которых включены дифференцирующие цепочки. Эти триггеры нашли широкое применение в системах диспетчерской централизации ЧДЦ, «Нева», «Луч» и др.

Потенциальные Т – триггеры изменяют свое состояние в два такта: сначала подается на Т – вход единица, затем ноль. При этом длительность этих импульсов может быть любой.

Варианты потенциальных Т-триггеров приведены на рис. 1.33.

На рис 1.33 d изображён RS-триггер в базисе И-НЕ с прямым и инверсным обозначением входов.

Рис. 1.33. Варианты потенциальных Т-триггеров в базисе И-НЕ

При подаче на Т-вход единицы изменяет свое состояние на противоположное первый триггер, появление нуля на Т – входе приводит к переключению второго триггера (номера состояний графа, приведенного на рис. 1.34 соответствуют номерам строк таблицы состояний 1.7).

Рис. 1.34. Граф асинхронного Т-триггера с

потенциальным управлением

Таблица состояний Т– триггера, изображенного на рис. !.33а

Таблица 1.7

Таблица состояний асинхронного Т-триггера с

потенциальным управлением

Набор |

Входная переменная |

Текущее состояние |

Новое состояние |

Контрольные точки |

||||||

Tn |

Q’n |

Q”n |

Q’n+1 |

Q”n+1 |

R1 |

S1 |

R2 |

S2 |

||

0 |

0 |

0 |

0 |

(0) |

|

1 |

Ø |

0 |

1 |

|

1 |

0 |

0 |

1 |

(0) |

(1) |

1 |

Ø |

Ø |

1 |

|

2 |

0 |

1 |

0 |

(1) |

(0) |

Ø |

1 |

1 |

Ø |

|

3 |

0 |

1 |

1 |

(1) |

0 |

Ø |

1 |

1 |

0 |

|

4 |

1 |

0 |

0 |

|

(0) |

1 |

Ø |

1 |

Ø |

|

5 |

1 |

0 |

1 |

1 |

(1) |

0 |

1 |

Ø |

1 |

|

6 |

1 |

1 |

0 |

0 |

(0) |

1 |

0 |

1 |

Ø |

|

7 |

1 |

1 |

1 |

(1) |

|

Ø |

1 |

Ø |

1 |

|

Графы и таблицы состояний для всех остальных триггеров рис. 1,33 выглядят аналогично.

Методика разработки алгоритмов управления данными триггерами практически не отличается от рассмотренных выше методов.

1

1 (0)

(0) (1)

(1)