- •Оглавление

- •Введение

- •Методы разработки алгоритмов и программ имитационных моделей комбинационных схем и последовательных автоматов с памятью

- •Методы разработки алгоритмов имитационных моделей комбинационных схем

- •Непосредственнее решение функций алгебры логики

- •Метод бинарных функций

- •Решение функции алгебры логики методом адресных переходов

- •Элементы памяти полупроводниковых устройств

- •Классификация триггерных устройств

- •Триггер как элементарный последовательный автомат

- •Наиболее популярные методы разработки алгоритмов и программ имитационных моделей с памятью

- •Асинхронные триггеры

- •Асинхронный rs-триггер

- •Асинхронные s-, r- и e-триггеры

- •Асинхронный d-триггер

- •Асинхронные т-триггеры

- •Асинхронные jk-триггеры с импульсным управлением

- •Асинхронные потенциально управляемые jk-триггеры

- •Синхронные (тактируемые) триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Синхронный jk-триггер

- •Универсальные d- и jk-триггеры

- •Примеры схем, построенных с применением jk-триггера к155тв1

- •Пример разработки имитационной модели триггерного устройства

- •Непосредственное решение уравнений, описывающих работу триггерной установки

- •Использование графа состояний триггерного устройства для разработки алгоритма

- •Применение таблицы переходов для решения поставленной задачи

- •Реализация дискретных устройств на микроконтроллерах pic16

- •Введение в программирование микроконтроллеров pic16

- •Краткие сведения об архитектуре микроконтроллеров pic16 и принципе их работы

- •Язык ассемблера pic16

- •Команды пересылки

- •Арифметические команды

- •Булевы операции

- •Битовые операции

- •Операции условного, безусловного переходов и вызова подпрограмм

- •Общий вид программы и типовые приемы программирования

- •Битовая арифметика

- •Ветвление

- •Вызов подпрограммы

- •Использование среды mplab

- •Моделирование комбинационных автоматов

- •Метод непосредственного вычисления фал

- •Метод бинарных функций

- •Метод адресных переходов (табулирование функций)

- •Приложение а. Исходные тексты примеров а.1. Применение метода непосредственного вычисление фал

- •А.2. Применение метода бинарных программ

- •А.3. Применение метода адресных переходов а.3.1. Способ размещения таблицы в пзу

- •А.3.2. Способ размещения таблицы в озу

- •А.4. Модуль hdw_init

- •Приложение б. Краткий справочник инструкций pic16

- •Библиография

- •Имитационное моделирование дискретных устройств

- •620034, Екатеринбург, ул. Колмогорова, 66.

Элементы памяти полупроводниковых устройств

Классификация триггерных устройств

Подавляющее большинство дискретных устройств, используемых для управления объектами, содержит элементы памяти, предназначенные для длительного или кратковременного хранения информации о состоянии объекта или управляющей системы. В подобных устройствах чаще всего для хранения информации используют триггеры – устройства с двумя устойчивыми состояниями.

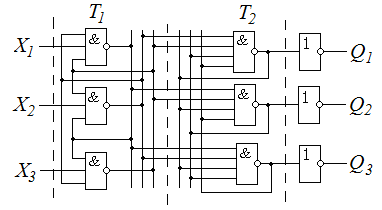

На рис. 1.6 приведена схема триггера с тремя устойчивыми состояниями, однако подобные элементы памяти применяются довольно редко.

Обобщённая схема триггерного устройства приведена на рис. 1.5.

Рис. 1.5. Обобщённая схема триггерного устройства

_

где Q, Q – выходы;

x1,…, xn – информационные входы;

C1, …, Cm – входы синхронизации (тактовые входы);

V1, …, Vk – управляющие входы;

Sу, Ry – установочные входы;

S*, R* – информационные входы элементарной запоминающей ячейки.

Коммутационные входы используются для внешних соединений в программируемых универсальных триггерах. В реальных схемах триггеров некоторые входные сигналы и связи, указанные на рис. 1.5, могут отсутствовать, а в простейших триггерах не предусматриваются схемы управления.

Входы S и R являются входами раздельной установки триггеров в состояние «1» или «0», входы С разрешают схеме управления записать информацию в триггер.

Вход V (Valve – клапан, вентиль) – управляющий вход для разрешения приёма информационных, или тактовых импульсов.

В некоторых схемах триггеров используются обозначения, отличные от выше перечисленных: J (Jerk – внезапное включение) – импульсный вход для раздельной установки JK – триггера в единичное состояние (Q =1), K – импульсный вход для раздельной установки JK – триггера в нулевое состояние (Q =0), Т (Toggle – релаксатор) – счётный вход триггера, D – информационный вход для установки триггера в состояние «0» или «1».

Классификация триггеров может производиться по различным определяющим признакам.

По способу организации логических связей различают триггеры с раздельной установкой состояния «0» и «1» (статические RS-триггеры и динамические JK-триггеры); со счётным входом (Т-триггеры); с приёмом информации по одному входу (D-триггеры); комбинированные со сложной входной логикой (например, RST-, JKRS-, DRS-триггеры).

По способу записи информации триггеры подразделяются на несинхронизируемые (асинхронные, нетактируемые) и синхронизируемые (синхронные, тактируемые). В свою очередь синхронизируемые триггеры бывают со статическим или динамическим управлением.

В синхронных триггерах со статическим управлением записью тактовый импульс начинает оказывать влияние только тогда, когда его уровень достигнет уровня срабатывания триггера (переключение триггера единицей) или когда уровень сигнала станет меньше определённого значения (переключение триггера нулём). Триггеры, состояние которых изменяется в интервале действия тактового импульса (нуля или единиц), называют триггерами, срабатывающими по уровню. Если состояние триггера изменяется по окончании действия уровней единицы или нуля тактового импульса, эти триггеры являются триггерами с внутренней задержкой. В синхронных триггерах с динамическим управлением записью информация поступает в момент изменения амплитуды тактового импульса в определённом направлении, т.е. во время нарастания или спада его фронта.

По

количеству информационных входов

триггеры могут быть одновходовые,

двухвходовые и многовходовые. Наибольшее

распространение получили одно- и

двухвходовые триггеры. Не следует путать

количество информационных входов с

количеством фактических входов, на

которые поступают информационные

сигналы, так как реально действующий

информационный вход в структуре триггера

может быть конъюнкцией, дизъюнкцией

или какой либо функцией нескольких

логических переменных, действующих на

информационные входы, например, J

= J1

& J2

& J3;

K

= K1

& K2

V

K3;

J

= J1

V

J2

V

J3

и т.п.

По

количеству информационных входов

триггеры могут быть одновходовые,

двухвходовые и многовходовые. Наибольшее

распространение получили одно- и

двухвходовые триггеры. Не следует путать

количество информационных входов с

количеством фактических входов, на

которые поступают информационные

сигналы, так как реально действующий

информационный вход в структуре триггера

может быть конъюнкцией, дизъюнкцией

или какой либо функцией нескольких

логических переменных, действующих на

информационные входы, например, J

= J1

& J2

& J3;

K

= K1

& K2

V

K3;

J

= J1

V

J2

V

J3

и т.п.

По количеству тактовых входов различают триггеры однотактные, двухтактные и многотактные.

По виду выходных сигналов триггеры бывают статические, у которых выходные сигналы в устойчивом состоянии остаются неизменными во времени, и динамические, выходные сигналы которых в устойчивом состоянии изменяются во времени.

По способу хранения информации различают триггеры с активным хранением информации (выходной информационный сигнал действует постоянно) и с пассивным хранением информации (выходной сигнал может быть получен только с помощью специального опросного сигнала).

Число внутренних состояний триггера, как правило, равно двум. Однако на практике можно встретить триггеры с бÓльшим числом состояний.

На рис. 1.6 приведена схема триггера, имеющего три устойчивых состояния. Характерной особенностью данного триггера является то, что он изменяет своё состояние только в том случае, когда на его входах одна единица и два нуля. При поступлении на входы триггера любых комбинаций сигналов (две, три единицы или все нули) сохраняется его предыдущее внутреннее состояние, и сигналы на выходах не изменяются.

Рис. 1.6. Триггер, имеющий три устойчивых состояния

Приведённый на рис. 1.6 триггер состоит из двух элементарных триггеров Т1 и Т2. Первый из них сохраняет предыдущее состояние при появлении на входах двух или трёх единиц. Второй элементарный триггер не изменяет своего состояния при появлении на входах X трёх нулей.