- •Оглавление

- •Введение

- •Методы разработки алгоритмов и программ имитационных моделей комбинационных схем и последовательных автоматов с памятью

- •Методы разработки алгоритмов имитационных моделей комбинационных схем

- •Непосредственнее решение функций алгебры логики

- •Метод бинарных функций

- •Решение функции алгебры логики методом адресных переходов

- •Элементы памяти полупроводниковых устройств

- •Классификация триггерных устройств

- •Триггер как элементарный последовательный автомат

- •Наиболее популярные методы разработки алгоритмов и программ имитационных моделей с памятью

- •Асинхронные триггеры

- •Асинхронный rs-триггер

- •Асинхронные s-, r- и e-триггеры

- •Асинхронный d-триггер

- •Асинхронные т-триггеры

- •Асинхронные jk-триггеры с импульсным управлением

- •Асинхронные потенциально управляемые jk-триггеры

- •Синхронные (тактируемые) триггеры

- •Синхронный rs-триггер

- •Синхронный d-триггер

- •Синхронный jk-триггер

- •Универсальные d- и jk-триггеры

- •Примеры схем, построенных с применением jk-триггера к155тв1

- •Пример разработки имитационной модели триггерного устройства

- •Непосредственное решение уравнений, описывающих работу триггерной установки

- •Использование графа состояний триггерного устройства для разработки алгоритма

- •Применение таблицы переходов для решения поставленной задачи

- •Реализация дискретных устройств на микроконтроллерах pic16

- •Введение в программирование микроконтроллеров pic16

- •Краткие сведения об архитектуре микроконтроллеров pic16 и принципе их работы

- •Язык ассемблера pic16

- •Команды пересылки

- •Арифметические команды

- •Булевы операции

- •Битовые операции

- •Операции условного, безусловного переходов и вызова подпрограмм

- •Общий вид программы и типовые приемы программирования

- •Битовая арифметика

- •Ветвление

- •Вызов подпрограммы

- •Использование среды mplab

- •Моделирование комбинационных автоматов

- •Метод непосредственного вычисления фал

- •Метод бинарных функций

- •Метод адресных переходов (табулирование функций)

- •Приложение а. Исходные тексты примеров а.1. Применение метода непосредственного вычисление фал

- •А.2. Применение метода бинарных программ

- •А.3. Применение метода адресных переходов а.3.1. Способ размещения таблицы в пзу

- •А.3.2. Способ размещения таблицы в озу

- •А.4. Модуль hdw_init

- •Приложение б. Краткий справочник инструкций pic16

- •Библиография

- •Имитационное моделирование дискретных устройств

- •620034, Екатеринбург, ул. Колмогорова, 66.

Универсальные d- и jk-триггеры

Наиболее часто разработчики аппаратуры используют универсальные D- и JK-триггеры, входящие в состав широко распространенных серий К133, КМ133, К155, КМ155 и др. Эти триггеры могут работать в различных режимах и в качестве различных типов триггеров.

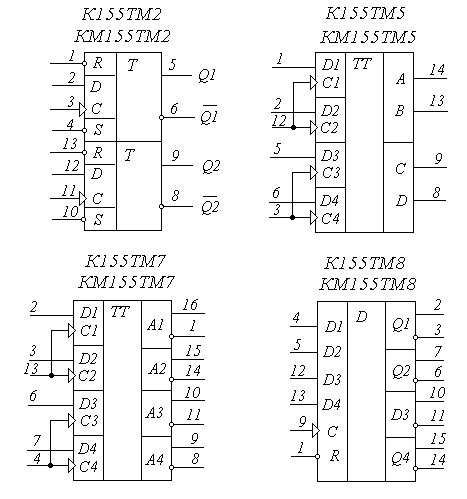

Варианты D-триггеров серии К155 приведены на рис. 1.50.

В микросхеме К155ТМ2 содержится два независимых D-триггера, имеющих дополнительно инверсные входы R и S. Эти триггеры можно использовать в качестве тактируемых RS-триггеров или D-триггеров. Использование этих триггеров в качестве других, рассмотренных выше триггеров (S-, R- или Е-триггеров), достигается дополнением схем логическими элементами И-НЕ, ИЛИ-НЕ или И, ИЛИ, НЕ. При этом графы, таблицы переходов и функции алгебры логики идентичны описаниям работы триггеров, приведённых выше.

Рис. 1.50. Варианты D-триггеров серии К155

1.5.4.1. Пример № 1. Применение D-триггера типа К155ТМ2

для произвольного триггерного устройства

Предлагается разработать схему триггерного устройства, выполняющую функции произвольного триггера, таблица истинности которого приведена в табл. 1.9.

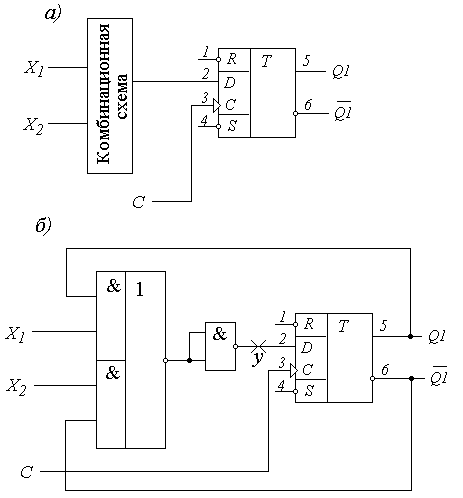

На рис. 1.51 приведён пример использования D-триггера для реализации произвольной триггерной структуры, где показаны структурная и принципиальная схемы, функционирующие в соответствии с табл. 1.9.

Таблица 1.9

Рис. 1.51. Структурная и принципиальная схемы триггера,

функционирующего в соответствии с табл. 1.9

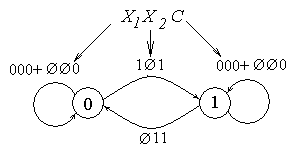

Рис. 1.52. Граф состояний схемы рис. 3.13

Ø – любое значение переменной

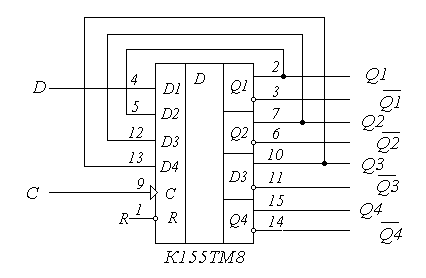

1.5.4.2. Регистр сдвига на микросхеме К155ТМ8

Рис. 1.53. Регистр сдвига

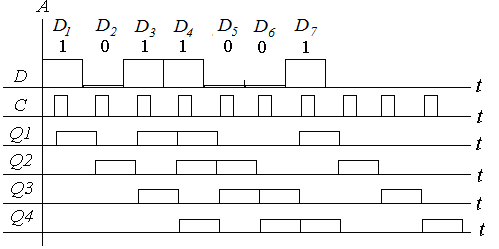

Рис. 1.54. Временная диаграмма передачи кода 1011001

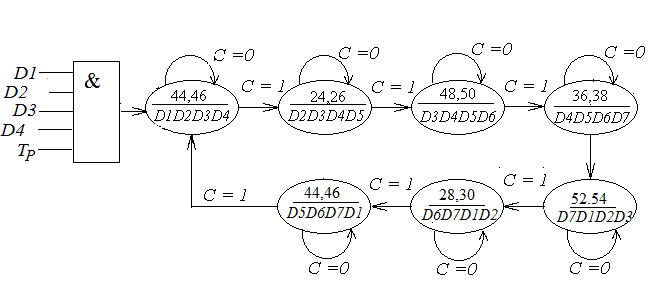

Рис. 1.55. Граф состояний регистра сдвига

В числителях дробей, помещённых в овалы, указываются номера строк таблицы переходов, соответствующие передаче сообщения, изображённого на временной диаграмме рис. 1.54, в знаменателе – состояние триггеров Передаваемое сообщение:

D1= 1, D2 = 0, D3 = 1, D4 = 1, D5 = 0, D6 = 0, D7 =1.

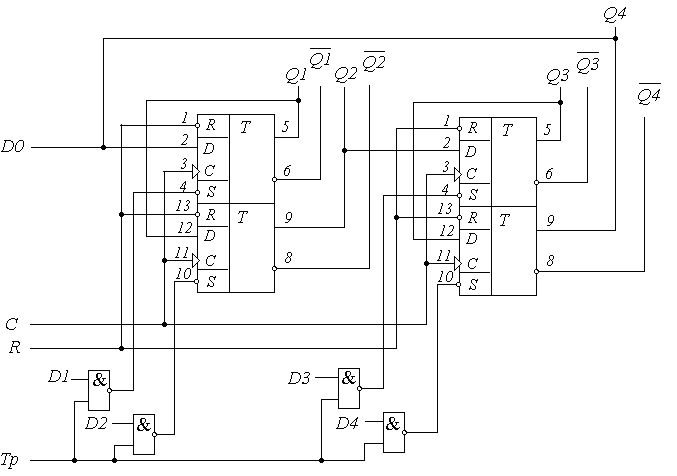

На рис. 1.56 приведена схема регистра с параллельной записью информации и обратной связью [4]. При появлении единицы на входе Тр в регистры записываются сигналы, подаваемые на входы D1, D2, D3 и D4. Поскольку предусмотрено соединение выхода Q4 с входом D0, эти данные будут передаваться на выход Q4 циклически.

Рис. 1.57. Схема регистра с параллельной записью и

обратной связью

Рис. 1.58. Граф состояний регистра с параллельной

записью и обратной связью

Примеры схем, построенных с применением jk-триггера к155тв1

Входы и выходы микросхем К155ТВ1 и КМ155ТВ1 показаны на рис. 1.59 а, здесь же приведена таблица, описывающая работу триггера. Переключение триггера происходит по срезу импульса на тактовом входе С (в момент перехода единицы в ноль).

Рис. 1.59. Микросхема JK-триггера типа К155В1

Микросхема К155ТВ1 отличается от рассмотренных выше тактируемых потенциальных JK-триггеров тем, что на входах J и K установлены схемы И на три входа (отключение входа от источника питания воспринимается схемой как единица).

Эта микросхема работает аналогично рассмотренным выше схемам, изображённым на рис. 1.51 и 1.53.

1.5.5.1. Произвольный триггер на микросхеме К155ТВ1 (рис. 1.60)

Это тактируемый триггер, переходящий в нулевое состояние в момент появления нуля на тактовом входе С при одновременном поступлении единиц или нулей на оба входа J и K (J = J1J2J3; K =K1K2R3).

![]()

Рис. 1.60. Таблица истинности и

принципиальная схема триггера, построенного

с использованием микросхемы К155ТВ1

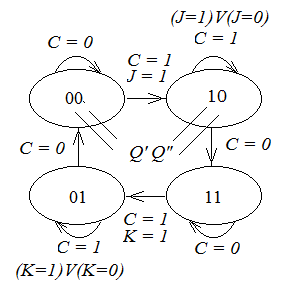

Рис. 1.61. Граф состояний триггерного устройства рис. 1.60

1.5.5.2. Двоичный счётчик на микросхемах К155ТВ1

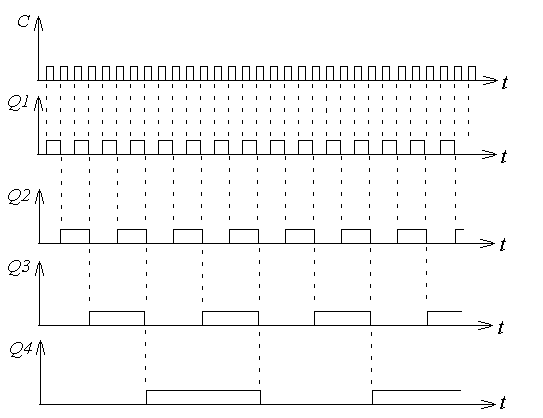

При подаче на входы J и K единиц микросхема К155ТВ1 работает как потенциальный Т-триггер [3]. В момент подачи на С-вход микросхемы единицы изменяет своё состояние на противоположное вспомогательный триггер. Нулевой потенциал на С-вход (по срезу импульса) переходит в это же состояние и головной триггер. При этом каждый последующий триггер работает с частотой в два раза ниже частоты работы предыдущего триггера. Временная диаграмма работы схемы приведена на рис. 1.63.

|

Рис. 1.62. Двоичный счётчик на триггерах К155ТВ1 |

Рис. 1.63. Временная диаграмма работы двоичного счётчика

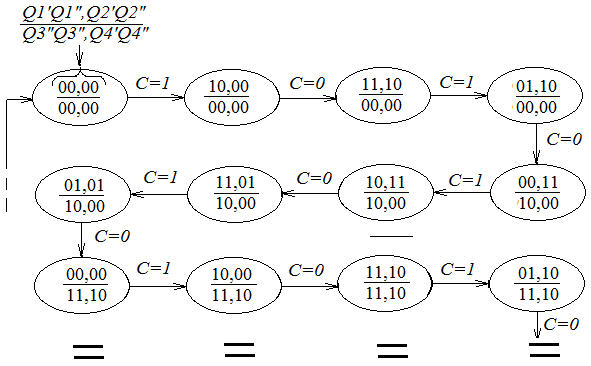

Рис. 1.64. Граф состояний двоичного счётчика

Граф состояний двоичного счётчика, изображённого на рис. 1.61, будет иметь 32 устойчивых состояния. На рис. 1.64 показана только часть графа.