- •Конспект лекций

- •Могилев, 2007

- •Тема 1. Введение

- •Тема 2. Полупроводниковые приборы

- •1.1. Электронные приборы.

- •1.2. Полупроводниковые материалы. Собственная и примесная электропроводность. Электронно-дырочные p-n переход и его свойства

- •1.3 Полупроводниковые диоды.

- •Раздел 2. Электронные аналоговые устройства

- •2.1. Электронные усилители электрических сигналов, классификация и основные параметры усилителей.

- •2.2. Принцип построения усилительного каскада: выбор рабочего режима, назначение и расчет основных элементов.

- •2.3. Обратная связь в усилителях. Виды, назначение ос.

- •2.5. Генераторы электрических сигналов.

- •Раздел 3. Электронные цифровые устройства

- •3.1. Основные логические понятия, типовые логические функции и элементы (и, или, не, и-не, или-не, исключающее или.

- •Схемная реализация логических элементов. Их основные параметры.

- •3.3. Триггеры: общая структура и классификация. Назначение и принцип действия триггеров типа: rs-, d-, jk-, т-.

- •3.4. Счетчики. Назначение, устройство, классификация, принцип действия, область применения. Типовые интегральные схемы счетчиков.

- •3.5. Регистры. Принцип действия, область применения. Типовые интегральные схемы регистров.

- •3.6. Шифраторы и дешифраторы. Назначение, устройство, область применения. Типовые интегральные схемы шифраторов и дешифраторов.

- •3.7. Сумматоры. Назначение, устройство, классификация, принцип действия. Типовые интегральные схемы сумматоров.

- •3.8. Цифроаналоговые и аналого-цифровые преобразователи.

- •3.9. Запоминающие устройства: назначение, принцип построения и программирования. Типовые интегральные схемы.

- •Раздел 4. Микропроцессорная техника.

- •4.1. Назначение, устройство, характеристики и принцип действия микропроцессора. Арифметические и логические основы представления информации.

- •4.2. Типовая структура микропроцессорной системы.

- •4.3. Этапы проектирования микропроцессорных систем управления (мпсу).

- •4.4. Разработка и выбор аппаратной части микропроцессорного устройства (мпу). Выбор микропроцессорного комплекта. Организация модуля памяти. Средства сопряжения.

- •4.5. Разработка программного обеспечения и отладка микропроцессорного устройства (мпу). Система команд. Способы адресации.

- •4.6. Микропроцессорное устройство управления на основе мпк к580

3.5. Регистры. Принцип действия, область применения. Типовые интегральные схемы регистров.

Регистры – функциональные узлы, предназначенные для приема, хранения, передачи и преобразования информации.

Используются в качестве управляющих и запоминающих устройств генераторов и преобразователей кодов, счетчиков и делителей частоты, узлов временной задержки. Строятся на синхронных триггерах с динамическим или статическим управлением. Занесение информации в регистр называется операцией ввода или записью. Выдача информации к внешним устройствам характеризует операцию вывода или считывание. Запись информации в регистр не требует его предварительного обнуления.

Регистры делятся на:

сдвигающие

накопительные (памяти, хранения)

универсальные.

Регистры памяти предназначены для хранения двоичной информации небольшого объема в течение короткого промежутка времени. Представляют собой набор синхронных триггеров, каждый из которых хранит один разряд двоичного числа. Ввод и вывод информации производится одновременно во всех разрядах параллельного кода. Ввод обеспечивается тактовым командным импульсом. Считывание может производиться в прямом и обратном коде (с инверсных выходов).

Регистры сдвига. Сущность сдвига – с приходом каждого тактового импульса происходит перезапись (сдвиг) содержимого триггера каждого разряда в соседний разряд без изменения порядка следования «0» и «1». При сдвиге вправо бит из более старшего разряда сдвигается в младший. При сдвиге влево – наоборот.

Сдвигающие регистры классифицируются:

по способу ввода и вывода информации на:

параллельные

последовательные

комбинированные

по направлению сдвига на:

однонаправленные

реверсивные

Обозначаются: RG ←, → и ↔ (влево, вправо и реверсивные)

Универсальные в зависимости от управляющих сигналов могут выполнять как операцию хранения, так и сдвиг.

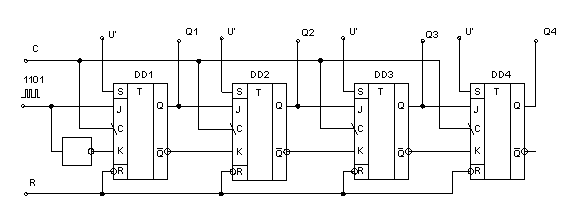

4-х разрядный сдвигающий регистр с последовательным вводом.

Допустим, что в регистр последовательно вводится начиная с младшего разряда двоичный код 1101, который поступает с внешнего устройства синхронно с тактовыми импульсами. С первым тактовым импульсом в триггер DD1 записывается «1» младшего разряда. Со следующим тактовым импульсом эта «1» будет сдвинута в триггер DD2 и окажется на его выходе. Одновременно в 1-ый триггер запишется «0». После 4-х тактовых импульсов параллельный код на выходах Q1—Q4 будет соответствовать последовательному входному. После пятого тактового импульса сигнал, бывший на выходе Q4 выводится из регистра и пропадает. После 8 тактов регистр полностью очищен.

Дополнительная логика позволяет вводить информацию параллельно и снимать последовательно.

Сдвигающийся регистр может быть использован в качестве кольцевого счетчика или счетчика Джонса, который применяется для последовательного вывода информации без ее стирания.

Для этого информация с выхода регистра по цепи ОС снова вводится на вход. Пока на V единица, информация вводится в регистр по входу D и обратная связь не действует. За n тактов запоминается n разрядный код. Затем на V устанавливается «0» тактовыми импульсами по входу С. Информация с выхода Qn снова вводится в регистр одновременным последовательным (возможно и параллельным) считыванием и через n тактов находится в исходном состоянии.

К155ИР-1

Ч етырехразрядный

регистр сдвига с последовательным или

параллельным вводом информации и

параллельным выводом (может быть и

последовательным).

Он может выполнять:

етырехразрядный

регистр сдвига с последовательным или

параллельным вводом информации и

параллельным выводом (может быть и

последовательным).

Он может выполнять:

ввод информации параллельным кодом

ввод информации последовательным кодом со сдвигом влево

ввод информации последовательным кодом со сдвигом вправо

хранение.

Регистр имеет:

2 тактовых входа С1 и С2.

управляющий вход выбора режима V2

5 информационных входов (V1 для ввода в последовательном коде, D1-D4 для записи в параллельном коде)

4 выхода Q1-Q4.

Ввод информации параллельным кодом осуществляется при V2=1 и C2=0. Сдвиг информации в триггерах происходит по перепаду 1-0 на С2. Входы V1 и C1 при этом блокированы. В этом же режиме по входам V2, С2 производится преобразование последовательного кода в параллельный со сдвигом влево. В этом случае поток информации происходит в обратном направлении. Для этого соединяют Q4 – D3, Q3 – D2, Q2 – D1. Информация подается на D4. Сдвиг влево по перепаду 1-0 на С2.

V2 |

V1 |

С1 |

С2 |

|

1 |

X |

X |

10 |

запись параллельного кода, сдвиг влево |

0 |

вход |

10 |

X |

запись последовательного кода, сдвиг вправо |

Во избежание сбоев при смене состояний V2 должна происходить при C1=C2=0.

Ввод информации последовательным кодом: входная информация подается на V1, а тактовые импульсы на С1. Сдвиг вправо происходит при каждом перепаде 10 тактовых импульсов.