- •Московский государственный институт

- •Лекция 1. Базовые понятия информации Введение

- •Информация, энтропия и избыточность при передаче данных

- •Информационные процессы

- •Основные структуры данных

- •Обработка данных

- •Способы представления информации и два класса эвм

- •Кодирование информации

- •Представление данных в эвм.

- •Форматы файлов

- •Кодирование чисел

- •Кодирование текста

- •Кодирование графической информации

- •Кодирование звука

- •Типы данных

- •Вопросы и задания

- •Лекция 2. Компьютер – общие сведения

- •Материнская плата

- •Интерфейсные шины

- •Основные внешние устройства компьютера

- •Вопросы и задания

- •Лекция 3. Многоуровневая компьютерная организация

- •Архитектура компьютера

- •Классическая структура эвм - модель фон Неймана

- •Особенности современных эвм

- •Вопросы и задания

- •Библиотеки стандартных программ и ассемблеры

- •Высокоуровневые языки и системы автоматизированного программирования

- •Диалоговые ос и субд

- •Прикладные программы иCase– технологии

- •Компьютерные сети и мультимедиа

- •Операционные системы

- •Лекция 5.Вычислительные системы - общие сведения Введение

- •Общие требования

- •Классификация компьютеров по областям применения

- •Персональные компьютеры и рабочие станции

- •Суперкомпьютеры

- •Увеличение производительности эвм, за счет чего?

- •Параллельные системы

- •Использование параллельных вычислительных систем

- •Закон Амдала и его следствия

- •Вопросы и задания

- •Лекция 6. Структурная организация эвм - процессор Введение

- •Что известно всем

- •Микропроцессорная система

- •Что такое микропроцессор?

- •Назначение элементов процессора

- •Устройство управления

- •Микропроцессорная память

- •Структура адресной памяти процессора

- •Интерфейсная часть мп

- •Тракт данных типичного процессора

- •Базовые команды

- •Трансляторы

- •Архитектура системы команд и классификация процессоров

- •Микроархитектура процессораPentiumIi

- •512 Кбайт

- •Вопросы и задания

- •Лекция 7. Структурная организация эвм - память Общие сведения

- •Верхняя

- •Расширенная

- •Верхняя память (Upper Memory Area) – это 384 Кбайт, зарезервированных у верхней границы системной памяти. Верхняя память разделена на несколько частей:

- •Первые 128 Кбайт являются областью видеопамяти и предназначены для использовании видеоадаптерами, когда на экран выводится текст или графика, в этой области хранятся образы изображений;

- •Видеопамять

- •Иерархия памяти компьютера

- •Оперативная память, типы оп

- •Тэг Строка Слово (байт)

- •Способы организации кэш-памяти

- •1. Где может размещаться блок в кэш-памяти?

- •2. Как найти блок, находящийся в кэш-памяти?

- •3. Какой блок кэш-памяти должен быть замещен при промахе?

- •4. Что происходит во время записи?

- •Разновидности строения кэш-памяти

- •Вопросы и задания

- •Лекция 8. Логическая организация памяти

- •Виртуальная память

- •Основная память

- •Дисковая память

- •Страничная организация памяти

- •Преобразование адресов

- •Сегментная организация памяти.

- •Свопинг

- •Вопросы и задания

- •Лекция 9. Методы адресации

- •Лекция 10. Внешняя память компьютера Введение

- •Жесткий диск (Hard Disk Drive)

- •Конструкция жесткого диска

- •Основные характеристики нмд:

- •Способы кодирования данных

- •Интерфейсы нмд

- •Структура хранения информации на жестком диске

- •Кластер

- •Методы борьбы с кластеризацией

- •Магнито-оптические диски

- •Дисковые массивы и уровни raid

- •Лазерные компакт-дискиCd-rom

- •Вопросы и задания

- •Лекция 11. Основные принципы построения систем ввода/вывода

- •Физические принципы организации ввода-вывода

- •Интерфейс

- •Магистрально-модульный способ построения эвм

- •Структура контроллера устройства

- •Опрос устройств и прерывания. Исключительные ситуации и системные вызовы

- •Организация передачи данных

- •Прямой доступ к памяти (Direct Memory Access – dma)

- •Логические принципы организации ввода-вывода

- •Структура системы ввода-вывода

- •Буферизация и кэширование

- •Структура шин современного пк

- •Мост pci

- •Вопросы и задания

- •Лекция 12. Особенности архитектуры современных высокопроизводительных вс

- •Классификация архитектур по параллельной обработке данных

- •Вычислительные Системы

- •Параллелизм вычислительных процессов

- •Параллелизм на уровне команд – однопроцессорные архитектуры

- •Конвейерная обработка

- •Суперскалярные архитектуры

- •Мультипроцессорные системы на кристалле

- •Технология Hyper-Threading

- •Многоядерность — следующий этап развития

- •Вопросы и задания

- •Лекция 13. Архитектура многопроцессорных вс Введение

- •Smp архитектура

- •MpPархитектура

- •Гибридная архитектура (numa)

- •Организация когерентности многоуровневой иерархической памяти.

- •Pvp архитектура

- •Кластерная архитектура

- •Проблемы выполнения сети связи процессоров в кластерной системе.

- •Лекция 14. Кластерные системы

- •Концепция кластерных систем

- •Разделение на High Availability и High Performance системы

- •Проблематика High Performance кластеров

- •Проблематика High Availability кластерных систем

- •Смешанные архитектуры

- •Лекция 15 Многомашинные системы – вычислительные сети Введение

- •Простейшие виды связи сети передачи данных

- •Связь компьютера с периферийным устройством

- •Связь двух компьютеров

- •Многослойная модель сети

- •Функциональные роли компьютеров в сети

- •Одноранговые сети

- •Сети с выделенным сервером

- •Гибридная сеть

- •Сетевые службы и операционная система

- •Лекция 17. Сети и сетевые операционные системы Введение

- •Для чего компьютеры объединяют в сети

- •Сетевые и распределенные операционные системы

- •Взаимодействие удаленных процессов как основа работы вычислительных сетей

- •Основные вопросы логической организации передачи информации между удаленными процессами

- •Понятие протокола

- •Многоуровневая модель построения сетевых вычислительных систем

- •Проблемы адресации в сети

- •Одноуровневые адреса

- •Двухуровневые адреса

- •Удаленная адресация и разрешение адресов

- •Локальная адресация. Понятие порта

- •Полные адреса. Понятие сокета (socket)

- •Проблемы маршрутизации в сетях

- •Связь с установлением логического соединения и передача данных с помощью сообщений

- •Синхронизация удаленных процессов

- •Заключение

- •Список литературы:

Pvp архитектура

PVP (Parallel Vector Process) - параллельная архитектура с векторными процессорами. Основным признаком PVP-систем является наличие специальных векторно-конвейерных процессоров, в которых предусмотрены команды однотипной обработки векторов независимых данных, эффективно выполняющиеся на конвейерных функциональных устройствах. Как правило, несколько таких процессоров (1-16) работают одновременно с общей памятью (аналогично SMP) в рамках многопроцессорных конфигураций. Несколько таких узлов могут быть объединены с помощью коммутатора (аналогично MPP). Поскольку передача данных в векторном формате осуществляется намного быстрее, чем в скалярном (максимальная скорость может составлять 64 Гб/с, что на 2 порядка быстрее, чем в скалярных машинах), то проблема взаимодействия между потоками данных при распараллеливании становится несущественной. И то, что плохо распараллеливается на скалярных машинах, хорошо распараллеливается на векторных. Таким образом, системы PVP архитектуры могут являться машинами общего назначения (general purpose systems). Однако, поскольку векторные процессоры весьма дороги, эти машины не будут являться общедоступными.

Кластерная архитектура

Кластер представляет собой два или больше компьютеров (часто называемых узлами), объединяемых при помощи сетевых технологий на базе шинной архитектуры или коммутатора и предстающих перед пользователями в качестве единого информационно-вычислительного ресурса. В качестве узлов кластера могут быть выбраны серверы, рабочие станции и даже обычные персональные компьютеры. Преимущество кластеризации для повышения работоспособности становится очевидным в случае сбоя какого-либо узла: при этом другой узел кластера может взять на себя нагрузку неисправного узла, и пользователи не заметят прерывания в доступе. Возможности масштабируемости кластеров позволяют многократно увеличивать производительность приложений для большего числа пользователей. технологий (Fast/Gigabit Ethernet, Myrinet) на базе шинной архитектуры или коммутатора. Такие суперкомпьютерные системы являются самыми дешевыми, поскольку собираются на базе стандартных комплектующих элементов ("off the shelf"), процессоров, коммутаторов, дисков и внешних устройств. Кластеризация может быть осуществлена на разных уровнях компьютерной системы, включая аппаратное обеспечение, операционные системы, программы-утилиты, системы управления и приложения. Чем больше уровней системы объединены кластерной технологией, тем выше надежность, масштабируемость и управляемость кластера.

Проблемы выполнения сети связи процессоров в кластерной системе.

Архитектура кластерной системы (способ соединения процессоров друг с другом) в большей степени определяет ее производительность, чем тип используемых в ней процессоров. Критическим параметром, влияющим на величину производительности такой системы, является расстояние между процессорами. Так, соединив вместе 10 персональных компьютеров, мы получим систему для проведения высокопроизводительных вычислений, проблема, однако, будет состоять в нахождении наиболее эффективного способа соединения стандартных средств друг с другом, поскольку при увеличении производительности каждого процессора в 10 раз производительность системы в целом в 10 раз не увеличится.

Рассмотрим для примера задачу построения симметричной 16-ти процессорной системы, в которой все процессоры были бы равноправны. Наиболее естественным представляется соединение в виде плоской решетки, где внешние концы используются для подсоединения внешних устройств.

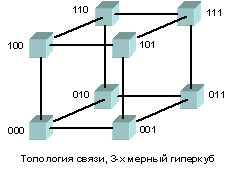

Схема соединения процессоров в виде плоской решетки

При таком типе соединения максимальное расстояние между процессорами окажется равным 6 (количество связей между процессорами, отделяющих самый ближний процессор от самого дальнего). Теория же показывает, что если в системе максимальное расстояние между процессорами больше 4, то такая система не может работать эффективно. Поэтому, при соединении 16 процессоров друг с другом плоская схема является не эффективной. Для получения более компактной конфигурации необходимо решить задачу о нахождении фигуры, имеющей максимальный объем при минимальной площади поверхности. В трехмерном пространстве таким свойством обладает шар. Но поскольку нам необходимо построить узловую систему, то вместо шара приходится использовать куб (если число процессоров равно 8) или гиперкуб, если число процессоров больше 8. Размерность гиперкуба будет определяться в зависимости от числа процессоров, которые необходимо соединить. Так, для соединения 16 процессоров потребуется 4-х мерный гиперкуб. Для его построения следует взять обычный 3-х мерный куб, сдвинуть в еще одном направлении и, соединив вершины, получить гиперкуб размером 4.

Примеры гиперкубов

Архитектура гиперкуба является второй по эффективности, но самой наглядной. Используются и другие топологии сетей связи: трехмерный тор, "кольцо", "звезда" и другие.

Архитектура кольца с полной связью по хордам (Chordal Ring)

Наиболее эффективной является архитектура с топологией "толстого дерева" (fat-tree). Архитектура "fat-tree" (hypertree) предложена Лейзерсоном (Charles E. Leiserson) в 1985 году. Процессоры локализованы в листьях дерева, в то время как внутренние узлы дерева скомпонованы во внутреннюю сеть. Поддеревья могут общаться между собой, не затрагивая более высоких уровней сети.

Кластерная архитектура "Fat-tree"

Кластерная архитектура "Fat-tree" (вид сверху на предыдущую схему)

Поскольку способ соединения процессоров друг с другом больше влияет на производительность кластера, чем тип используемых в ней процессоров, то может оказаться более рентабельным создать систему из большего числа дешевых компьютеров, чем из меньшего числа дорогих. В кластерах, как правило, используются операционные системы, стандартные для рабочих станций, чаще всего, свободно распространяемые - Linux, FreeBSD, вместе со специальными средствами поддержки параллельного программирования и балансировки нагрузки. При работе с кластерами, также как и с MPP системами, используют так называемую Massive Passing Programming Paradigm - парадигму программирования с передачей данных (чаще всего - MPI). Дешевизна подобных систем оборачивается большими накладными расходами на взаимодействие параллельных процессов между собой, что сильно сужает потенциальный класс решаемых задач.

Выводы

Классификация Флинна позволяет распределить параллельные вычисления по уровням архитектуры вычислительных систем.

Сравнивая между собой ММВС и МПВС, можно отметить, что в МПВС достигается более высокая скорость обмена информацией между элементами системы и поэтому более высокая производительность, более высокая живучесть и надежность.

ММВС на стандартных ОС значительно проще и дешевле.

Вопросы и задания

Привести примеры практической реализации архитектуры SISD,SIMD,MISDиMIMD.

Какая архитектура более пригодна для обработки мультимедийных задач?

Что из себя представляет архитектура MSIMD?