- •Программирование цифровой техники и микроконтроллеров управления

- •Алматы 2012

- •1 Микроконтроллеры в современном мире

- •1.1 Краткая история развития микроконтроллеров

- •1.2 Задачи и роль микроконтроллеров

- •2 Выполнение арифметических операций в мп

- •2.1 Системы счислений

- •2.2 Двоичная арифметика

- •2.3 Дополнительный код

- •2.4 Знаковый разряд

- •3 Регистры общего и специального назначения

- •3.1 Регистры portc и trisc

- •3.2 Регистр Status

- •3.3 Фиксированная (абсолютная) адресация

- •4 Косвенная адресация. Логика

- •4.1 Косвенная адресация

- •4.2 Логические функции

- •5 Маскирование. Стек

- •5.1 Маскирование

- •5.2 Счетчик команд

- •5.3 Стек

- •6 Конвейер и подпрограмма задержки

- •6.1 Конвейер

- •6.2 Программа задержки

- •6.3 Расчет времени задержки

- •7 Выполнение умножения и деления

- •7.1 Умножение и деление при помощи сдвига

- •7.2 Инструкции условных переходов

- •7.3 Целочисленное умножение

- •7.4 Целочисленное деление

- •7.5 Умножение на дробное число

- •8 Программирование клавиатуры. Дешифратор

- •8.1 Клавиатура

- •8.2 Фрагменты программы

- •8.3 Дешифратор

- •8.4 Компаратор

- •9 Основные элементы цифровой техники

- •9.1 Сумматор

- •9.2 Арифметико-логическое устройство

- •9.3 Бистабильные схемы

- •9.4 Триггеры и регистры

- •10 Структура микроконтроллера. Индикатор

- •10.1 Применение операций сдвига

- •10.2 Цифровой индикатор

- •10.2 Структурная схема мк

- •11 Прерывания и сторожевой таймер

- •11.1 Прерывания

- •11.2 Подсчет посетителей с помощью прерываний

- •11.3 Сторожевой таймер

- •12 Фактор времени и аналоговый мир

- •12.1 Модуль таймера tmr1

- •12.2 Применение таймера tmr1

- •12.3 Аналоговый мир

- •Приложение а Список некоторых сокращений

- •Список литературы

- •Содержание

- •050013, Алматы, Байтурсынова, 126

9.2 Арифметико-логическое устройство

Таблица 9.1 - АЛУ

S2 S1 S0 |

Операция |

0 0 0 |

Сброс (F=0000) |

0 0 1 |

Вычитание (В-А) |

0 1 0 |

Вычитание (А-В) |

0 1 1 |

Сложение (А+В) |

1 0 0 |

Искл. ИЛИ (АВ) |

1 0 1 |

ИЛИ (А+В) |

1 1 0 |

И (А*В) |

1 0 1 |

Установка (F=1111) |

Микросхема, таблица истинности которой приведена в таблице 9.1, выполняет 8 операций над двумя 4-битными числами. Выполняемая операция задается тремя битами выбора режима S0S1S2. Кроме сложения и вычитания, это АЛУ выполняет также операции OR, AND и XOR. Микросхема формирует также признак переполнения дополнительного кода.

9.3 Бистабильные схемы

Все рассмотренные ранее схемы, относятся к классу комбинационных схем. Значение их выходов зависит только от состояния входов в данный момент времени и не зависит от предыдущих событий. Такие же логические схемы, как защелки, счетчики, регистры и оперативная память (допускающая как чтение, так и запись), относятся к классу последовательных схем. Состояние выходов таких схем зависит не только от текущего состояния входов, но и от предыстории сигналов на входах.

Возьмем обыкновенную кнопку, она не обладает памятью. Рассмотрим выключатель. Вы нажимаете на выключатель, и свет загорается. Чтобы выключить свет, вы должны перевести выключатель в выключенное состояние. Ключи такого типа называются бистабильными Каждый такой ключ ведет себя как 1-битная ячейка памяти.

В микросхемах оперативной памяти каждая бистабильная ячейка формируется с помощью двух перекрестно включенных транзисторов. Рассмотрим два логических элемента ИЛИ-НЕ, объединенных перекрестными обратными связями (см. рисунок 9.3).

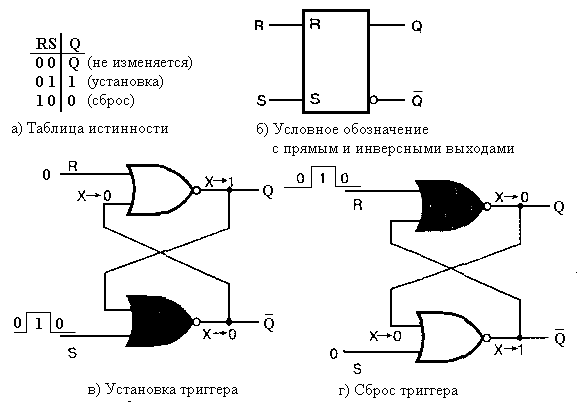

Рисунок 9.3 - RS триггер

Вспомним, что при появлении логической 1 на каком-либо входе элемента ИЛИ-НЕ на его выходе появляется логический нуль. Вооружившись этим знанием, проанализируем схему:

- если на вход S подать 1, то выход Q переключится в 0. На обоих входах верхнего элемента появится 0, что приведет к появлению 1 на выходе Q. Если, теперь на входе S снова появится 0, то нижний элемент останется в 0 (поскольку на входе обратной связи с вывода Q присутствует 1) и состояние выхода верхнего элемента также не изменится. Таким образом, триггер устанавливается при подаче положительного импульса на вход S.

- если на вход R подать 1, то выход Q переключится в 0. На обоих входах нижнего элемента появится 0, что приведет к появлению 1 на выходе Q. Если теперь на входе R снова появится 0, то верхний элемент останется в 0 (поскольку на входе обратной связи с вывода Q присутствует 1) и состояние выхода нижнего элемента также не изменится. Таким образом, триггер сбрасывается при подаче положительного импульса на вход R.

При нормальном функционировании (предполагается, что оба входа не могут быть активными в один и тот же момент времени) оба выхода дополняют друг друга, что отражено на условном графическом изображении триггера (см. рисунок 9.3).