- •Программирование цифровой техники и микроконтроллеров управления

- •Алматы 2012

- •1 Микроконтроллеры в современном мире

- •1.1 Краткая история развития микроконтроллеров

- •1.2 Задачи и роль микроконтроллеров

- •2 Выполнение арифметических операций в мп

- •2.1 Системы счислений

- •2.2 Двоичная арифметика

- •2.3 Дополнительный код

- •2.4 Знаковый разряд

- •3 Регистры общего и специального назначения

- •3.1 Регистры portc и trisc

- •3.2 Регистр Status

- •3.3 Фиксированная (абсолютная) адресация

- •4 Косвенная адресация. Логика

- •4.1 Косвенная адресация

- •4.2 Логические функции

- •5 Маскирование. Стек

- •5.1 Маскирование

- •5.2 Счетчик команд

- •5.3 Стек

- •6 Конвейер и подпрограмма задержки

- •6.1 Конвейер

- •6.2 Программа задержки

- •6.3 Расчет времени задержки

- •7 Выполнение умножения и деления

- •7.1 Умножение и деление при помощи сдвига

- •7.2 Инструкции условных переходов

- •7.3 Целочисленное умножение

- •7.4 Целочисленное деление

- •7.5 Умножение на дробное число

- •8 Программирование клавиатуры. Дешифратор

- •8.1 Клавиатура

- •8.2 Фрагменты программы

- •8.3 Дешифратор

- •8.4 Компаратор

- •9 Основные элементы цифровой техники

- •9.1 Сумматор

- •9.2 Арифметико-логическое устройство

- •9.3 Бистабильные схемы

- •9.4 Триггеры и регистры

- •10 Структура микроконтроллера. Индикатор

- •10.1 Применение операций сдвига

- •10.2 Цифровой индикатор

- •10.2 Структурная схема мк

- •11 Прерывания и сторожевой таймер

- •11.1 Прерывания

- •11.2 Подсчет посетителей с помощью прерываний

- •11.3 Сторожевой таймер

- •12 Фактор времени и аналоговый мир

- •12.1 Модуль таймера tmr1

- •12.2 Применение таймера tmr1

- •12.3 Аналоговый мир

- •Приложение а Список некоторых сокращений

- •Список литературы

- •Содержание

- •050013, Алматы, Байтурсынова, 126

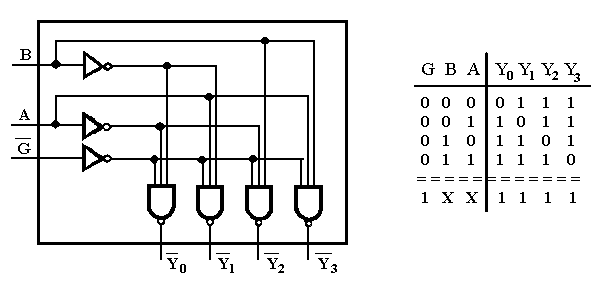

8.3 Дешифратор

Изображенная на рисунке 8.2 микросхема, содержащая определенным образом соединенные элементы И-НЕ, является типичным примером интегральных микросхем средней степени интеграции. Если вспомнить, что на выходе элемента И-НЕ логический 0 присутствует только в том случае, если на всех его входах присутствует логическая 1, то можно увидеть, что при любых сочетаниях сигналов на входах выборки BA сигнал логический 0 будет присутствовать на выходе только одного вентиля. Так, выход Y1 будет активным (активным здесь считается значение 0) при ВА=012. После рассмотрения таблицы истинности становится понятно, что данная схема декодирует двоичное число ВА таким образом, что при подаче числа N становится активным только выход Yn. Вход разрешения G подключен параллельно ко всем элементам. Таким образом, дешифратор выполняет свои функции только в том случае, если на входе G присутствует низкий уровень (логический 0). Если на входе G присутствует высокий уровень, то независимо от состояния входов В и А (в таблице истинности эта ситуация обозначается символом «X» — безразличное состояние) все выходы устанавливаются в неактивное состояние (логический 0).

Рисунок 8.2 – Схема дешифратора и таблица истинности

8.4 Компаратор

Матрица логических элементов. используемая для обнаружения равенства между двумя 8-ми битными числами Р и Q, показана на рисунке 8.3.

Рисунок 8.3. - Микросхема 8-битного компаратора

Каждый из восьми логических элементов Исключающее ИЛИ-НЕ формирует логический 1, если оба входных бита РN и QN одинаковы. Соответственно, низкий уровень на выходе элемента И-НЕ появится только в том случае, если все 8 пар битов одинаковы. Микросхема компаратора обычно имеет также вход G, сигнал с которого подается на один из входов элемента И-НЕ и выполняет функцию глобального разрешения.

На условном обозначении микросхемы по стандарту ANSI/IEC, функция сравнения указывается аббревиатурой СОМР.

9 Основные элементы цифровой техники

Цель лекции: изучить основные схемы цифровой техники.

Краткое содержание лекции. Сумматор. Арифметико-логическое устройство. Бистабильные схемы. Триггеры и регистры. D-триггер. Т-триггер.

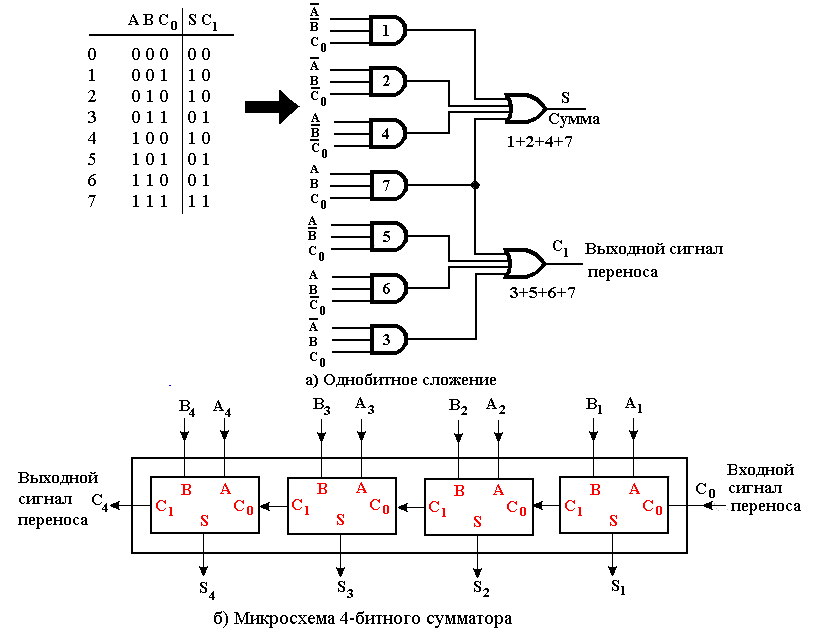

9.1 Сумматор

Одной из первых функций, реализованных в ИС помимо обычных логических функций, было сложение. В таблице истинности, показанной на рисунке 9.1, приведены значения бита суммы S и флага переноса С, образующихся при сложении двух битов А и В и бита переноса из предыдущего разряда Со.

Рисунок 9.1 – Сложение чисел

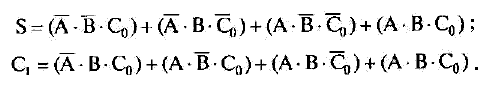

Например, из 7-й строки таблицы истинности следует, что при сложении двух единиц и 0-го переноса сумма будет равна 1, перенос равен 1 (1+1+1=11). Для реализации этой строки таблицы нам нужно распознать комбинацию битов 111, описываемую выражением АВСо. Эту операцию выполняет 7-й элемент схемы. Таким образом, для сумматора мы просто объединяем по ИЛИ все возможные комбинации входных переменных:

Применяя такую схему для каждого разряда и подключая при этом выход переноса разряда с номером К - 1 к входу переноса разряда с номером К, мы сможем выполнять сложение любых N-битных чисел.

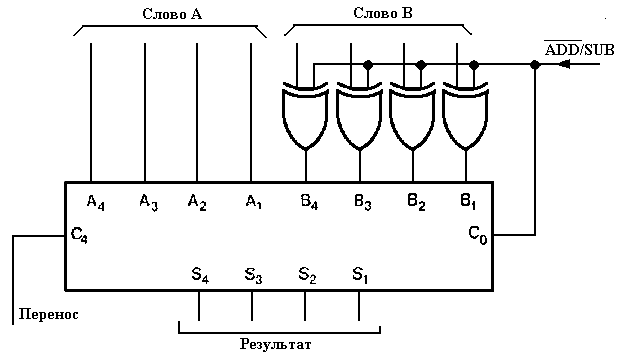

Разумеется, сумматоры можно использовать и для вычитания, если перевести операнды в дополнительный код.

Рисунок 9.2 - Программируемый сумматор/вычитатель

Схему сумматора/вычитателя можно реализовать при помощи набора логических элементов Исключающее-ИЛИ, выступающих в роли программируемых инверторов. Вход выбора режима ADD/SUB, управляющий этими инверторами на рисунке 9.2, подключен также к входу переноса, что вызывает добавление единицы в режиме вычитания.