- •Микропроцессоры в системах автоматического управления.

- •Структура микропроцессора i8080. Принцип работы.

- •Основные понятия системы прерываний. Обработка запросов прерываний i8080.

- •Архитектура микроконтроллера мк-51. Алу, организация памяти и устройства управления. Совмещение адресного пространства памяти данных и программ.

- •5. Архитектура микроконтроллера мк-51. Порты ввода/вывода.

- •6. Архитектура микроконтроллера мк-51. Таймер/счётчик.

- •7. Архитектура микроконтроллера мк-51.Последовательный интерфейс.

- •Система команд

- •4.4.1 Общая характеристика

- •4.4.2 Типы команд

- •4.4.3 Типы операндов

- •4.4.4 Группы команд

- •4.4.5 Oбозначения, используемые при описании команд

- •Система прерываний мк-51.??

- •8. Архитектура микроконтроллера мк-51. Система прерываний.??

- •9. Режимы работы мк-51.

- •Система команд мк-51. Способы адресации в мк-51.

- •Система команд мк-51. Команды передачи данных.

- •Система команд мк-51. Команды арифметических операций.

- •13. Команды логических операций микроконтроллера 8051

- •Система команд мк-51. Команды операций с битами.

- •Система команд мк-51. Команды передачи управления.

- •Программирование на языке Ассемблера. Директивы резервирования памяти.

- •Программирование на языке Ассемблера. Использование подпрограмм – процедур и подпрограмм – функций.

- •5.7.1 Реализация подпрограмм-процедур на языке asm51.

- •5.7.2 Передача переменных-параметров в подпрограмму.

- •5.7.3 Реализация подпрограмм-функций на языке asm51.

- •Организация циклов и ветвлений. Ветвление

- •Программирование на языке Ассемблера. Использование сегментов в языке программирования ассемблер. Разбиение памяти мк на сегменты, абсолютные сегменты памяти, перемещаемые сегменты памяти.

- •5.10.1 Абсолютные сегменты памяти.

- •5.10.2 Перемещаемые сегменты памяти.

- •Архитектура микроконтроллеров семейства mcs-51 gb. Адресация регистров и памяти микроконтроллеров.

- •2.4 Организация памяти.

- •2.4.2 Память данных (озу).

- •2.4.3 Регистры специальных функций.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Последовательный порт с шиной i2c.

- •2.7.3 Режимы работы таймеров-счетчиков.

- •Периферийные устройства микроконтроллеров семейства mcs-51. Программируемая счётная матрица (pca).

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Контроллер прерываний (ic).

- •2.10.1 Регистр масок прерывания (ie).

- •2.10.2 Регистр приоритетов прерываний (ip).

- •2.10.3 Выполнение подпрограммы прерывания.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Аналого-цифровой преобразователь (adc). Функциональная схема ацп

- •Числа в двоичном, восьмеричном, шестнадцатеричном и двоично-десятичном коде.

- •Перевод двоичных чисел в восьмеричный и шестнадцатеричный формат и наоборот.

- •Системы счисления. Перевод десятичных чисел в систему с основанием r.

- •Перевод чисел с основанием r в десятичные числа

- •Двоичная арифметика (сложение, умножение, деление двоичных чисел).

- •Вычитание двоичных чисел

- •Логические операции над двоичными числами.

9. Режимы работы мк-51.

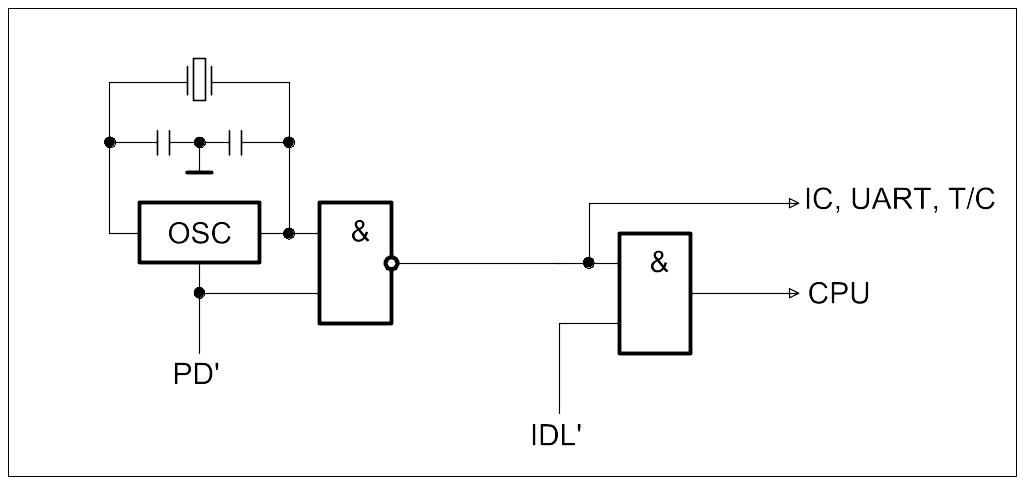

МК 80C51 имеют два энергосберегающих режима работы: режим холостого хода (idle mode) и режим пониженного энергопотребления (power down mode). В режиме холостого хода (IDL=1) внутренний тактовый генератор МК работает, осуществляя синхронизацию контроллера прерываний, последовательного порта и таймеров, но блокируется поступление импульсов синхронизации в центральный процессор (рис. 2.17). В режиме пониженного энергопотребления (PD=1) тактовый генератор останавливается и импульсы синхронизации не вырабатываются.

В режим холостого хода МК переводится программной установкой бита IDL (PCON.0) регистра управления мощностью.

В этом режиме приостанавливается работа CPU, благодаря чему снижается энергопотребление МК приблизительно в 4 раза. Кроме того, дополнительно снижается энергопотребление всей микропроцессорной системы за счет резкого уменьшения тока потребления микросхем внешней памяти.

Р ис.

2.17. Внутренняя синхронизация МК в режимах

Idle и Power

Down

ис.

2.17. Внутренняя синхронизация МК в режимах

Idle и Power

Down

Тактовый генератор МК, а также таймеры, последовательный порт и контроллер прерываний в режиме холостого хода продолжают работать. Содержимое внутренней памяти данных и всех регистров специальных функций (в том числе, SP, PC, PSW, ACC), а также логические сигналы на выходах всех портов сохраняются неизменными. На выходах ALE и PSEN’ поддерживаются логические сигналы 1.

Вывести МК из режима холостого хода можно с помощью любого разрешенного прерывания или с помощью аппаратного сброса.

При формировании запроса прерывания бит IDL аппаратно сбрасывается контроллером прерываний, процессор возобновляет работу, а управление передается подпрограмме обслуживания прерывания. Возврат из подпрограммы обслуживания прерывания осуществляется к той команде программы, которая следует за командой, переключившей МК в режим холостого хода.

Для того, чтобы выйти из режима холостого хода с помощью аппаратного сброса МК, достаточно подать внешний сигнал RST на время, равное длительности двух машинных циклов, поскольку в этом случае (в отличие от сброса при включении электропитания) тактовый генератор не нуждается в запуске. Бит IDL сбрасывается сигналом RST асинхронно, и CPU сразу же возобновляет выполнение программы с того места, где она была приостановлена переходом в режим холостого хода. Следует помнить о том, что внутренний сигнал сброса формируется не мгновенно, а с некоторой задержкой относительно переднего фронта сигнала RST (около двух машинных циклов), причем, до тех пор, пока не произошел сброс МК, аппаратно запрещается доступ процессора к внутренней памяти данных, но не запрещается доступ к буферным регистрам параллельных портов. Для того, чтобы исключить появление неожиданных сигналов на выходах портов, не следует использовать в программе сразу вслед за командой, которая переводит МК в режим холостого хода, команду записи в регистр параллельного порта или команду обращения к внешней памяти данных.

Перевод МК в режим пониженного энергопотребления осуществляется программной установкой бита PD (PCON.1) регистра управления мощностью. В этом режиме тактовый генератор МК не работает, вследствие чего синхронизация всех внутренних функциональных узлов прекращается. Содержимое внутренней памяти данных и регистров специальных функций сохраняется неизменным, выходные сигналы портов соответствуют содержимому буферных регистров, на выходах ALE и PSEN’ формируются сигналы 0. Потребляемый ток снижается приблизительно до 15 мкА.

Выход из режима пониженного энергопотребления возможен только путем аппаратного сброса МК. При этом происходит начальная установка всех регистров специальных функций, но сохраняется неизменным содержимое внутренней памяти данных. Длительность сигнала RST должна быть достаточной для запуска тактового генератора МК.

После перевода МК в режим пониженного энергопотребления напряжение питания может быть снижено до 2 В, однако, перед выходом из данного режима напряжение питания должно быть восстановлено до нормального уровня.