- •Микропроцессоры в системах автоматического управления.

- •Структура микропроцессора i8080. Принцип работы.

- •Основные понятия системы прерываний. Обработка запросов прерываний i8080.

- •Архитектура микроконтроллера мк-51. Алу, организация памяти и устройства управления. Совмещение адресного пространства памяти данных и программ.

- •5. Архитектура микроконтроллера мк-51. Порты ввода/вывода.

- •6. Архитектура микроконтроллера мк-51. Таймер/счётчик.

- •7. Архитектура микроконтроллера мк-51.Последовательный интерфейс.

- •Система команд

- •4.4.1 Общая характеристика

- •4.4.2 Типы команд

- •4.4.3 Типы операндов

- •4.4.4 Группы команд

- •4.4.5 Oбозначения, используемые при описании команд

- •Система прерываний мк-51.??

- •8. Архитектура микроконтроллера мк-51. Система прерываний.??

- •9. Режимы работы мк-51.

- •Система команд мк-51. Способы адресации в мк-51.

- •Система команд мк-51. Команды передачи данных.

- •Система команд мк-51. Команды арифметических операций.

- •13. Команды логических операций микроконтроллера 8051

- •Система команд мк-51. Команды операций с битами.

- •Система команд мк-51. Команды передачи управления.

- •Программирование на языке Ассемблера. Директивы резервирования памяти.

- •Программирование на языке Ассемблера. Использование подпрограмм – процедур и подпрограмм – функций.

- •5.7.1 Реализация подпрограмм-процедур на языке asm51.

- •5.7.2 Передача переменных-параметров в подпрограмму.

- •5.7.3 Реализация подпрограмм-функций на языке asm51.

- •Организация циклов и ветвлений. Ветвление

- •Программирование на языке Ассемблера. Использование сегментов в языке программирования ассемблер. Разбиение памяти мк на сегменты, абсолютные сегменты памяти, перемещаемые сегменты памяти.

- •5.10.1 Абсолютные сегменты памяти.

- •5.10.2 Перемещаемые сегменты памяти.

- •Архитектура микроконтроллеров семейства mcs-51 gb. Адресация регистров и памяти микроконтроллеров.

- •2.4 Организация памяти.

- •2.4.2 Память данных (озу).

- •2.4.3 Регистры специальных функций.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Последовательный порт с шиной i2c.

- •2.7.3 Режимы работы таймеров-счетчиков.

- •Периферийные устройства микроконтроллеров семейства mcs-51. Программируемая счётная матрица (pca).

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Контроллер прерываний (ic).

- •2.10.1 Регистр масок прерывания (ie).

- •2.10.2 Регистр приоритетов прерываний (ip).

- •2.10.3 Выполнение подпрограммы прерывания.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Аналого-цифровой преобразователь (adc). Функциональная схема ацп

- •Числа в двоичном, восьмеричном, шестнадцатеричном и двоично-десятичном коде.

- •Перевод двоичных чисел в восьмеричный и шестнадцатеричный формат и наоборот.

- •Системы счисления. Перевод десятичных чисел в систему с основанием r.

- •Перевод чисел с основанием r в десятичные числа

- •Двоичная арифметика (сложение, умножение, деление двоичных чисел).

- •Вычитание двоичных чисел

- •Логические операции над двоичными числами.

5. Архитектура микроконтроллера мк-51. Порты ввода/вывода.

Параллельные порты предназначены для ввода/вывода цифровых данных в параллельном коде. Микроконтроллеры подсемейства 80C51 имеют 4 параллельных порта.

Все четыре порта являются двунаправленными. Отдельные разряды портов может быть использован независимо для ввода и вывода информации.

Каждый порт состоит из регистра-защелки (регистры P0 P3), выходного драйвера (управляющего каскада) и входного буфера. Для того, чтобы какая-либо линия порта могла быть использована для ввода данных, в соответствующий разряд регистра-защелки этого порта должна быть записана 1.

Порты Р0 и Р2 используются микроконтроллером при обращении к внешней памяти. Порт Р0 служит для вывода младшего байта адреса, а также для ввода/вывода байта данных в режиме временного мультиплексирования. Порт Р2 служит для вывода старшего байта адреса, если длина адреса равна 16 бит (при выполнении команды MOVX A,@DPTR). В том случае, когда при обращении к внешней памяти данных формируется 8-битный адрес (при выполнении команды MOVX A,@Ri), порт Р2 используется по своему прямому назначению – через него выводится содержимое регистра-защелки Р2.

Порт Р3 является многофункциональным. Каждый разряд этого порта выполняет какую-либо альтернативную функцию. Разрешение альтернативных функций осуществляется путем записи 1 в соответствующие разряды регистра-защелки порта.

По сигналу RST в регистры-защелки всех портов записывается число FFH, разрешая тем самым все альтернативные функции и устанавливая для всех портов режим ввода данных.

6. Архитектура микроконтроллера мк-51. Таймер/счётчик.

В режиме таймера (т.е. счетчика времени) содержимое счетчика инкрементируется в каждом машинном цикле. В режиме счета внешних событий содержимое счетчика инкрементируется под воздействием перехода из 1 в 0 внешнего логического сигнала, поступающего на соответствующий вход микроконтроллера.

При работе таймера/счетчика в режиме счетчика внешних событий максимальная частота входных импульсов не должна превышать 1/24 тактовой частоты микроконтроллера, поскольку для распознавания перехода внешнего сигнала из 1 в 0 требуется два машинных цикла. Для того, чтобы обеспечить надежное считывание значения внешнего входного сигнала, сигнал не должен изменяться в течение одного полного машинного цикла. Длительность периода входного сигнала сверху не ограничена.

Для управления работой таймеров/счетчиков и организации взаимодействия таймеров/счетчиков с системой прерываний используются два регистра специальных функций – регистр управления режимом TMOD (Timer/Counter Mode Control Register) и регистр управления TCON (Timer/Counter Control Register).

Выбор функционального назначения таймера/счетчика (“таймер” или “счетчик внешних событий”) осуществляется программированием бита C/T’ регистра TMOD.

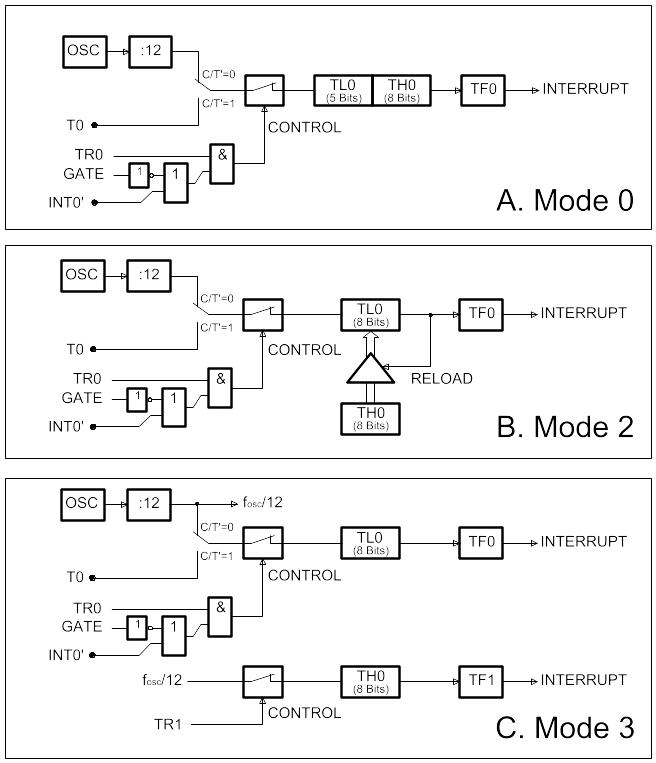

Каждый таймер/счетчик (в дальнейшем таймер) имеет четыре режима работы, индивидуально программируемых с помощью битов M0 и M1 регистра TMOD. Выбранный режим определяет не только алгоритм работы таймера, но также и его внутреннюю структуру (рис. 2.11). Режимы 0, 1 и 2 одинаковы для обоих таймеров. В режиме 3 таймеры работают по-разному. Ниже рассмотрены все режимы работы таймеров на примере таймера 0.

В режиме 0 таймер 0 представляет собой программно управляемый 13-разрядный двоичный счетчик импульсов, состоящий из 8-разрядного счетчика TH0, вход которого подключен к выходу 5-разрядного делителя частоты TL0 (рис. 2.11, А). При переполнении счетчика (когда счетчик переходит из состояния “все единицы” в состояние “все нули”) таймер устанавливает флаг TF0.

Р ис.

2.11. Таймер-счетчик 0 в разных режимах

работы:

ис.

2.11. Таймер-счетчик 0 в разных режимах

работы:

А. Режим 0: 13-разрядный счетчик,

В. Режим 2: 8-разрядный счетчик с автоперезагрузкой,

С: Режим 3: два 8-разрядных счетчика

Счетные импульсы поступают на вход счетчика TL0, когда TR0=1 и либо GATE=0, либо INT0’=1, где TR0 – управляющий бит регистра TCON, GATE – бит 3 регистра TMOD, а INT0’ – внешний сигнал запроса прерывания.

Режим 1 отличается от режима 0 (см. рис. 2.11, А) только тем, что счетчик TL0 имеет разрядность 8 бит, а весь таймер, в структуру которого входят два последовательно включенных счетчика TL0 и TH0, имеет разрядность 16 бит.

В режиме 2 таймер 0 представляет собой 8-разрядный счетчик с автоперезагрузкой (см. рис. 2.11, В). При переполнении счетчика TL0 не только устанавливается флаг TF0, но и автоматически загружается в TL0 содержимое счетчика TH0. После перезагрузки содержимое счетчика TH0 остается прежним. Начальная установка счетчика TH0 выполняется программным путем.

В режиме 3 таймеры 0 и 1 работают по-разному.

Содержимое таймера 1 в режиме 3 сохраняется неизменным (эффект такой же, как при TR1=0).

Счетчики TL0 и TH0 таймера 0 работают как два независимых 8-разрядных счетчика (см. рис. 2.11, С). Счетчик TL0 использует управляющие биты таймера 0: C/T’, GATE, TR0, INT0’ и TF0. Счетчик TH0, который может выполнять только функции таймера (считать машинные циклы), использует управляющий бит TR1 и флаг TF1 таймера 1.

Режим 3 используется тогда, когда для реализации требуемого алгоритма нужен дополнительный 8-разрядный таймер или счетчик. Если таймер 0 работает в режиме 3, в составе МК 80С51 имеется три таймера. При этом таймер 1 может быть выключен путем перевода в свой собственный режим 3, может быть использован последовательным портом в качестве формирователя частоты синхронизации, а также может быть использован в любом применении, не требующем прерывания.