- •Микропроцессоры в системах автоматического управления.

- •Структура микропроцессора i8080. Принцип работы.

- •Основные понятия системы прерываний. Обработка запросов прерываний i8080.

- •Архитектура микроконтроллера мк-51. Алу, организация памяти и устройства управления. Совмещение адресного пространства памяти данных и программ.

- •5. Архитектура микроконтроллера мк-51. Порты ввода/вывода.

- •6. Архитектура микроконтроллера мк-51. Таймер/счётчик.

- •7. Архитектура микроконтроллера мк-51.Последовательный интерфейс.

- •Система команд

- •4.4.1 Общая характеристика

- •4.4.2 Типы команд

- •4.4.3 Типы операндов

- •4.4.4 Группы команд

- •4.4.5 Oбозначения, используемые при описании команд

- •Система прерываний мк-51.??

- •8. Архитектура микроконтроллера мк-51. Система прерываний.??

- •9. Режимы работы мк-51.

- •Система команд мк-51. Способы адресации в мк-51.

- •Система команд мк-51. Команды передачи данных.

- •Система команд мк-51. Команды арифметических операций.

- •13. Команды логических операций микроконтроллера 8051

- •Система команд мк-51. Команды операций с битами.

- •Система команд мк-51. Команды передачи управления.

- •Программирование на языке Ассемблера. Директивы резервирования памяти.

- •Программирование на языке Ассемблера. Использование подпрограмм – процедур и подпрограмм – функций.

- •5.7.1 Реализация подпрограмм-процедур на языке asm51.

- •5.7.2 Передача переменных-параметров в подпрограмму.

- •5.7.3 Реализация подпрограмм-функций на языке asm51.

- •Организация циклов и ветвлений. Ветвление

- •Программирование на языке Ассемблера. Использование сегментов в языке программирования ассемблер. Разбиение памяти мк на сегменты, абсолютные сегменты памяти, перемещаемые сегменты памяти.

- •5.10.1 Абсолютные сегменты памяти.

- •5.10.2 Перемещаемые сегменты памяти.

- •Архитектура микроконтроллеров семейства mcs-51 gb. Адресация регистров и памяти микроконтроллеров.

- •2.4 Организация памяти.

- •2.4.2 Память данных (озу).

- •2.4.3 Регистры специальных функций.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Последовательный порт с шиной i2c.

- •2.7.3 Режимы работы таймеров-счетчиков.

- •Периферийные устройства микроконтроллеров семейства mcs-51. Программируемая счётная матрица (pca).

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Контроллер прерываний (ic).

- •2.10.1 Регистр масок прерывания (ie).

- •2.10.2 Регистр приоритетов прерываний (ip).

- •2.10.3 Выполнение подпрограммы прерывания.

- •Периферийные устройства микроконтроллеров семейства mcs-51 gb. Аналого-цифровой преобразователь (adc). Функциональная схема ацп

- •Числа в двоичном, восьмеричном, шестнадцатеричном и двоично-десятичном коде.

- •Перевод двоичных чисел в восьмеричный и шестнадцатеричный формат и наоборот.

- •Системы счисления. Перевод десятичных чисел в систему с основанием r.

- •Перевод чисел с основанием r в десятичные числа

- •Двоичная арифметика (сложение, умножение, деление двоичных чисел).

- •Вычитание двоичных чисел

- •Логические операции над двоичными числами.

2.7.3 Режимы работы таймеров-счетчиков.

Рассмотрим кратко работу Т/С в каждом из режимов.

Рис.5. Логика работы T/C0 и Т/C1в режимах 0, 1, 2 и 3

Режим 0. Перевод любого Т/С в режим 0 делает его похожим на таймер КМ1816ВЕ48 (восьми битный счетчик), к входу которого подключен пяти-битный предделитель частоты на 32. Работу Т/С в режиме 0 на примере T/C1 иллюстрирует рис а. В этом режиме таймерный регистр имеет разрядность 13 бит. При переходе из состояния "все единицы" в состояние "все нули" устанавливается флаг прерывания от таймера TF 1. Входной синхросигнал таймера 1 разрешен (поступает на вход Т/С1), когда управляющий бит TR1 установлен в 1 либо управляющий бит GATE (блокировка) равен 0, либо на внешний вывод запроса прерывания INT1 поступает уровень 1. Отметим попутно, что установка бита GATE в 1 позволяет использовать таймер для измерения длительности импульсного сигнала подаваемого на вход запроса прерывания.

Режим 1. Работа любого Т/С в этом режиме такая же, как и в режиме 0, за исключением того, что таймерный регистр имеет разрядность 16 бит.

Режим 2. В этом режиме работа организована таким образом, что переполнение (переход из состояния "все единицы" в состояние, "все нули") восьмибитного счетчика TL1 приводит не только к установке флага TF1 (см. рис. б), но и автоматически перезагружает в TL1 содержимое старшего байта (TH 1) таймерного регистра, которое предварительно было задано программным путем. Перегрузка оставляет содержимое TH1 неизменным. В режиме 2 Т/С0 и Т/С1 также работают совершенно одинаково.

Режим 3. В режиме 3 Т/С0 и Т/С1 работают по-разному. Т/С1 сохраняет неизменным свое текущее содержимое. Иными словами, эффект такое же как и при сбросе управляющего бита TR1 в 0. Работу Т/С0 иллюстрирует рис. в. В режиме 3 TL0 и TH0 функционируют как два независимых восьмибитных счетчика. Работу TL0 определяют управляющие биты Т/С0 (С/Т, GATE TR0), входной сигнал INT0 и флаг переполнения TF0. Работу TH0, который может выполнять только функции таймера (подсчёт машинных циклов микро-ЭВМ), определяет управляющий бит TR1. При этом TH0 использует флаг переполнения TF1. Режим 3 используется в тех случаях, когда требуется наличие дополнительного восьми битного таймера или счетчика событий. Можно считать, что в этом режиме микро-ЭВМ 8051 имеет в своем составе три таймера/счетчика. В случае же, если Т/С0 используется в режиме 3, Т/С1 может быть или выключен, или переведен в режим 0, 1 или 2, или может быть использован последовательным портом в качестве генератора частоты передачи.

Периферийные устройства микроконтроллеров семейства mcs-51. Программируемая счётная матрица (pca).

Данная многофункциональная структура предназначена для выполнения целого спектра операций с применением таймеров/счётчиков и позволяет увеличить производительность CPU за счёт минимизации числа обращений к нему. По этому же удается уменьшить объём и сложность необходимого программного обеспечения.

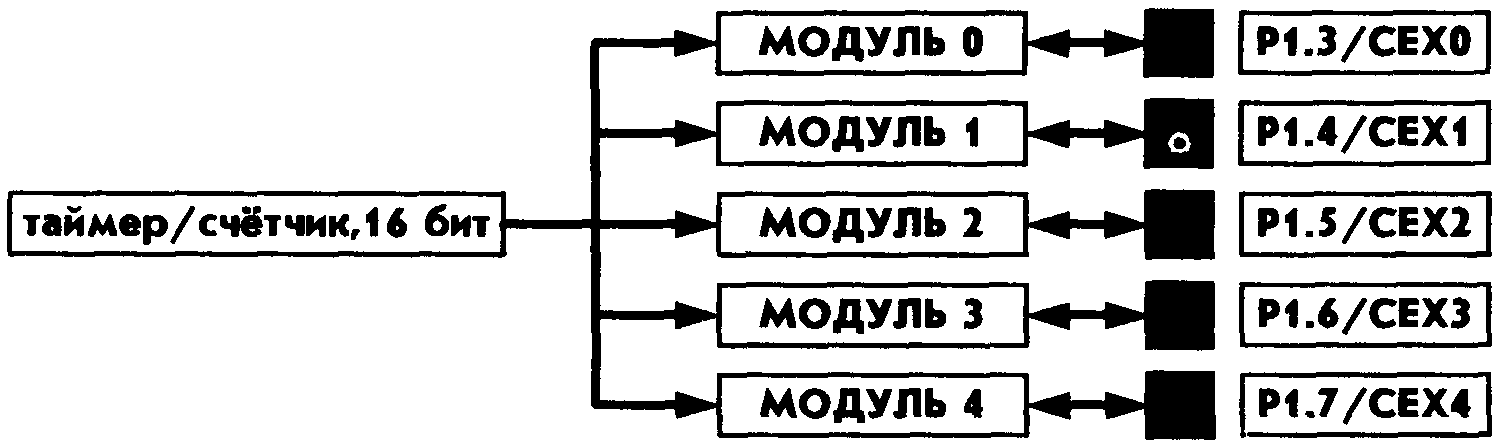

Матрица программируемых счётчиков

РСА состоит из 1-го таймера/счётчика и 5-ти 16-битных модулей фиксации/сравнения, изображённых на Таймер/счётчик является общим для всех модулей, а также единственным, который может ими использоваться. Входной сигнал может подаваться на него с одного от следующих источников:

• Fclc/12;

• Fclc/4;

• Сигнал переполнения Т/СО;

• * Внешний вывод ECI (Р1.2).

Каждый модуль фиксации/сравнения может быть запрограммирован на один из следующих режимов:

• фиксация увеличения и/или уменьшения кромки;

• программный таймер;

• высокоскоростной выход;

• сторожевой таймер (только для модуля 4);

• широтно-импульсный модулятор.

Когда модуль сравнения/фиксации запрограммирован на режим фиксации, программного таймера или высокоскоростного выхода, возможна генерация соответствующего ему прерывания. Все 5 модулей и таймер/счётчик разделяют один и тот же вектор – 0033h, описанный несколько ниже. Для ввода/вывода таймер/счётчик и модули сравнения/фиксации используют выводы порта 1, как показано в таблице. Если соответствующий модуль не задействован, то вывод порта используется по своему прямому назначению.

Использование порта 1 для РСА

-

компонент РСА

вывод порта 1

16-битный счётчик

Р1.2/ЕС1

16-битный модуль 0

Р1.3/СЕХО

16-битный модуль 0

Р1.4/СЕХ1

16-битный модуль 0

Р1.5/СЕХ2

16-битный модуль 0

Р1.6/СЕХЗ

16-битный модуль 0

Р1.7/СЕХ4

16-разрядный таймер/счётчик РСА (рис. 6.3) состоит из регистров СН и CL (соответственно старший и младший байты счётчика). Эти 2 регистра постоянно доступны для чтения и записи.

Ниже рассмотрены некоторые примеры режимов:

Режим сторожевого таймера

Сторожевой таймер предназначен для автоматического сброса системы в случае, если она не производит регулярных обращений к нему с целью изменения его значения. Эта функция применяется в программах, функционирующих в условиях электрических помех, электростатических наводок и требующих повышенной надёжности работы микроконтроллера. Данный режим доступен лишь для модуля 4. В этом режиме каждый раз, когда значения таймера РСА и регистра хранения/фиксации модуля 4 достигают равенства, генерируется сигнал внутреннего сброса процессора.

Широтно-импульсный модулятор - PWM

Любой модуль РСА из 5-ти имеющихся может быть запрограммирован как "широтно-импульсный модулятор". Этот режим может использоваться для преобразования дискретного выходного значения в аналоговый сигнал посредством какого-либо внешнего преобразователя (например, интегрирующей цепи). Частота выходного сигнала зависит от частоты тактирования таймера/счётчика РСА, т.е., для тактовой частоты 16КГц, максимально возможная выходная частота составит 15.6 Кгц.

PCA1

Описываемая микросхема, содержит и второй набор РСА, аналогичный первому, названный РСА1. Отличия РСА1 от РСА заключаются в следующем:

• модуль 4 РСА1 не поддерживает сторожевой таймер;

• внешними выводами РСА1 являются ножки Р4.2-Р4.7 (все альтернативные функции портов микросхемы перечислены при описании её выводов);

• названия всех регистров РСА1 и их битов содержат символ "1" в своём имени см. табл.

• В регистре управления РСА1 СICON, в 5-й позиции имеется дополнительный бит CRE (битовый адрес 0EDh). При установке данного бита в "1", разрешение работы РСА1 происходит посредством совместной установки битов CR и CR 1.