- •Основи електроніки та мікропроцесорної техніки

- •Основні дати відкриттів і винаходів в електроніці

- •Як вивчати електроніку

- •Розділ 1. Фізичні основи електронної теорії

- •1.1 Основи електронної теорії

- •1.1.1 Електрон та його властивості

- •1.1.2 Робота виходу електронів. Електронна емісія

- •Таким чином, для відриву від поверхні провідника електрони повинні затратити роботу проелектричних сил, які повертають їх назад:

- •1.1.3 Рух електронів в електричних та магнітних полях

- •1.1.4 Електричний струм в газі

- •Контрольні питання і вправи

- •1.2. Електрофізичні властивості напівпровідників

- •1.2.1 Фізичні властивості напівпровідників

- •1.2.2 Власна провідність напівпровідників

- •1.2.3 Домішкова провідність

- •Дрейфовий і дифузний струми в напівпровіднику

- •1.2.4 Електронно-дірковий перехід

- •1.2.5 Властивості р-n переходу

- •Контрольні питання і вправи

- •2. Електронні прилади

- •2.1. Пасивні елементи електроніки

- •2.1.1. Резистори

- •2.1.2 Конденсатори

- •2.1.3 Котушки індуктивності. Трансформатори

- •2.1.4 Коливальні контури

- •2.1.5 Напівпровідникові резистори

- •Терморезистори

- •Фоторезистори

- •Варистори

- •Контрольні питання і вправи

- •2.2 Напівпровідникові діоди

- •2.2.1 Випрямні діоди

- •2.2.2. Високочастотні та імпульсні діоди

- •2.2.3 Стабілітрони

- •2.2.4 Варикапи

- •2.2.5. Тунельні діоди

- •2.2.6 Фотодіоди

- •2.2.7 Світлодіоди

- •2.2.8 Маркування діодів

- •Контрольні питаня і вправи

- •2.3 Транзистори. Тиристори

- •2.3.1 Класифікація транзисторів

- •2.3.2 Будова та принцип роботи біполярних транзисторів

- •2.3.3 Схеми ввімкнення транзистора

- •Еквівалентна схема заміщення, h – параметри транзистора

- •Статичні характеристики транзистора та визначення за ними h - параметрів

- •Температурні і частотні властивості транзистора

- •Транзистор у режимі ключа

- •Польові транзистори

- •Одноперехідні (двобазові) транзистори

- •Фототранзистори

- •Тиристори

- •Контрольні питаня і вправи

- •2.4 Електровакуумні та іонні прилади

- •Електронні лампи

- •Електровакуумний діод

- •Маркування електровакуумних приладів

- •Іонні прилади тліючого розряду

- •Неонова лампа

- •Тиратрон

- •2.5 Гібридні інтегральні мікросхеми

- •2.5.1 Конструктивні елементи гібридних інтегральних мікросхем

- •2.5.2 Пасивні елементи

- •2.5.3 Активні елементи – безкорпусні напівпровідникові прилади

- •Контрольні питання і вправи

- •2.6 Напівпровідникові інтегральні мікросхеми

- •2.6.1 Принцип виготовлення напівпровідникових імс

- •2.6.2 Великі імс

- •Контрольні питання і вправи

- •2.7 Оптоелектронні прилади

- •2.7.1 Елементна база мікроелектроніки – світловипромінювачі, фотоприймачі

- •2.7.2 Оптрони

- •Контрольні питання та вправи

- •Прилади відображення інформації

- •2.8.1 Електронно-променеві трубки

- •2.8.2 Буквенно-цифрові індикатори

- •Контрольні питання і вправи

- •3 Основи аналогової електронної схемотехніки

- •3.1 Підсилювачі

- •3.1.1 Призначення і характеристика підсилювачів

- •3.1.2 Основні показники роботи підсилювача

- •3.1.3 Підсилювачі низької частоти. Попередні каскади підсилення

- •3.1.4 Міжкаскадні зв’язки

- •3.1.5 Підсилювачі потужності

- •3.1.6 Зворотні зв’язки у підсилювачах

- •3.1.7 Фазоінвертори

- •3.1.8 Підсилювачі постійного струму Підсилювачі постійного струму прямого підсилення

- •Балансні та диференційні підсилювачі

- •3.1.9 Операційні підсилювачі

- •Масштабні інвертуючи підсилювачі

- •Масштабні неінвертуючи підсилювачі

- •Інтегратори

- •Компаратори

- •Контрольні питання та вправи

- •3.2 Генератори синусоїдних коливань

- •3.2.1 Класифікація генераторів

- •3.2.2 Автогенератори lc-типу

- •3.2.3 Стабілізація частоти lс - генераторів

- •3.2.4. Автогенератори типу rc

- •3.2.4. Автогенератор на тунельному діоді

- •3.2.5. Генератори на інтегральних мікросхемах

- •Контрольні питання та вправи

- •3.3 Випрямлячі. Стабілізатори

- •3.3.1 Класифікація випрямлячів

- •3.3.2 Однофазні випрямлячі

- •3.3.3. Випрямлячі з помноженням напруги

- •3.3.4. Трифазні випрямлячі

- •3.3.5. Згладжуючі фільтри

- •Стабілізатори постійної напруги

- •Стабілізатори струму

- •3.3.8 Стабілізатори постійної напруги на імс

- •3.3.9 Стабілізатори змінної напруги

- •3.3.10 Інвертори струму та напруги

- •Контрольні питання та вправи

- •Розділ 4. Основи цифрової електронної схемотехніки

- •4.1 Імпульсні пристрої

- •4.1.1 Загальні характеристики сигналів

- •Основні характеристики електричних сигналів імпульсного типу

- •4.1.2. Ключі як генератори імпульсів

- •4.1.3. Мультивібратори

- •4.1.4. Блокінг-генератор

- •4.1.5. Тригер на дискретних елементах

- •Контрольні питаня і вправи

- •4.2. Логічні елементи

- •4.2.1. Основні логічні операції (функції)

- •4.2.2. Найпростіші логічні схеми

- •4.2.3. Логічні інтегральні мікросхеми (класифікація)

- •4.2.4. Характеристики і параметри логічних мікросхем

- •4.2.5. Логічні імс типу дтл, ттл, на мдн (мон) транзисторах

- •4.2.6. Коротка характеристика деяких серій логічних імс

- •Контрольні питання та вправи

- •4.3. Цифрові пристрої

- •4.3.1. Цифрові способи зображення (передавання) інформації. Системи числення

- •4.3.2 Тригери на логічних елементах

- •4 Б .3.3. Двійковий лічильник та дільник частоти

- •4.3.4. Регістри

- •4.3.5. Комбінаційні цифрові інтегральні пристрої (комбінаційні цифрові мікросхеми)

4.3.4. Регістри

Р егістр

- це послідовнісний цифровий пристрій,

призначений для приймання,

зберігання, простих перетворень і

передачі двійкових чисел.

егістр

- це послідовнісний цифровий пристрій,

призначений для приймання,

зберігання, простих перетворень і

передачі двійкових чисел.

Під простими перетвореннями розуміється зсув чисел на задану кількість розрядів, перетворення послідовного двійкового коду у паралельний і паралельного у послідовний. Базовими елементами регістрів є тригери, які доповнюються комбінаційними логічними елементами для реалізації різних зв’язків між розрядами регістра для управління прийманням і передачею операндів. Основне функціональне призначення регістрів - оперативна пам’ять для багаторозрядних двійкових чисел.

Залежно від способу приймання і передачі двійкової інформації розрізняють паралельні, послідовні, послідовно-паралельні, паралельно- послідовні й універсальні регістри.

Паралельні

регістри.

У

паралельних регістрах або регістрах

пам’яті,

ввід-вивід

всіх розрядів числа проводиться

одночасно за один такт. При побудові

паралельних

регістрів використовуються прості

асинхронні RS-тригери

і синхронні

RS-

і

D-тригери.

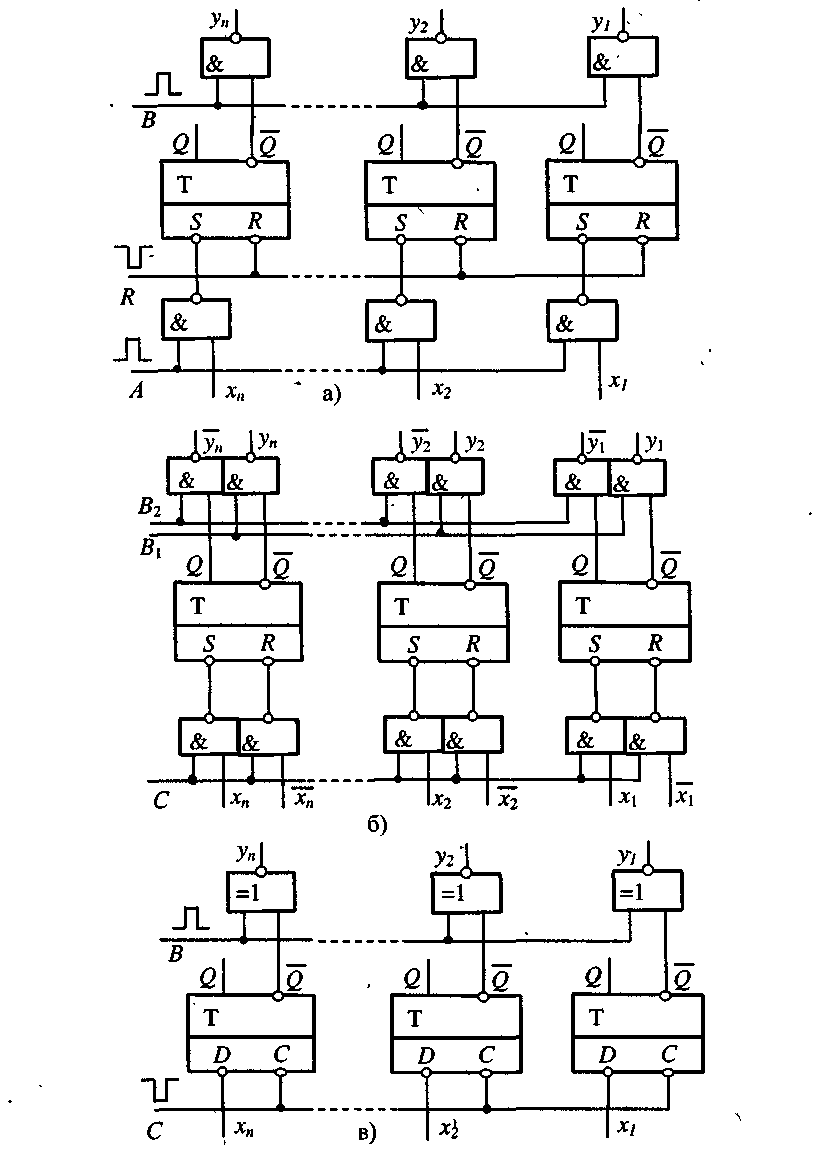

На рис. 4.30 подано варіанти паралельних

регістрів, які відрізняються

типом тригерів і складом вхідних-вихідних

інформаційних шин. У

регістра на основі асинхронних RS

-тригерів (рис. 4.30,а)

перед занесенням п-розрядного

числа з входів х1,...,

хn

необхідно

попередньо провести скидання всіх

тригерів у нульовий стан. Скидання

проводиться сигналом R=

0. Введення

інформації

в регістр проходить за сигналом А=

1,

R=

1.

Якщо

на деякому i-му

вході

Хi=

1,

то

![]() і даний тригер (з інверсним керуванням)

перемкнеться

у стан "1".

При

Хi=

0

і даний тригер (з інверсним керуванням)

перемкнеться

у стан "1".

При

Хi=

0

![]() і і-тригер збереже

стан "0". Виведення

інформації із регістра здійснюється

за сигналом В=1,

який

визначає стан

виводів

і і-тригер збереже

стан "0". Виведення

інформації із регістра здійснюється

за сигналом В=1,

який

визначає стан

виводів

![]() .

Якщо

В

=

0, то

на всіх виходах встановлюються рівні

"логічна

1",

а

при В

=

1

буде

.

Якщо

В

=

0, то

на всіх виходах встановлюються рівні

"логічна

1",

а

при В

=

1

буде

![]() .

Основний недолік даного регістра

-необхідність

попередньої його очистки, тому оновлення

інформації відбувається

за два такти.

.

Основний недолік даного регістра

-необхідність

попередньої його очистки, тому оновлення

інформації відбувається

за два такти.

Регістр (рис. 4.30, б) також побудований на асинхронних RS -тригерах і не вимагає попередньої очистки інформації, оскільки її поновлення проходить встановленням тригерів у стан "1" і "0" за один такт. Для цього на вході регістра необхідно вдвоє більше логічних елементів і ліній зв'язку. У схемі показаний спосіб видачі інформації у прямому коді (команда В= 1). Асинхронні RS -тригери в поєднанні з вхідними вентилями фактично утворюють варіанти синхронних RS -тригерів.

На рис. 4.30,в наведена схема паралельного регістра на основі синхронних D-тригерів.

Послідовні регістри. У послідовних регістрах (зсуваних) введення-виведення інформації здійснюється через один інформаційний вхід і вихід порозрядно зі зсувом числа. За один такт введена або виведена інформація зсувається на один розряд вправо або вліво. Зсувані регістри, які за командою керування реалізують зсув інформації вправо або вліво, називають реверсивними.

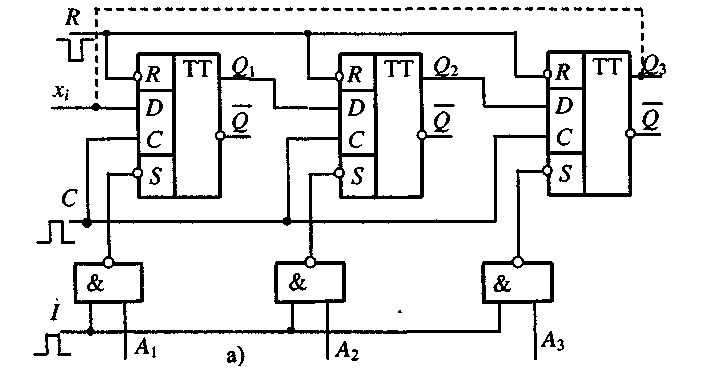

На рис. 4.31,а наведено зсувний регістр на D-тригерах, а на рис. 4.31,6 - часову діаграму зсуву інформації.

Вводити інформацію можна послідовно із входів х з наступним зсувом її вправо на рдин розряд за синхроімпульсом по входу С або паралельно із входів А за сигналом І=1 асинхронним записом числа в попередньо очищений регістр (сигнал R=0 асинхронного скидання тригерів у стан "0"). Додатний фронт синхроімпульсу С=1 забезпечує запис інформації з входів D і х в тригери першого ступеня. Вихідні рівні тригерів залишаються незмінними.

Від’ємний фронт синхроімпульсу, входи D-тригерів блокує, а рівні на виходах перемкнуться.

Рис Рис.4.31. Схема зсуваного регістра (а)

і часові діаграми зсуву інформації (б).

Рис.4.30. Схеми паралельних регістрів:

а - на асинхронних RS-тригерах; б - на асинхронних RS-тригерах без необхідності попередньої очистки інформації; в-на синхронних D-

тригерах.

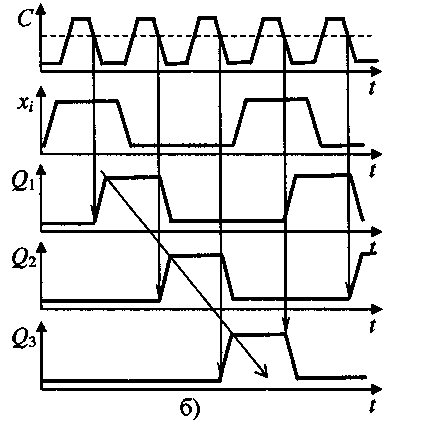

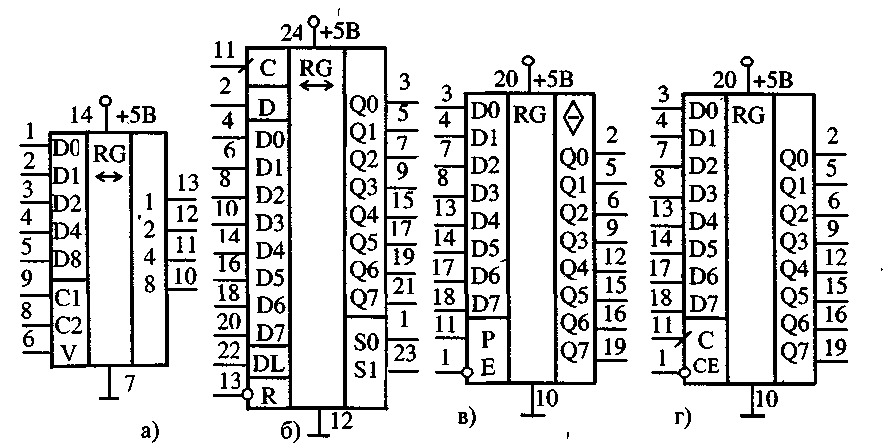

Схеми деяких типів регістрів наведено на рис. 4.32.

Регістр К155ИР1 (К133ИР1, К134ИР1, К555ИР1) (рис. 4.32,а) реалізує дві мікрооперації: приймання коду з входів D при V= 1 і зсув вправо при V= 0, які виконуються за спадом сигналів С1 і С2 відповідно. При інших станах входів V, СІ і СІ здійснюється зберігання інформації.

Рис. 4.32. Графічне позначення мікросхем регістрів:

а - К155ИР1, К133ИР1, К134ИР1, К555ИР1;

б - К133ИР13,К155ИР13;

в - К5$5ИР22(ИР23), К531ИР22(ИР23);

г - К555ИР27.

Регістр

К133ИР13 (К155ИР13) (рис. 4.32,6)

реалізує наступні мікрооперації:

встановлення "0" при R=0,

зсув вліво при R

=S0

=

![]() =

1,

зсув вправо при R

=

S1

=

=

1,

зсув вправо при R

=

S1

=

![]() =

1,

приймання інформації з входів D0-D7

при R

= S0

= S1=

1.

Ці операції

виконуються при наростанні синхроімпульсу

по С.

При

інших

комбінаціях

на входах R,

S0,

S1

реалізується

режим зберігання.

=

1,

приймання інформації з входів D0-D7

при R

= S0

= S1=

1.

Ці операції

виконуються при наростанні синхроімпульсу

по С.

При

інших

комбінаціях

на входах R,

S0,

S1

реалізується

режим зберігання.

При запису інформації в регістр К133ИР13 можна у паралельному коді її і зчитати з виходів Q0-Q7.

Регістр К555ИР22 (ИР23) (рис4.32,в) є паралельним і має наступні мікрооперації: запис інформації у регістр без попередньої очистки при РЕ=1 (для ИР23 - за наростанням сигналу), видача інформації на вихід при Е0= 0. Якщо Е0 = 1, то на виходах Q1-Q8 буде високоомний стан.