- •Процесори 80х86. Основні характеристики. Типи процесорів: sx, dx, dx-2. Адресний простір. Обчислення адреси.

- •Пам'ять pc. Типи пам'яті (convention, umb, hma, extended, expanded). Cmos - пам'ять, Shadow - пам'ять.

- •Диски, дисководи і контролери. Типи, коротка характеристика.

- •Ms dos. Призначення, особливості й основні компоненти.

- •Комп'ютерні віруси. Способи захисту інформації.

- •Ms dos. Пакетні командні файли. Призначення, команди. Утиліта ве.

- •Os/2. Коротка характеристика. Особливості обчислення адреси.

- •Unix: команди керування файлами і каталогами. Права доступу користувачів.

- •Windows. Коротка характеристика. Режими роботи.

- •Класифікація переривань ibm pc. Апаратні переривання. Маскирование апаратних переривань.

- •Оброблювачі переривань ibm pc. Обробка переривань з використанням мов ассемблера і с. Модифікація оброблювачів переривань.

- •Структура дискових томів у ms dos.

- •Керування дисками і каталогами в ms dos.

- •Com і exe програми. Їх особливості і правила написання.

- •Принципи організації взаємодії користувальницької програми з клавіатурою ibm pc.

- •Принципи організації виводу інформації на екран ibm pc.

- •Принципи організації виводу інформації на принтер для ibm pc.

- •Файлова система ms dos, функції з використанням fcb і дескриптора.

- •Основи створення резидентних програм для ms dos.

- •Компоновщики і завантажники. Призначення і застосування.

- •Відладчики, дизасемблери і профайлери. Призначення. Функції і можливості.

- •Утиліти. Призначення. Приклади використання.

- •Комп'ютерна електроніка

- •T, jk, d, rs - тригери. Принцип роботи. Синхронні й асинхронні тригери.

- •Двоступінчасті тригери за схемою ms. Тригери з керуванням по фронту. Принцип роботи. Область застосування.

- •Шифрувачі і дешифрувачі. Синтез комбінаційних схем (кс) на базі дешифрувачів.

- •Мультиплексори. Синтез кс на мультиплексорах.

- •Синтез операційних елементів комбінаційного типу.

- •Регістри. Загальні відомості, класифікація і принцип роботи.

- •Методика синтезу багатофункціональних регістрів.

- •Лічильники. Принцип дії, класифікація. Синтез лічильників з довільним модулем і порядком рахунку.

- •Додавачі. Основні поняття і визначення. Перенос у додавачах.

- •Програмуємі логічні матриці (плм). Синтез схем із застосуванням плм.

- •Запам'ятовуючі пристрої. Класифікація, структура, принцип дії.

- •Постійні запам'ятовуючі пристрої (пзп). Синтез схем на базі пзп.

- •Арифметико-логічні пристрої. Принцип дії, використання в обчислювальній техніці.

- •Розподільники тактів. Методи синтезу розподільників по заданих часових діаграмах.

- •Аналогові обчислювальні машини. Основні вирішальні елементи.

- •Структурні міри інформації. Статична міра інформації, поняття ентропії.

- •2. Комбинаторная мера.

- •3. Логарифмическая мера.

- •Властивості безумовної ентропії.

- •Умовна ентропія, властивості умовної ентропії.

- •Ентропія й інформація, властивості інформації.

- •Квантування інформації. Теорема Котельникова.

- •Основна теорема про кодування для каналу без шуму. Оптимальне кодування.

- •Коди Шеннона-Фано і Хаффмена.

- •Коди, що виявляють помилки і коректують коди. Код Хемминга.

- •Групові коди. Циклічні коди.

- •Семантичний розрив між архітектурою еом і мовами високого рівня.

- •Основи горизонтальної і вертикальної обробки інформації.

- •Використання матричного паралелізму в архітектурі спеціалізованих еом.

- •Використання конвеєрного паралелізму в архітектурі спеціалізованих еом.

- •Заготівля результату в архітектурі спеціалізованих еом.

- •Машини потоків даних.

- •Асоціативні системи.

- •Матричні системи.

- •Конвеєрні системи.

- •Багатопроцесорні системи.

- •Багатомашинні системи.

- •Топологічні структури обчислювальних систем. Приклади реалізацій.

- •Мережі еом

- •Алгоритмічна структура обчислювальних мереж. Призначення протоколів відповідних рівнів.

- •Стандарти комітету ieee в області локальних обчислювальних мереж. Протоколи ieee 802.3, ieee 802.4, ieee 802.5.

- •Стандарт швидкісної оптичної магістралі fddi.

- •Основні складові елементи мережної архітектури.

- •Стандарти швидкісних магістралей Fast Ethernet, Switch Ethernet, 100vg.

- •Архітектурні особливості малих локальних мереж. Структура мережі битбас.

Матричні системи.

Назначение матричных вычислительных систем - обработка больших массивов данных (во многом схоже с назначением векторных ВС). В основе матричных систем лежит матричный процессор (array processor), состоящий из регулярного массива процессорных элементов (ПЭ).

Организация систем подобного типа на первый взгляд достаточно проста. Они имеют общее управляющее устройство, генерирующее поток команд, и большое число ПЭ, работающих параллельно и обрабатывающих каждый свой поток данных.

Между матричными и векторными системами есть существенная разница. Матричный процессор интегрирует множество идентичных функциональных блоков (ФБ), логически объединенных в матрицу и работающих в SIMD-стиле. Не столь существенно, как конструктивно реализована матрица процессорных элементов — на едином кристалле или на нескольких. Важен сам принцип - ФБ логически скомпонованы в матрицу и работают синхронно, то есть присутствует только один поток команд для всех. Векторный процессор имеет встроенные команды для обработки векторов данных, что позволяет эффективно загрузить конвейер из функциональных блоков. В свою очередь, векторные процессоры проще использовать, потому что команды для обработки векторов — это более удобная для человека модель программирования, чем SIMD.

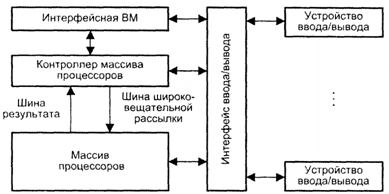

Структуру матричной вычислительной системы можно представить в следующем виде.

Обобщенная модель матричной ВС

Рассмотрим компоненты обобщенной модели матричной ВС.

Массив процессоров (МПр) осуществляет параллельную обработку множественных элементов данных.

Контроллер массива процессоров (КМП) генерирует единый поток команд, управляющий обработкой данных в массиве процессоров, выполняет последовательный программный код, реализует операции условного и безусловного переходов, транслирует в МПр команды, данные и сигналы управления. Команды обрабатываются процессорами в режиме жесткой синхронизации.

Сигналы управления используются для синхронизации команд и пересылок, а также для управления процессом вычислений, в частности определяют, какие процессоры массива должны выполнять операцию, а какие - нет.

Шина широковещательной рассылки служит для передачи команд, данных и сигналов управления из КМП в массив процессоров.

Шина результата служит для трансляции результатов вычислений из МПр в КМП (это требуется, поскольку выполнение операций условного перехода зависит от результатов вычислений).

Конвеєрні системи.

Конвейеризация (или конвейерная обработка) в общем случае основана на разделении подлежащей исполнению функции на более мелкие части, называемые ступенями, и выделении для каждой из них отдельного блока аппаратуры. Так обработку любой машинной команды можно разделить на несколько этапов (несколько ступеней), организовав передачу данных от одного этапа к следующему. При этом конвейерную обработку можно использовать для совмещения этапов выполнения разных команд. Производительность при этом возрастает благодаря тому, что одновременно на различных ступенях конвейера выполняются несколько команд. Конвейерная обработка такого рода широко применяется во всех современных быстродействующих процессорах.

Выполнение типичной команды можно разделить на следующие этапы:

выборка команды - IF (по адресу, заданному счетчиком команд, из памяти извлекается команда);

декодирование команды / выборка операндов из регистров - ID;

выполнение операции / вычисление эффективного адреса памяти - EX;

обращение к памяти - MEM;

запоминание результата - WB.

Конвейеризация увеличивает пропускную способность процессора (количество команд, завершающихся в единицу времени), но она не сокращает время выполнения отдельной команды. В действительности, она даже несколько увеличивает время выполнения каждой команды из-за накладных расходов, связанных с управлением регистровыми станциями. Однако увеличение пропускной способности означает, что программа будет выполняться быстрее по сравнению с простой неконвейерной схемой.