- •Процесори 80х86. Основні характеристики. Типи процесорів: sx, dx, dx-2. Адресний простір. Обчислення адреси.

- •Пам'ять pc. Типи пам'яті (convention, umb, hma, extended, expanded). Cmos - пам'ять, Shadow - пам'ять.

- •Диски, дисководи і контролери. Типи, коротка характеристика.

- •Ms dos. Призначення, особливості й основні компоненти.

- •Комп'ютерні віруси. Способи захисту інформації.

- •Ms dos. Пакетні командні файли. Призначення, команди. Утиліта ве.

- •Os/2. Коротка характеристика. Особливості обчислення адреси.

- •Unix: команди керування файлами і каталогами. Права доступу користувачів.

- •Windows. Коротка характеристика. Режими роботи.

- •Класифікація переривань ibm pc. Апаратні переривання. Маскирование апаратних переривань.

- •Оброблювачі переривань ibm pc. Обробка переривань з використанням мов ассемблера і с. Модифікація оброблювачів переривань.

- •Структура дискових томів у ms dos.

- •Керування дисками і каталогами в ms dos.

- •Com і exe програми. Їх особливості і правила написання.

- •Принципи організації взаємодії користувальницької програми з клавіатурою ibm pc.

- •Принципи організації виводу інформації на екран ibm pc.

- •Принципи організації виводу інформації на принтер для ibm pc.

- •Файлова система ms dos, функції з використанням fcb і дескриптора.

- •Основи створення резидентних програм для ms dos.

- •Компоновщики і завантажники. Призначення і застосування.

- •Відладчики, дизасемблери і профайлери. Призначення. Функції і можливості.

- •Утиліти. Призначення. Приклади використання.

- •Комп'ютерна електроніка

- •T, jk, d, rs - тригери. Принцип роботи. Синхронні й асинхронні тригери.

- •Двоступінчасті тригери за схемою ms. Тригери з керуванням по фронту. Принцип роботи. Область застосування.

- •Шифрувачі і дешифрувачі. Синтез комбінаційних схем (кс) на базі дешифрувачів.

- •Мультиплексори. Синтез кс на мультиплексорах.

- •Синтез операційних елементів комбінаційного типу.

- •Регістри. Загальні відомості, класифікація і принцип роботи.

- •Методика синтезу багатофункціональних регістрів.

- •Лічильники. Принцип дії, класифікація. Синтез лічильників з довільним модулем і порядком рахунку.

- •Додавачі. Основні поняття і визначення. Перенос у додавачах.

- •Програмуємі логічні матриці (плм). Синтез схем із застосуванням плм.

- •Запам'ятовуючі пристрої. Класифікація, структура, принцип дії.

- •Постійні запам'ятовуючі пристрої (пзп). Синтез схем на базі пзп.

- •Арифметико-логічні пристрої. Принцип дії, використання в обчислювальній техніці.

- •Розподільники тактів. Методи синтезу розподільників по заданих часових діаграмах.

- •Аналогові обчислювальні машини. Основні вирішальні елементи.

- •Структурні міри інформації. Статична міра інформації, поняття ентропії.

- •2. Комбинаторная мера.

- •3. Логарифмическая мера.

- •Властивості безумовної ентропії.

- •Умовна ентропія, властивості умовної ентропії.

- •Ентропія й інформація, властивості інформації.

- •Квантування інформації. Теорема Котельникова.

- •Основна теорема про кодування для каналу без шуму. Оптимальне кодування.

- •Коди Шеннона-Фано і Хаффмена.

- •Коди, що виявляють помилки і коректують коди. Код Хемминга.

- •Групові коди. Циклічні коди.

- •Семантичний розрив між архітектурою еом і мовами високого рівня.

- •Основи горизонтальної і вертикальної обробки інформації.

- •Використання матричного паралелізму в архітектурі спеціалізованих еом.

- •Використання конвеєрного паралелізму в архітектурі спеціалізованих еом.

- •Заготівля результату в архітектурі спеціалізованих еом.

- •Машини потоків даних.

- •Асоціативні системи.

- •Матричні системи.

- •Конвеєрні системи.

- •Багатопроцесорні системи.

- •Багатомашинні системи.

- •Топологічні структури обчислювальних систем. Приклади реалізацій.

- •Мережі еом

- •Алгоритмічна структура обчислювальних мереж. Призначення протоколів відповідних рівнів.

- •Стандарти комітету ieee в області локальних обчислювальних мереж. Протоколи ieee 802.3, ieee 802.4, ieee 802.5.

- •Стандарт швидкісної оптичної магістралі fddi.

- •Основні складові елементи мережної архітектури.

- •Стандарти швидкісних магістралей Fast Ethernet, Switch Ethernet, 100vg.

- •Архітектурні особливості малих локальних мереж. Структура мережі битбас.

Використання матричного паралелізму в архітектурі спеціалізованих еом.

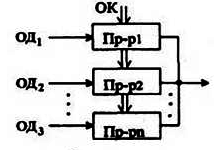

Архитектура ОКМД предполагает создание структур векторной или матричной обработки. Системы этого типа обычно строятся как однородные, т.е. процессорные элементы, входящие в систему, идентичны, и все они управляются одной и той же последовательностью команд. Однако каждый процессор обрабатывает свой поток данных. Под эту схему хорошо подходят задачи обработки матриц или векторов (массивов), задачи решения систем линейных и нелинейных, алгебраических и дифференциальных уравнений, задачи теории поля и др. В структурах данной архитектуры желательно обеспечивать соединения между процессорами, соответствующие реализуемым математическим зависимостям. Как правило, эти связи напоминают матрицу, в которой каждый процессорный элемент связан с соседними.

рис.

Архитектура ОКМД

рис.

Архитектура ОКМД

По данной схеме строились системы: первая суперЭВМ - ILLIAC-IV, отечественные параллельные системы - ПС-2000, ПС-3000. Идея векторной обработки широко использовалась в таких известных суперЭВМ, как Cyber-205 и Gray-I, II, III. Узким местом подобных систем является необходимость изменения коммутации между процессорами, когда связь между ними отличается от матричной. Кроме того, задачи, допускающие широкий матричный параллелизм, составляют достаточно узкий класс задач. Структуры ВС этого типа, по существу, являются структурами специализированных суперЭВМ.

Використання конвеєрного паралелізму в архітектурі спеціалізованих еом.

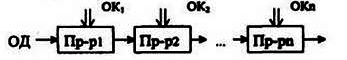

Третий тип архитектуры МКОД предполагает построение своеобразного процессорного конвейера, в котором результаты обработки передаются от одного процессора к другому по цепочке. Выгоды такого вида обработки понятны. Прототипом таких вычислений может служить схема любого производственного конвейера. В современных ЭВМ по этому принципу реализована схема совмещения операций, в которой параллельно работают различные функциональные блоки, и каждый из них делает свою часть в общем цикле обработки команды.

рис.

Архитектуры МКОД

рис.

Архитектуры МКОД

В ВС этого типа конвейер должны образовывать группы процессоров. Однако при переходе на системный уровень очень трудно выявить подобный регулярный характер в универсальных вычислениях. Кроме того, на практике нельзя обеспечить и “большую длину” такого конвейера, при которой достигается наивысший эффект. Вместе с тем конвейерная схема нашла применение в так называемых скалярных процессорах суперЭВМ, в которых они применяются как специальные процессоры для поддержки векторной обработки.

Заготівля результату в архітектурі спеціалізованих еом.

Запоминающие устройства обеспечивают хранение исходных и промежуточных данных, результатов вычислений, а также программ. Они включают: оперативные (ОЗУ), сверхоперативные СОЗУ), постоянные (ПЗУ) и внешние (ВЗУ) запоминающие устройства.

Оперативные ЗУ хранят информацию, с которой компьютер работает непосредственно в данное время (резидентная часть операционной системы, прикладная программа, обрабатываемые данные). В СОЗУ хранится наиболее часто используемые процессором данные. Только та информация, которая хранится в СОЗУ и ОЗУ, непосредственно доступна процессору.

Внешние запоминающие устройства (накопители на магнитных дисках, например, жесткий диск или винчестер) с емкостью намного больше, чем ОЗУ, но с существенно более медленным доступом, используются для длительного хранения больших объемов информации. Например, операционная система (ОС) хранится на жестком диске, но при запуске компьютера резидентная часть ОС загружается в ОЗУ и находится там до завершения сеанса работы ПК.

ПЗУ (постоянные запоминающие устройства) и ППЗУ (перепрограммируемые постоянные запоминающие устройства) предназначены для постоянного хранения информации, которая записывается туда при ее изготовлении, например, ППЗУ для BIOS.