- •Процесори 80х86. Основні характеристики. Типи процесорів: sx, dx, dx-2. Адресний простір. Обчислення адреси.

- •Пам'ять pc. Типи пам'яті (convention, umb, hma, extended, expanded). Cmos - пам'ять, Shadow - пам'ять.

- •Диски, дисководи і контролери. Типи, коротка характеристика.

- •Ms dos. Призначення, особливості й основні компоненти.

- •Комп'ютерні віруси. Способи захисту інформації.

- •Ms dos. Пакетні командні файли. Призначення, команди. Утиліта ве.

- •Os/2. Коротка характеристика. Особливості обчислення адреси.

- •Unix: команди керування файлами і каталогами. Права доступу користувачів.

- •Windows. Коротка характеристика. Режими роботи.

- •Класифікація переривань ibm pc. Апаратні переривання. Маскирование апаратних переривань.

- •Оброблювачі переривань ibm pc. Обробка переривань з використанням мов ассемблера і с. Модифікація оброблювачів переривань.

- •Структура дискових томів у ms dos.

- •Керування дисками і каталогами в ms dos.

- •Com і exe програми. Їх особливості і правила написання.

- •Принципи організації взаємодії користувальницької програми з клавіатурою ibm pc.

- •Принципи організації виводу інформації на екран ibm pc.

- •Принципи організації виводу інформації на принтер для ibm pc.

- •Файлова система ms dos, функції з використанням fcb і дескриптора.

- •Основи створення резидентних програм для ms dos.

- •Компоновщики і завантажники. Призначення і застосування.

- •Відладчики, дизасемблери і профайлери. Призначення. Функції і можливості.

- •Утиліти. Призначення. Приклади використання.

- •Комп'ютерна електроніка

- •T, jk, d, rs - тригери. Принцип роботи. Синхронні й асинхронні тригери.

- •Двоступінчасті тригери за схемою ms. Тригери з керуванням по фронту. Принцип роботи. Область застосування.

- •Шифрувачі і дешифрувачі. Синтез комбінаційних схем (кс) на базі дешифрувачів.

- •Мультиплексори. Синтез кс на мультиплексорах.

- •Синтез операційних елементів комбінаційного типу.

- •Регістри. Загальні відомості, класифікація і принцип роботи.

- •Методика синтезу багатофункціональних регістрів.

- •Лічильники. Принцип дії, класифікація. Синтез лічильників з довільним модулем і порядком рахунку.

- •Додавачі. Основні поняття і визначення. Перенос у додавачах.

- •Програмуємі логічні матриці (плм). Синтез схем із застосуванням плм.

- •Запам'ятовуючі пристрої. Класифікація, структура, принцип дії.

- •Постійні запам'ятовуючі пристрої (пзп). Синтез схем на базі пзп.

- •Арифметико-логічні пристрої. Принцип дії, використання в обчислювальній техніці.

- •Розподільники тактів. Методи синтезу розподільників по заданих часових діаграмах.

- •Аналогові обчислювальні машини. Основні вирішальні елементи.

- •Структурні міри інформації. Статична міра інформації, поняття ентропії.

- •2. Комбинаторная мера.

- •3. Логарифмическая мера.

- •Властивості безумовної ентропії.

- •Умовна ентропія, властивості умовної ентропії.

- •Ентропія й інформація, властивості інформації.

- •Квантування інформації. Теорема Котельникова.

- •Основна теорема про кодування для каналу без шуму. Оптимальне кодування.

- •Коди Шеннона-Фано і Хаффмена.

- •Коди, що виявляють помилки і коректують коди. Код Хемминга.

- •Групові коди. Циклічні коди.

- •Семантичний розрив між архітектурою еом і мовами високого рівня.

- •Основи горизонтальної і вертикальної обробки інформації.

- •Використання матричного паралелізму в архітектурі спеціалізованих еом.

- •Використання конвеєрного паралелізму в архітектурі спеціалізованих еом.

- •Заготівля результату в архітектурі спеціалізованих еом.

- •Машини потоків даних.

- •Асоціативні системи.

- •Матричні системи.

- •Конвеєрні системи.

- •Багатопроцесорні системи.

- •Багатомашинні системи.

- •Топологічні структури обчислювальних систем. Приклади реалізацій.

- •Мережі еом

- •Алгоритмічна структура обчислювальних мереж. Призначення протоколів відповідних рівнів.

- •Стандарти комітету ieee в області локальних обчислювальних мереж. Протоколи ieee 802.3, ieee 802.4, ieee 802.5.

- •Стандарт швидкісної оптичної магістралі fddi.

- •Основні складові елементи мережної архітектури.

- •Стандарти швидкісних магістралей Fast Ethernet, Switch Ethernet, 100vg.

- •Архітектурні особливості малих локальних мереж. Структура мережі битбас.

Методика синтезу багатофункціональних регістрів.

Многофункциональный регистр Может выполнять различные операции

Например Yi - сброс, Y2 - прием числа, Y3 - сдвиг содержимого на 1 разряд влево, сдвиг содержимого на 1 разряд вправо и др.

Регистр - это определенный участок памяти внутри самого процессора, от 8-ми до 32-х бит длиной, который используется для промежуточного хранения информации, обрабатываемой процессором. Некоторые регистры содержат только определенную информацию.

Регистры общего назначения - EAX, EBX, ECX, EDX. Они 32-х битные и делятся еще на две части, нижние из которых AX, BX, CD, DX - 16-ти битные, и деляется еще на два 8-ми битных регистра. Так, АХ делится на AH и AL, DX на DH и DL и т.д. Буква "Н" означает верхний регистр.

Так, AH и AL каждый по одному байту, АХ - 2 байта (или word - слово), ЕАХ - 4 байта (или dword - двойное слово). Эти регистры используются для операций с данными, такими, как сравнение, математические операции или запись данных в память. Регистр СХ чаще всего используется как счетчик в циклах. АН в DOS программах используется как определитель, какой сервис будет использоваться при вызове INT.

Регистры сегментов - это CS, DS, ES, FS, GS, SS. Эти регистры 16-ти битные, и содержат в себе первую половину адреса "оффсет:сегмент".

CS - сегмент кода (страница памяти) исполняемой в данный момент программы.

DS - сегмент (страница) данных исполняемой программы, т.е. константы, т.д.

SS - сегмент стека исполняемой программы.

ES, FS, GS - дополнительные сегменты, и могут не использоваться программой.

Лічильники. Принцип дії, класифікація. Синтез лічильників з довільним модулем і порядком рахунку.

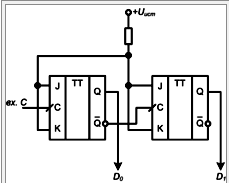

Счётчик числа импульсов — устройство, на выходах которого получается двоичный (двоично-десятичный) код, определяемый числом поступивших импульсов. Счётчики могут строиться на двухступенчатых D-триггерах, T-триггерах и JK-триггерах.

Основной параметр счётчика — модуль счёта — максимальное число единичных сигналов, которое может быть сосчитано счётчиком.

Двухразрядный

двоичный асинхронный суммирующий

счётчик с последовательной организацией

переноса на JK-триггерах.

Двухразрядный

двоичный асинхронный суммирующий

счётчик с последовательной организацией

переноса на JK-триггерах.

Счётчики классифицируют:

по числу устойчивых состояний триггеров

на двоичных триггерах

на троичных триггерах

на n-ичных триггерах

по модулю счёта:

двоично-десятичные (декада);

двоичные;

с произвольным постоянным модулем счёта;

с переменным модулем счёта;

по направлению счёта:

суммирующие;

вычитающие;

реверсивные;

по способу формирования внутренних связей:

с последовательным переносом;

с ускоренным переносом;

с параллельным ускоренным переносом;

со сквозным ускоренным переносом;

с комбинированным переносом;

кольцевые;

по способу переключения триггера: синхронные; асинхронне ;Счётчик Джонсона

Двоичные счетчики

Схему двоичного счетчика можно получить с помощью формального синтеза, однако более наглядным путем представляется эвристический. Таблица истинности двоичного счетчика — последовательность двоичных чисел от нуля до , где n - разрядность счётчика. Наблюдение за разрядами чисел, составляющих таблицу, приводит к пониманию структурной схемы двоичного счетчика