- •Процесори 80х86. Основні характеристики. Типи процесорів: sx, dx, dx-2. Адресний простір. Обчислення адреси.

- •Пам'ять pc. Типи пам'яті (convention, umb, hma, extended, expanded). Cmos - пам'ять, Shadow - пам'ять.

- •Диски, дисководи і контролери. Типи, коротка характеристика.

- •Ms dos. Призначення, особливості й основні компоненти.

- •Комп'ютерні віруси. Способи захисту інформації.

- •Ms dos. Пакетні командні файли. Призначення, команди. Утиліта ве.

- •Os/2. Коротка характеристика. Особливості обчислення адреси.

- •Unix: команди керування файлами і каталогами. Права доступу користувачів.

- •Windows. Коротка характеристика. Режими роботи.

- •Класифікація переривань ibm pc. Апаратні переривання. Маскирование апаратних переривань.

- •Оброблювачі переривань ibm pc. Обробка переривань з використанням мов ассемблера і с. Модифікація оброблювачів переривань.

- •Структура дискових томів у ms dos.

- •Керування дисками і каталогами в ms dos.

- •Com і exe програми. Їх особливості і правила написання.

- •Принципи організації взаємодії користувальницької програми з клавіатурою ibm pc.

- •Принципи організації виводу інформації на екран ibm pc.

- •Принципи організації виводу інформації на принтер для ibm pc.

- •Файлова система ms dos, функції з використанням fcb і дескриптора.

- •Основи створення резидентних програм для ms dos.

- •Компоновщики і завантажники. Призначення і застосування.

- •Відладчики, дизасемблери і профайлери. Призначення. Функції і можливості.

- •Утиліти. Призначення. Приклади використання.

- •Комп'ютерна електроніка

- •T, jk, d, rs - тригери. Принцип роботи. Синхронні й асинхронні тригери.

- •Двоступінчасті тригери за схемою ms. Тригери з керуванням по фронту. Принцип роботи. Область застосування.

- •Шифрувачі і дешифрувачі. Синтез комбінаційних схем (кс) на базі дешифрувачів.

- •Мультиплексори. Синтез кс на мультиплексорах.

- •Синтез операційних елементів комбінаційного типу.

- •Регістри. Загальні відомості, класифікація і принцип роботи.

- •Методика синтезу багатофункціональних регістрів.

- •Лічильники. Принцип дії, класифікація. Синтез лічильників з довільним модулем і порядком рахунку.

- •Додавачі. Основні поняття і визначення. Перенос у додавачах.

- •Програмуємі логічні матриці (плм). Синтез схем із застосуванням плм.

- •Запам'ятовуючі пристрої. Класифікація, структура, принцип дії.

- •Постійні запам'ятовуючі пристрої (пзп). Синтез схем на базі пзп.

- •Арифметико-логічні пристрої. Принцип дії, використання в обчислювальній техніці.

- •Розподільники тактів. Методи синтезу розподільників по заданих часових діаграмах.

- •Аналогові обчислювальні машини. Основні вирішальні елементи.

- •Структурні міри інформації. Статична міра інформації, поняття ентропії.

- •2. Комбинаторная мера.

- •3. Логарифмическая мера.

- •Властивості безумовної ентропії.

- •Умовна ентропія, властивості умовної ентропії.

- •Ентропія й інформація, властивості інформації.

- •Квантування інформації. Теорема Котельникова.

- •Основна теорема про кодування для каналу без шуму. Оптимальне кодування.

- •Коди Шеннона-Фано і Хаффмена.

- •Коди, що виявляють помилки і коректують коди. Код Хемминга.

- •Групові коди. Циклічні коди.

- •Семантичний розрив між архітектурою еом і мовами високого рівня.

- •Основи горизонтальної і вертикальної обробки інформації.

- •Використання матричного паралелізму в архітектурі спеціалізованих еом.

- •Використання конвеєрного паралелізму в архітектурі спеціалізованих еом.

- •Заготівля результату в архітектурі спеціалізованих еом.

- •Машини потоків даних.

- •Асоціативні системи.

- •Матричні системи.

- •Конвеєрні системи.

- •Багатопроцесорні системи.

- •Багатомашинні системи.

- •Топологічні структури обчислювальних систем. Приклади реалізацій.

- •Мережі еом

- •Алгоритмічна структура обчислювальних мереж. Призначення протоколів відповідних рівнів.

- •Стандарти комітету ieee в області локальних обчислювальних мереж. Протоколи ieee 802.3, ieee 802.4, ieee 802.5.

- •Стандарт швидкісної оптичної магістралі fddi.

- •Основні складові елементи мережної архітектури.

- •Стандарти швидкісних магістралей Fast Ethernet, Switch Ethernet, 100vg.

- •Архітектурні особливості малих локальних мереж. Структура мережі битбас.

Двоступінчасті тригери за схемою ms. Тригери з керуванням по фронту. Принцип роботи. Область застосування.

Синхронний двоступінчастий JK-тригер типу MS JK-тригер типу MS із додатковою логікою 3І на J- і K-входах (інтегральна схема типу К155ТВ1* або SN 7472). Тригер даного типу складається із двох послідовно включених елементарних тригерів із протифазною синхронізацією. При цьому перший тригер є провідним або M-тригером (Master– хазяїн), бо виконує логічну функцію, а другий − веденим або S-тригером (Slave раб, підлеглий). Ведений тригер виконує тільки допоміжну функцію зберігання стану провідного при синхросигналі C=1. Роботу JK- тригера розглянемо за схемою його функціонального аналога При J=K=0 синхросигнал C=1 вхідні елементи 1 і 2 блоковані й M-тригер перебуває в режимі зберігання. Відзначимо, що при C=1 (незалежно від стану J- і K-входів) S-тригер завжди перебуває в режимі зберігання, тому що вхідні кон’юнктури 5, 6 блоковані інверсним сигналом С, що становить суть протифазної системи синхронізації.

Триггеры с динамическим управлением воспринимают информационные сигналы при изменении (перепаде) сигнала на входе С от 0 к 1 (прямой динамический С-вход) или от 1 к 0 (инверсный динамический С-вход). Также встречается название «триггер управляемый фронтом»

Шифрувачі і дешифрувачі. Синтез комбінаційних схем (кс) на базі дешифрувачів.

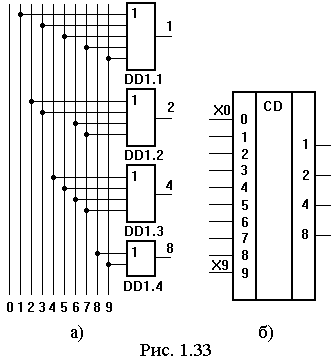

Шифратор (кодер) преобразует сигнал на одном из входов в n-разрядное двоичное число. Функциональная схема шифратора, преобразующего десятичные цифры в 4-разрядное двоичное число, приведена на рисунке 1.33,а, а его условное обозначение – на рисунке 1.33,б. При появлении сигнала логической единицы на одном из десяти входов на четырех выходах шифратора будет присутствовать соответствующее двоичное число. Пусть сигнал логической единицы подан на вход 7. Тогда на выходах логических элементов DD1.1, DD1.2, DD1.3 будут сигналы логических единиц, а на выходе элемента DD1.4 – сигнал логического нуля. Таким образом, на выходах 8, 4, 2, 1 шифратора мы получим двоичное число 0111.

Некоторые из шифраторов снабжаются входом стробирования. Наличие входа стробирования позволяет выделять сигнал в определенный момент времени.

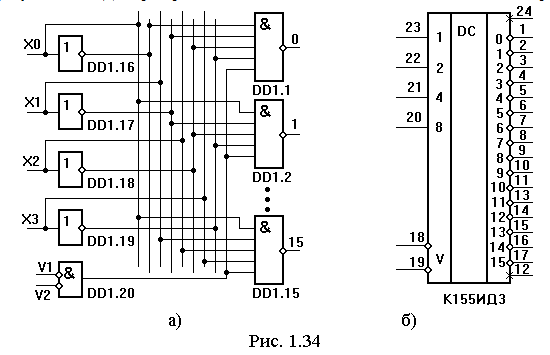

Дешифратор (декодер) преобразует код, поступающий на его входы, в сигнал только на одном из его выходов. Дешифратор n-разряд-ного двоичного числа имеет 2n выходов. Функциональная схема дешифратора на 16 выходов приведена на рисунке 1.34,а. По такой функциональной схеме построена микросхема К155ИД3. Условное обозначение этой микросхемы на принципиальных схемах приведено на рисунке 1.34,б. Для преобразования сигнала необходимо на входы V1 и V2 микросхемы подать сигналы логических нулей.

Пусть на входе дешифратора присутствует двоичное число 1111. В этом случае на всех пяти входах элемента DD1.15 будут сигналы логических единиц, а на выходе этого элемента будет логический нуль. На выходах всех остальных 15 элементов будут сигналы логических единиц. Если хотя бы на одном из входов V логическая единица, то единицы будут на всех 16 выходах.