- •Архитектура системного уровня процессоров ia-32 Задачи архитектуры системного уровня (system-level architecture)

- •Компоненты архитектуры системного уровня

- •Защищенный режим Общие сведениия Назначение защищенного режима микропроцессоров ia-32

- •Режим виртуального процессора 8086

- •Концепция защиты

- •Дескрипторы и таблицы дескрипторов. Системные сегменты

- •Регистры дескрипторов таблиц и системных сегментов

- •Механизм использования глобальной и локальной таблиц дескрипторов

- •Привилегии

- •Кольца защиты Привилегии задач (Task Privilege)

- •Привилегии дескриптора (Descriptor Privilege)

- •Привилегии селектора (Selector Privilege)

- •Привилегии ввода-вывода

- •Дескрипторы системных сегментов

- •Поля байта управления доступом к системным сегментам

- •Межсегментная передача управления

- •Типы и назначение шлюзов

- •Механизм использования шлюза вызова

- •Дескриптор шлюза вызова

- •Поля байта управления доступом дескриптора шлюза

- •Проверка условий, порождающих исключения

- •Инструкции тестирования указателей

- •Виртуальная память

- •Составляющие элементы механизма страничной переадресации

- •Адресация в защищенном режиме

- •Варианты организации страниц виртуальной памяти

- •Управление режимом страничной переадресации

- •Переключение стека

- •Операция переключения задач процессора (Task Switch Operation)

- •Переключение между реальным и защищенным режимами

- •Переключение в защищенный режим из реального:

- •Переключение процессора в реальный режим из защищенного

- •Регистры управления cr1, cr2, cr3

- •Регистр управления cr4

- •Управление прерываниями от fpu

- •Управление блоком fpu

- •Средства отладки по

- •Регистры отладки

- •Средства, предоставляющие дополнительные возможности отладки.

- •Регистр DebugCtlMsr:

- •Режим управления системой (smm)

- •Включение режима

- •Карта контекста процессора в smram

- •Идентификатор smm (Revision Identifier)

- •Базовый адрес smram

- •Некорректность восстановления контекста

- •Инициализация регистров процессора при входе в smm

- •Начальный сброс и тестирование Аппаратный сброс (hardware reset)

- •Установки при сбросе

- •Внутренний тест процессора

- •Начало нормального функционирования процессора

- •Инициализация по сигналу init («мягкий» сброс)

- •Тестирование аппаратных средств процессора

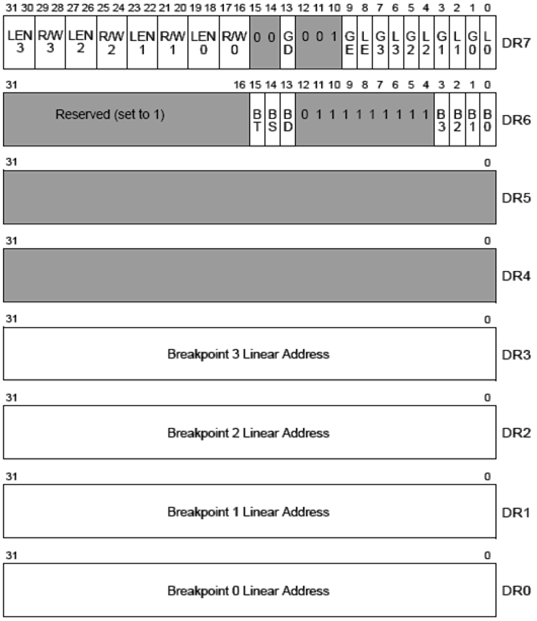

Регистры отладки

RWi – тип перехватываемого обращения:

00 – __________ _______________;

01 – только запись данных в память;

10 – при расширенной отладке (бит DE=1 в CR4) – обращение к _________ _______-_________ (Р5+);

11 – чтение или запись данных в память.

GD (Global Debug Register Access Detect) – отслеживание попыток доступа к отладочным регистрам:

доступен в реальном режиме и в защищенном (на уровне CPL=0);

=1 – любая попытка обращения вызовет #DB (отказ).

LENi – размер области, адресуемой DR0...DR3, попадание в которую вызывает срабатывание ловушки;

00 – байт;

01 – слово (2 байта);

10 – не определено;

11 – двойное слово.

Bi – срабатывание контрольной точки по DRi;

BS – ловушка _______________ _________;

ВТ – ловушка __________________ _______ (бит Т в TSS);

BD – отказ в попытке доступа к _____________ __________ при GD=1.

Причин может быть несколько.

DR7 (Debug Control Register) – управление отладкой

DR6 (Debug Status Register).

GE и LE (Global и Local Exact data breakpoint match) – определяют, будет ли исключение генерироваться сразу после завершения операции обмена при включенной ловушке на область данных или оно произойдет несколько позже (или никогда). При переключении задач: LE – автоматически сбрасывается; GE – не изменяется.

Gi и Li (Global и Local breakpoint enable) –разрешают срабатывание ловушек по ________________ _________.

Средства, предоставляющие дополнительные возможности отладки.

386+:

расстановка точек останова в ПЗУ;

перехват обращений к данным.

Pentium+:

останов по обращениям к портам.

P6+: средства регистрации последнего произошедшего перехода, прерывания или исключения – в составе MSR пять 32-битных регистров.

Регистр DebugCtlMsr:

Бит 0 – LBR (Last Branch/Interrupt/Exception) – разрешение регистрации исходного и целевого адреса перехода/прерывания/исключения. Автоматически сбрасывается по исключению отладки.

Бит 1 – BTF (Single-step on Branches) – установка пошагового режима ___ ________________ ____________. Автоматически сбрасывается по входу в обработчик исключения отладки.

Биты [2:5] – PBi (Performance monitoring/Breakpoint pins) – разрешение индикации (импульсами) ________________ _______ ____________, определенных регистрами DR0...DR3 на выводы BP0#...BP3#. При PBi=0 выводятся события монитора производительности.

Бит 6 – TR (Trace message enable) – разрешение вывода исходного и целевого адреса переходов/прерывания/исключения на системную шину в виде сообщений трассировки переходов (при этом в регистрах трассировки информация будет неопределенной).

LastBranchFromIP – содержимое IP, соответствующее инструкции ветвления;

LastBranchToIP – целевой адрес перехода.

При возникновении прерывания или исключения (кроме исключений отладки):

предварительно содержимое указанных регистров копируется в LastExceptionFromIP и LastExceptionToIP;

в указанные регистры помещаются:

адрес инструкции, во время которой произошло исключение (прерывание);

адрес обработчика.

Режим управления системой (smm)

SMM – System Management Mode.

Введен: некоторые модификации 486 и 386SL.

Суть: выполнение ряда действий _ _________ _____________ ___ от прикладного программного обеспечения и даже ОС.

Основное назначение: реализация системы управления энергопотреблением.