- •Архитектура системного уровня процессоров ia-32 Задачи архитектуры системного уровня (system-level architecture)

- •Компоненты архитектуры системного уровня

- •Защищенный режим Общие сведениия Назначение защищенного режима микропроцессоров ia-32

- •Режим виртуального процессора 8086

- •Концепция защиты

- •Дескрипторы и таблицы дескрипторов. Системные сегменты

- •Регистры дескрипторов таблиц и системных сегментов

- •Механизм использования глобальной и локальной таблиц дескрипторов

- •Привилегии

- •Кольца защиты Привилегии задач (Task Privilege)

- •Привилегии дескриптора (Descriptor Privilege)

- •Привилегии селектора (Selector Privilege)

- •Привилегии ввода-вывода

- •Дескрипторы системных сегментов

- •Поля байта управления доступом к системным сегментам

- •Межсегментная передача управления

- •Типы и назначение шлюзов

- •Механизм использования шлюза вызова

- •Дескриптор шлюза вызова

- •Поля байта управления доступом дескриптора шлюза

- •Проверка условий, порождающих исключения

- •Инструкции тестирования указателей

- •Виртуальная память

- •Составляющие элементы механизма страничной переадресации

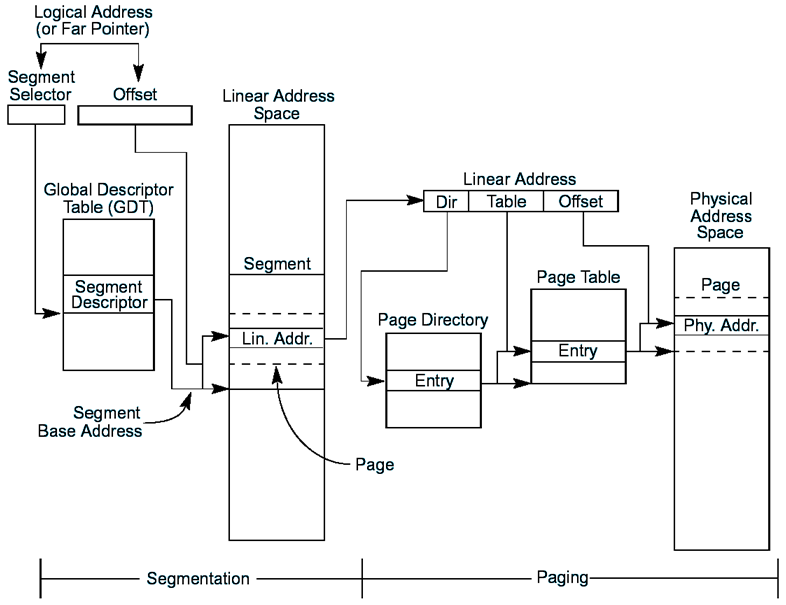

- •Адресация в защищенном режиме

- •Варианты организации страниц виртуальной памяти

- •Управление режимом страничной переадресации

- •Переключение стека

- •Операция переключения задач процессора (Task Switch Operation)

- •Переключение между реальным и защищенным режимами

- •Переключение в защищенный режим из реального:

- •Переключение процессора в реальный режим из защищенного

- •Регистры управления cr1, cr2, cr3

- •Регистр управления cr4

- •Управление прерываниями от fpu

- •Управление блоком fpu

- •Средства отладки по

- •Регистры отладки

- •Средства, предоставляющие дополнительные возможности отладки.

- •Регистр DebugCtlMsr:

- •Режим управления системой (smm)

- •Включение режима

- •Карта контекста процессора в smram

- •Идентификатор smm (Revision Identifier)

- •Базовый адрес smram

- •Некорректность восстановления контекста

- •Инициализация регистров процессора при входе в smm

- •Начальный сброс и тестирование Аппаратный сброс (hardware reset)

- •Установки при сбросе

- •Внутренний тест процессора

- •Начало нормального функционирования процессора

- •Инициализация по сигналу init («мягкий» сброс)

- •Тестирование аппаратных средств процессора

Адресация в защищенном режиме

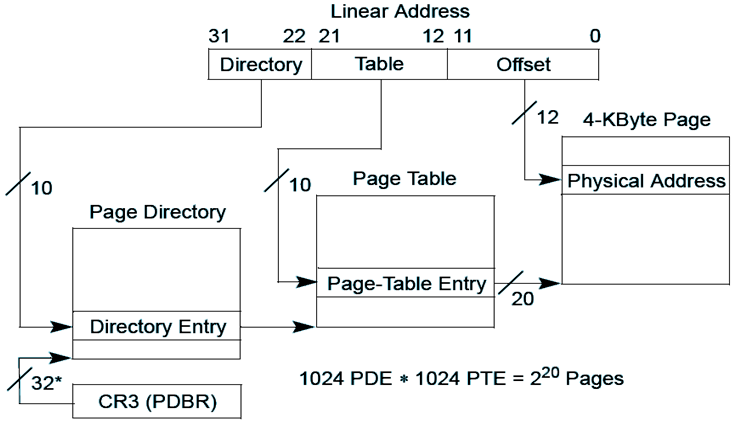

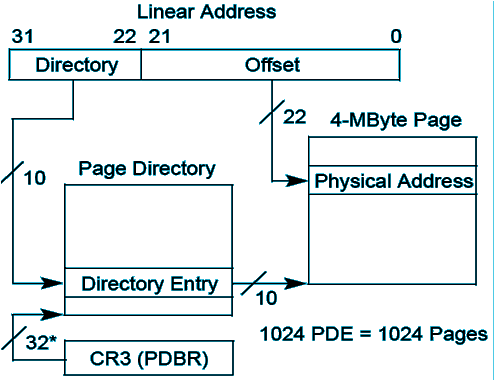

Варианты организации страниц виртуальной памяти

Доступное логическое адресное пространство задачи – до __ _______ (___ сегментов по 4 Гбайт).

386+: размер страницы – _ _______.

Pentium+: возможность увеличения размера страницы до _ _______ (режим PSE), наряду с использованием страниц размером 4 Кбайт.

Р6+: режим расширения физического адреса* до __ бит (РАЕ); страницы размером _ _______ и _ _______.

PIII+: возможность использования страниц размером 4 Мбайт с 36-битной физической адресацией (режим PSE-36).

*Р6+: разрядность ША – 36 бит.

IA-32: разрядность линейного адреса – 32 бит; старшие 4 бита доступны благодаря блоку страничной переадресации.

Без использования дополнительных режимов переадресации (РАЕ или PSE-36) биты [35:32] внешней ША принудительно обнуляются.

Управление режимом страничной переадресации

бит PG в регистре CR0 (PG=1 включает режим);

флаги РАЕ и PSE в CR4;

бит PS в PDE (элементе каталога страницы)

CR0.PG |

CR4.PAE |

CR4.PSE |

PDE.PS |

Размер страницы |

Разрядность физического адреса, бит |

0 |

X |

X |

X |

Трансляция запрещена |

32 |

1 |

0 |

0 |

X |

__ |

32 |

1 |

0 |

1 |

0 |

__ |

32 |

1 |

0 |

1 |

1 |

__ |

32 (PSE) / 36 (PSE-36) |

1 |

1 |

X |

0 |

__ |

36 (РАЕ) |

1 |

1 |

X |

1 |

__ |

36 (РАЕ) |

Использование страниц размером 4 Кбайт

Использование страниц размером 4 Мбайт

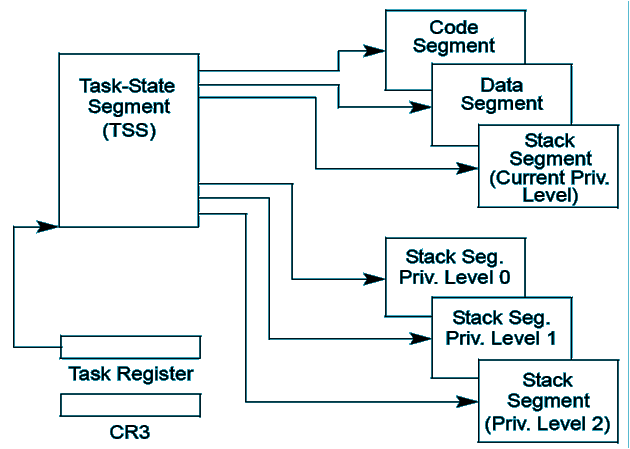

Аппаратная поддержка многозадачности

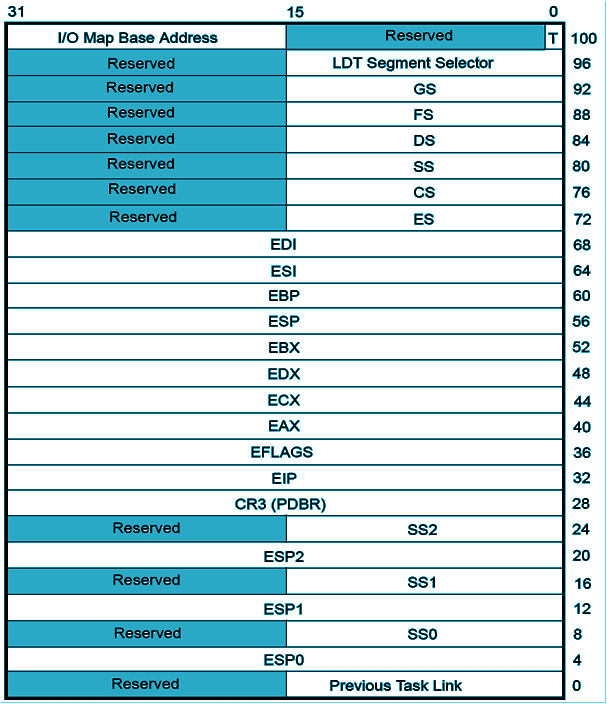

Сегмент состояния задачи

Состояние задачи – значение всех связанных с ней регистров процессора.

Формат TSS 386+: 32-битный/16-битный (в стиле 80286).

Карта разрешения ввода-вывода (I/O Permission Bit Map). Располагается в _______ ____ ____.

Содержит: по одному биту на _________ _______ _________ ввода-вывода; нулевое значение бита разрешает обращение.

Размер:

максимальный – _____ (64К адресов);

может быть урезан лимитом TSS; байт-терминатор 0FFh должен обязательно входить в TSS.

Порты с адресами, не попавшими в усеченную таблицу, считаются __________________.

Селектор в регистре задачи TR указывает на _______________ ____.

Дескриптор _______ _________ содержит селектор, указывающий на дескриптор TSS.

Дескриптор TSS указывает на сегмент, содержащий полное состояние процессора.

Переключение стека

Автоматически при передаче управления ___ _________ _________ _______________.

Начальное значение SS:SP для уровня привилегий 0, 1, 2 содержится в TSS.

При ____________ _______________ (команды JMP или CALL) новое значение указателя стека загружается в SS:SP, старые значения помещаются в новый стек.

При ____________ ___ __________ __________ привилегий его стек восстанавливается (как часть инструкции RET или IRET)