- •Программируемый контроллер прерываний i8259a Общие сведения Основные функции, реализуемые микросхемой i8259а

- •Состояния программируемого контроллера прерываний

- •Режимы обслуживания запросов на прерывания

- •Структурная схема пкп I 8259a

- •Назначение сигналов пкп I 8259a

- •Процедура формирования запроса и обработки прерывания

- •Подсистема пкп компьютера с шиной pci

- •Назначение и форматы управляющих слов пкп

- •Последовательность инициализации пкп

- •Назначение и форматы операционных слов пкп

- •Управление командными словами

- •Доступ к регистрам контроллера пкп в ibm pc at

- •Способы завершения прерывания (eoi)

- •Режимы пкп Режим фиксированных приоритетов

- •Режим полной вложенности

- •Специальный режим полного вложения (sfnm)

- •Режим специального маскирования (smm)

- •Режим опроса источников прерываний (poll)

- •Примеры управления пкп Инициализация пкп – master

- •Инициализация пкп – slave

- •Управление масками запросов

- •Завершение сервисной процедуры

- •Усовершенствованный контроллер прерываний apic

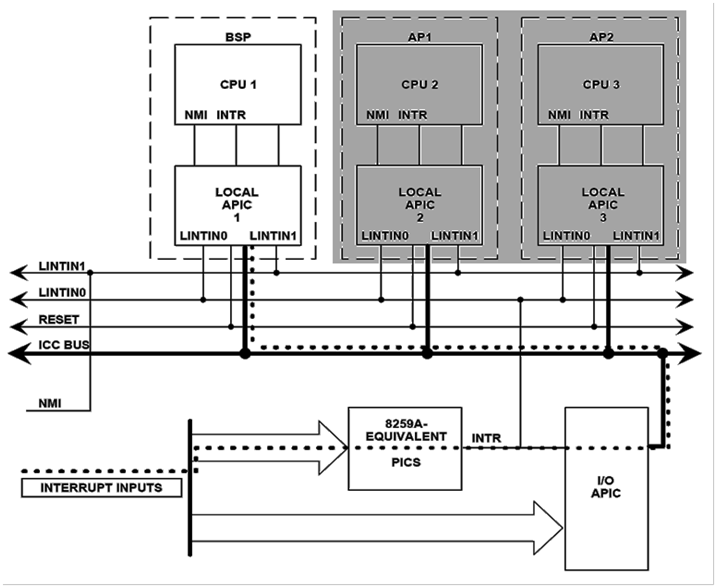

- •Взаимодействие локальных и системных модулей apic

- •Назначение локального модуля apic

- •«Virtual Wire Mode» на основе I/o apic

- •Локальный модуль apic Источники прерываний локального модуля apic

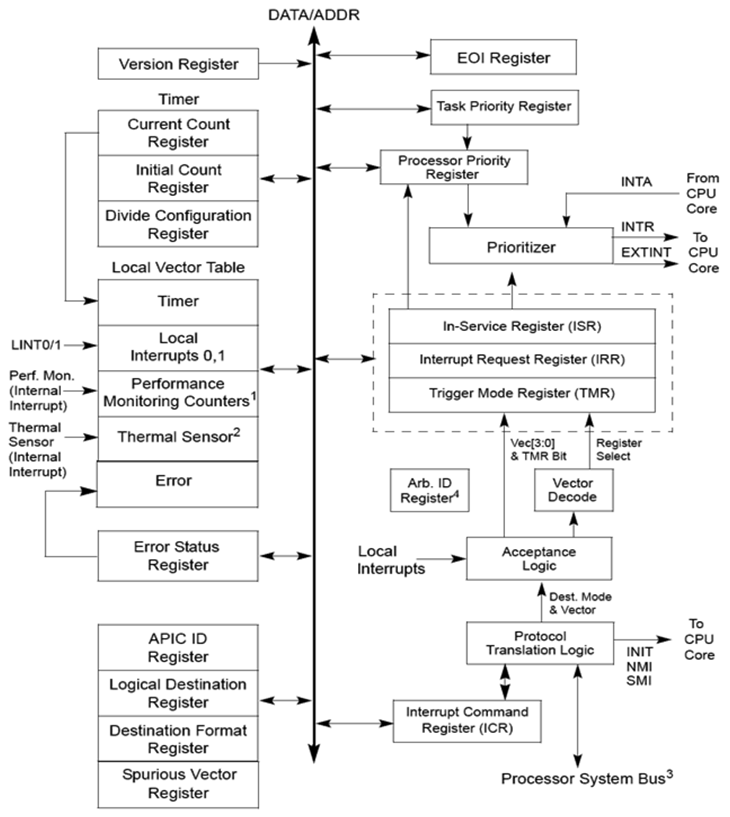

- •Структурная схема локального модуля apic

- •Регистры локального apic

- •Особенности реализации apic Отличия apic от контроллера прерываний на базе двух i8259a

- •Трансляция сообщений msi системной шины

- •Запросы прерываний от шины pci / pci Express

- •Аппаратный интерфейс I/o apic

- •Последовательная схема запросов прерывания

- •Маршрутизация прерываний в I/o apic

- •Пример кс с использованием дискретных локальных модулей apic

- •Пример кс с использованием встроенных локальных модулей apic

«Virtual Wire Mode» на основе I/o apic

«Symmetric I/O Mode»

Локальный модуль apic Источники прерываний локального модуля apic

________________________________устройства (с помощью входов _________________ или посредством внешнего PIC, совместимого с 8259);

_______________________________ устройства (запросы от них поступают на входы системного APIC);

_______________________________________(____) – от других процессоров на системной шине;

встроенный в APIC таймер (запрос по окончании запрограммированного счета);

счетчики ____________________________________________ (запрос при их переполнении; P6+);

датчики температуры (Pentium 4+).

внутренние ___________________________ (напр., попытка записи в недоступный регистр локального APIC.

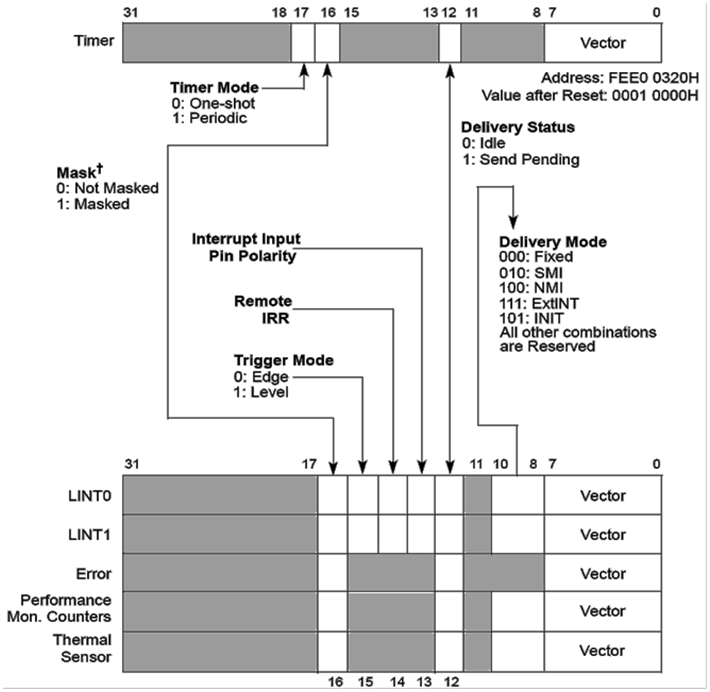

Таблица LVT локального модуля APIC

LVT (локальная таблица векторов, local vector table) – группа ______________________________.

Используется при обслуживании локальных источников (P6+).

Структурная схема локального модуля apic

1) __+.

2) ____________+.

3) 3-проводная шина ICC (_______________).

4) Отсутствует в ____________+.

Регистры локального apic

Смещение |

Назначение |

Тип |

0000h |

Reserved |

|

0010h |

Reserved |

|

0020h |

__________________ Register |

R/W |

0030h |

_________________________ Register |

R |

0040h-0070h |

Reserved |

|

0080h |

_________________________________(____)_ |

R/W |

0090h |

___________________________________________(____)_ |

R |

00A0h |

________________________________________(____)_ |

R |

00B0h |

____ Register |

W |

00C0h |

Reserved |

|

00D0h |

Logical Destination Register |

R/W |

00E0h |

Destination Format Register |

Bits 0-27 R; 28-31 R/W |

00F0h |

Spurious Interrupt Vector Register |

Bits 0-8 R/W; 9-31 R |

_____-_____ |

In-Service Register (ISR) |

R |

_____-______ |

Trigger Mode Register (TMR) |

R |

_____-______ |

Interrupt Request Register (IRR) |

R |

0280h |

Error Status Register |

R |

0290h-02F0h |

Reserved |

|

0300h |

Interrupt Command Register (ICR) [0-31] |

R/W |

0310h |

Interrupt Command Register (ICR) [32-63] |

R/W |

0320h |

LVT _______ Register |

R/W |

0330h |

LVT ____________________ Register |

R/W |

0340h |

LVT _____________________________________________ Register |

R/W |

0350h |

LVT _______ Register |

R/W |

0360h |

LVT _______ Register |

R/W |

0370h |

LVT _______ Register |

R/W |

0380h |

Initial Count Register (for Timer) |

R/W |

0390h |

Current Count Register (for Timer) |

R |

03A0h-03D0h |

Reserved |

|

03E0h |

Divide Configuration Register (for Timer) |

R/W |

03F0h |

Reserved |

|

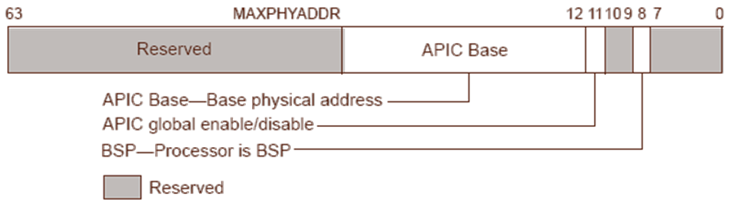

Local APIC Status and Location (IA32_APIC_BASE MSR)

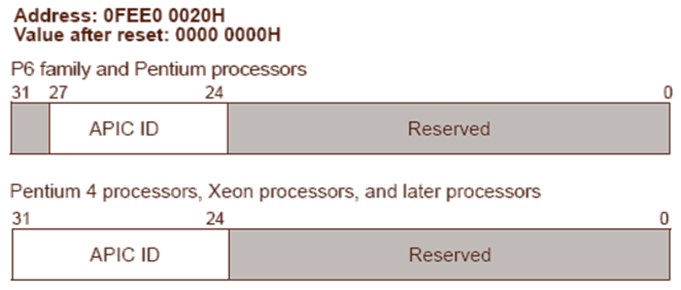

Local APIC ID Register

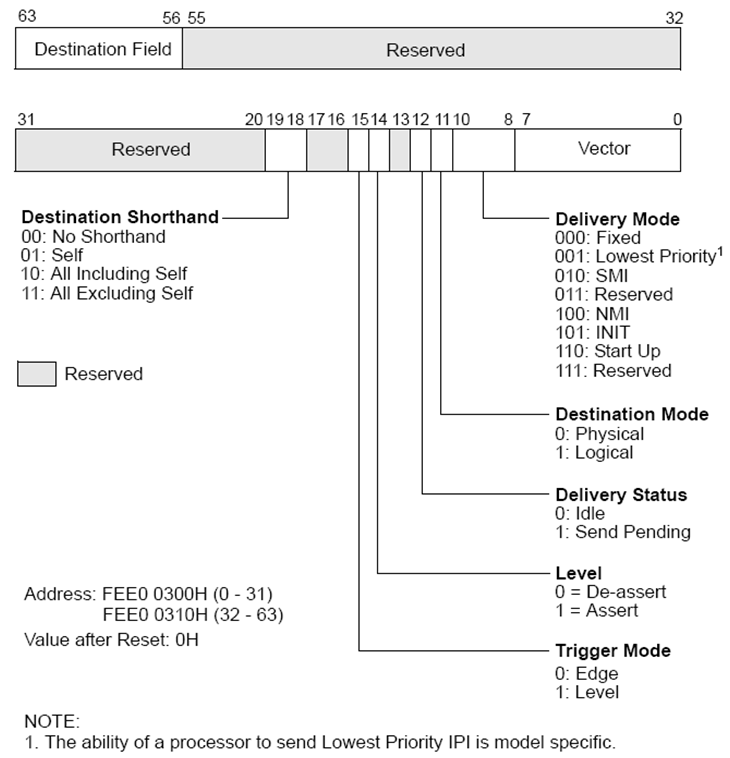

Механизм обмена сообщениями IPI:

1. Процессор генерирует IPI путем программирования ____________________________________________ (____) локального модуля APIC.

2. Локальный APIC передает __________________ по системной шине (Pentium 4+) или шине ICC (Pentium и P6).

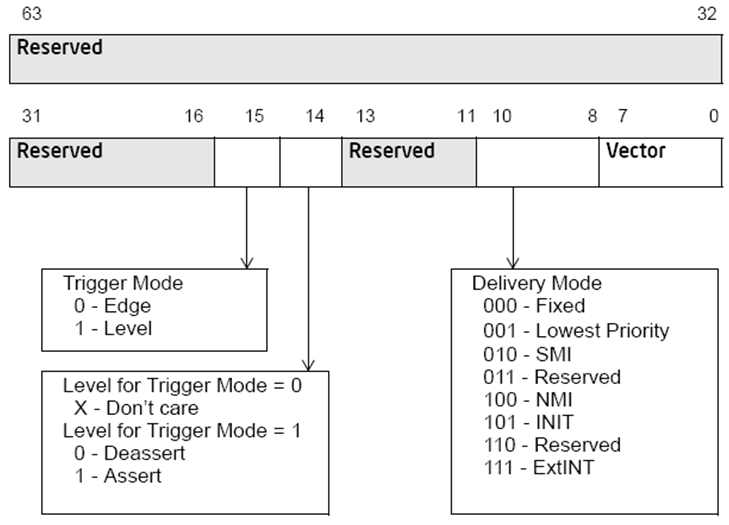

Interrupt Command Register (ICR)

Назначение:

выдача запросов прерываний ____________________________;

пересылка ________________________, необслуживаемого данным процессором, другому процессору;

выдача запроса на прерывание «________________»_(______-_____________);

передача ___________________________________, таких как инициализационные IPI (SIPI), другим процессорам.

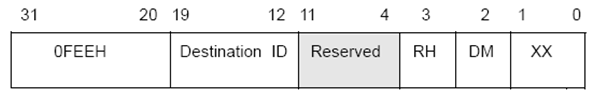

Message Address Register Format

Redirection hint indication (RH)

Destination mode (DM)

Message Data Register Format