- •Программируемый контроллер прерываний i8259a Общие сведения Основные функции, реализуемые микросхемой i8259а

- •Состояния программируемого контроллера прерываний

- •Режимы обслуживания запросов на прерывания

- •Структурная схема пкп I 8259a

- •Назначение сигналов пкп I 8259a

- •Процедура формирования запроса и обработки прерывания

- •Подсистема пкп компьютера с шиной pci

- •Назначение и форматы управляющих слов пкп

- •Последовательность инициализации пкп

- •Назначение и форматы операционных слов пкп

- •Управление командными словами

- •Доступ к регистрам контроллера пкп в ibm pc at

- •Способы завершения прерывания (eoi)

- •Режимы пкп Режим фиксированных приоритетов

- •Режим полной вложенности

- •Специальный режим полного вложения (sfnm)

- •Режим специального маскирования (smm)

- •Режим опроса источников прерываний (poll)

- •Примеры управления пкп Инициализация пкп – master

- •Инициализация пкп – slave

- •Управление масками запросов

- •Завершение сервисной процедуры

- •Усовершенствованный контроллер прерываний apic

- •Взаимодействие локальных и системных модулей apic

- •Назначение локального модуля apic

- •«Virtual Wire Mode» на основе I/o apic

- •Локальный модуль apic Источники прерываний локального модуля apic

- •Структурная схема локального модуля apic

- •Регистры локального apic

- •Особенности реализации apic Отличия apic от контроллера прерываний на базе двух i8259a

- •Трансляция сообщений msi системной шины

- •Запросы прерываний от шины pci / pci Express

- •Аппаратный интерфейс I/o apic

- •Последовательная схема запросов прерывания

- •Маршрутизация прерываний в I/o apic

- •Пример кс с использованием дискретных локальных модулей apic

- •Пример кс с использованием встроенных локальных модулей apic

Программируемый контроллер прерываний i8259a Общие сведения Основные функции, реализуемые микросхемой i8259а

фиксация запросов на прерывание от восьми внешних источников;

оценка приоритета поступившего запроса и формирование очереди на обслуживание в соответствии с установленной дисциплиной;

программное маскирование поступающих запросов;

присвоение циклических или программно изменяемых приоритетов входам контроллера, на которые поступают запросы;

определение и передача процессору номера вектора прерывания.

Состояния программируемого контроллера прерываний

1. Состояние настройки – инициализация и установка режимов работы ПКП путем его программирования как устройства ввода-вывода с помощью четырех управляющих слов инициализации (Initialization Command Word) ICW1-ICW4.

2. Обслуживание запросов – ПКП принимает операционные управляющие слова (слова рабочих команд, Operation Command World) OCW1-OCW3, определяющие алгоритм обслуживания запросов на прерывание в заданном режиме, и осуществляет обслуживание аппаратных прерываний.

Режимы обслуживания запросов на прерывания

фиксированные приоритеты;

автоматический сдвиг приоритетов;

программно-управляемый сдвиг приоритетов;

автоматическое завершение обработки прерывания (Automatic End of Interrupt, AEOI);

специальное маскирование;

опрос.

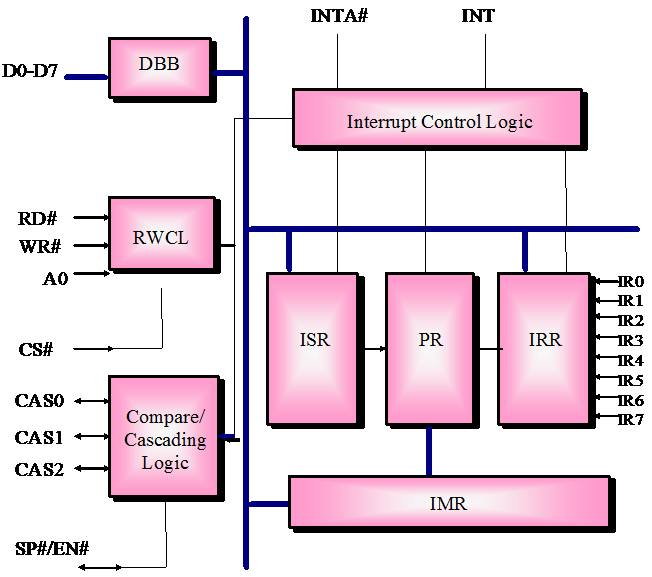

Структурная схема пкп I 8259a

Схема управления прерываниями. Содержит две группы 8-разрядных регистров:

для приема команд инициализации ICW;

для приема рабочих команд OCW.

Основные функции:

прием команд от процессора;

передача процессору информации о состоянии ПКП;

посылка сигнала запроса на вход INТR ЦП;

управление регистрами IRR и ISR в циклах подтверждения прерывания.

Регистры IRR, ISR, IMR, арбитр приоритетов PR. Предназначены для:

восприятия запросов на прерывания на входах IR0-IR7;

управления ими;

разрешения формирования сигнала INT по незамаскированному запросу наивысшего приоритета.

ISR (In Service Register) – Регистр обслуживаемых прерываний. Хранит текущие обрабатываемые запросы («текущий приоритет» ЦП).

IМR (Interrupt Mask Register) – Регистр маскирования запросов. Единичное значение бита означает, что прерывания соответствующего уровня при появлении запроса в IRR блокируются.

IRR (Interrupt Request Register) – Регистр запросов на прерывания. Фиксирует запросы на входах IR.

PR (Priority Resulver) – Арбитр приоритетов. Определяет наиболее приоритетный для выполнения (на данный момент) запрос в IRR.

RWCL (Read/Write Control Logic) – Схема управления чтением/записью. Предназначена для:

анализа сигналов СS#, RD#, WR#, A0;

активизации микросхемы;

инициализации режима чтения процессором содержимого регистров IRR, ISR и IMR;

инициализации режима записи процессором в ПКП управляющих слов ICWi и OCWi.

Назначение сигналов пкп I 8259a

А0 (Address 0). Служит для указания порта i8259A, к которому производится обращение. В IBM PC AT для каждого контроллера резервируется два адреса: для ведущего - 20h и 21h, для ведомого - A0h и A1h. В этом случае вход А0 должен быть подсоединен к разряду 0 шины адреса системного интерфейса.

D0-D7 (bidirectional Data bus) – двунаправленная шина данных. Служит для взаимодействия с ЦПУ.

CS# (Chip Select). Идентифицирует обращение к контроллеру.

RD# (ReaD). Совместно с CS и A0 управляет выдачей на D0-D7 содержимого регистров IMR, ISR и IRR или уровня приоритета.

WR# (WRite). Управляет записью слов инициализации и команд в регистры управления.

INTA# (INTerrupt Acknowlege). Вход подтверждения прерывания от ЦПУ.

IR0-IR7 (Interrupt Request). Входы для запросов прерывания от устройств ввода-вывода или ведомых контроллеров

CASx (Cascade) – Линии каскадирования. Служат для идентификации ведомого контроллера. Для ведущего контроллера являются выходными сигналами, для ведомого – входными

SP#/EN# (Slave Program/ENable buffer). Мультифункциональный: в режиме буфера используется как выходной сигнал для управления приемопередатчиками; в не буферном режиме – как входной сигнал для указания назначения контроллера (SP=0 ведомый, SP=1 ведущий)