- •3)Классификация шин. Их архитектурные особенности. Архитектура материнских плат.

- •4)Архитектура, классификация, физическая организация микросхем памяти и области их применения, технологии системной памяти.

- •7)Кэширование данных

- •8) Конструкция жестких дисков и виды их интерфейсов, логическая организация диска.

- •9)Устройство файловой системы fat, общие сведения об ntfs.

- •5)Логическая организация памяти, адресация памяти в основном режиме работы процессора.

- •6) Адресация памяти в защищенном режиме работы процессора.

- •10) Многоуровневый подход, протокол, интерфейс, уровни модели osi, стандартные стеки протоколов.

- •11) Физический уровень модели osi, среды передачи, сведенья о теории передачи информации.

- •12) Физическое и логическое кодирование.

- •13) Понятие о базовых технологиях лвс, технология Ethernet, спецификации физической среды и правила построения сегментов Ethernet, Fast Ethernet, Gigabit Ethernet.

- •14) Технологии с маркерным методом доступа, основные характеристики технологий Token Ring, fddi.

- •15) Логическая структуризация сетей с помощью мостов и коммутаторов.

- •16) Объединение сетей на основе протоколов сетевого уровня, принципы маршрутизации.

- •18. Коммутация и передача данных в глобальных сетях

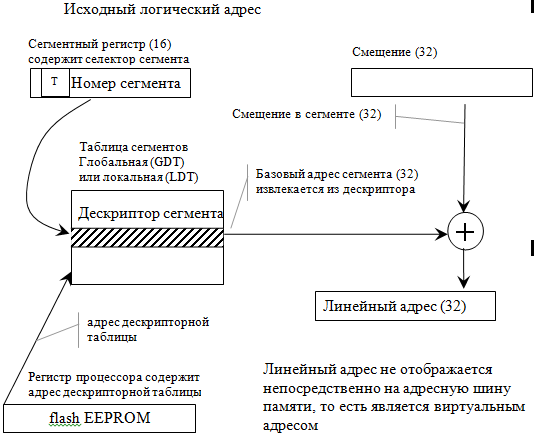

6) Адресация памяти в защищенном режиме работы процессора.

Р еальный

режим процессора Intel – однозадачная

среда, в данный момент времени в ней

может выполняться только одна, конкретная

задача. Все сегменты в этом режиме

доступны для любого процесса, поэтому

в многозадачном режиме процессы могут

мешать друг другу. Для решения этой

проблемы начиная с процессора i80268

был реализован защищенный режим.

Современный вид защищенный режим

приобрел в процессоре i80368

(применительно к 4-х гигабайтному

адресному пространству). Главной

особенностью защищенного режима является

то, что вся многозадачность реализована

аппаратно. Преимущества: возможность

для каждой задачи иметь свою систему

сегментов, сегменты могут быть защищены

от записи, можно указывать уровень

доступа, заложена возможность виртуальной

памяти. Организацию памяти в защищенном

режиме разделяют на 2е части: сегментация

и страничная организация. Сегментация

– это механизма разделения адресного

пространства процессора на отдельные

защищенные друг от друга кусочки

(сегменты). Механизм страничной

памяти позволяет разместить часть

оперативной памяти на диске. Это позволяет

обеспечить прикладные программы

оперативной виртуальной памятью, размер

которой больше размера физической

памяти, установленной в компьютере.

Программы, предназначенные для защищённого

режима, должны быть написаны особым

образом. Это означает, что реальный и

защищённый режим не совместимы. Разделение

адресного пространства на сегменты.

Итак, адресное пространство процесса

делится на части — сегменты, размер

которых определяется с учетом смыслового

значения содержащейся в них информации.

Отдельный сегмент может представлять

собой подпрограмму, массив данных и т.

п. (Еще раз прошу обратить внимание – в

реальном режиме размеры всех сегментов

одинаковые (64 Кбайта), а в защищенном

каждый сегмент имеет собственный

размер.) На этапе создания процесса во

время загрузки его образа в оперативную

память система создает в памяти локальную

таблицу дескрипторов–описателей

сегментов (LDT) процесса. Каждый

дескриптор описывает свой сегмент.

Кроме локальных таблиц дескрипторов

сегментов система создает одну глобальную

таблицу дескрипторов (GDT), где

хранятся дескрипторы сегментов, занятых

операционной системой. Доступ к глобальной

таблице имеют все выполняемые задачи.

Информация в дескрипторе, характеризующую

сегмент: базовый адрес сегмента, резмер

сегмента, тип сегмента, право доступа,

уровень привилегии. Процессы имеют

следующие привилегии: 0-ядро операционной

системы; 1 – программы обслуживающие

аппаратуру, драйвера, программы работающие

с портами ввода/вывода компьютера; 2 –

системы управления базами данных,

расширения операционной системы; 3-

прикладные программы, запускаемые

пользователем. Так же как и в случае

реального режима будет использоваться

двухкомпонентный логический адрес.

По-прежнему логический адрес формируется

при помощи сегментных регистров и

регистров, где хранится смещение. Однако

сегментные регистры содержат теперь

не сегментный адрес, а так называемый

селектор, часть которого (13 бит)

представляет собой индекс в дескрипторной

таблице, т.е. указывает на дескриптор,

в котором находится полная информация

о сегменте. Как это происходит показано

на рис. 24. .Иначе это преобразование

называется трансляция логического

адреса в линейный. Логический адрес

состоит из 16-битового селектора

сегмента и 32-битового смещения в этом

сегменте. Логический адрес преобразуется

в линейный адрес. Адрес сегмента берется

из таблицы глобальных дескрипторов

(GDT). Бит Т (13-й разряд) в селекторе сегмента

определяет, какая таблица (глобальная

или локальная) должна быть использована,

а собственно сам дескриптор определяется

на основании 13 младших разрядов селектора

сегмента. На основании известного

системе адреса таблицы дескрипторов

(определяется специальными регистрами)

и номера сегмента вычисляется адрес

дескриптора сегмента. Получив доступ

к дескриптору, анализируются его поля,

выполняется проверка возможности

выполнения заданной операции. Если

доступ разрешен, то из дескриптора

извлекается адрес этого сегмента и

вычисляется линейный адрес. Если доступ

невозможен, возникает прерывание. Для

нахождения линейного адреса к адресу

сегмента добавляется смещение, заданное

в исходном логическом адресе. В результате

проведенного преобразования мы получили

требуемый 32- разрядный линейный адрес.

Полученный линейный адрес является

виртуальным, т.е. не может быть

непосредственно отправлен на шину

адреса. Механизм страничнаой памяти.

Второй этап преобразования требуется,

потому что реальный компьютер не имеет,

как правило, установленных 4Гб памяти,

т.е. возникает необходимость перейти

от виртуального линейного адреса к

физическому. Полученный линейный

виртуальный адрес преобразуется в

искомый физический адрес. В процессе

страничной трансляции адресов полученный

линейный адрес разбивается на три части.

Старшие десять бит линейного адреса

являются индексом (номером) строки из

каталога таблиц. По этой строке

определяется физический адрес нужной

в данный момент таблицы страниц. Следующие

десять бит линейного адреса (биты 21-12)

содержат номер строки (дескриптора) из

этой таблицы страниц, т.е. эта часть

линейного адреса позволяет выбрать

нужный дескриптор страницы из таблицы

страниц. Выбранный дескриптор определяет

физический адрес страницы. Младшие 12

бит линейного адреса определяют смещение

от начала страницы. Для того чтобы

получить физический адрес нужно к

найденному физическому адресу страницы

добавить это смещение.

еальный

режим процессора Intel – однозадачная

среда, в данный момент времени в ней

может выполняться только одна, конкретная

задача. Все сегменты в этом режиме

доступны для любого процесса, поэтому

в многозадачном режиме процессы могут

мешать друг другу. Для решения этой

проблемы начиная с процессора i80268

был реализован защищенный режим.

Современный вид защищенный режим

приобрел в процессоре i80368

(применительно к 4-х гигабайтному

адресному пространству). Главной

особенностью защищенного режима является

то, что вся многозадачность реализована

аппаратно. Преимущества: возможность

для каждой задачи иметь свою систему

сегментов, сегменты могут быть защищены

от записи, можно указывать уровень

доступа, заложена возможность виртуальной

памяти. Организацию памяти в защищенном

режиме разделяют на 2е части: сегментация

и страничная организация. Сегментация

– это механизма разделения адресного

пространства процессора на отдельные

защищенные друг от друга кусочки

(сегменты). Механизм страничной

памяти позволяет разместить часть

оперативной памяти на диске. Это позволяет

обеспечить прикладные программы

оперативной виртуальной памятью, размер

которой больше размера физической

памяти, установленной в компьютере.

Программы, предназначенные для защищённого

режима, должны быть написаны особым

образом. Это означает, что реальный и

защищённый режим не совместимы. Разделение

адресного пространства на сегменты.

Итак, адресное пространство процесса

делится на части — сегменты, размер

которых определяется с учетом смыслового

значения содержащейся в них информации.

Отдельный сегмент может представлять

собой подпрограмму, массив данных и т.

п. (Еще раз прошу обратить внимание – в

реальном режиме размеры всех сегментов

одинаковые (64 Кбайта), а в защищенном

каждый сегмент имеет собственный

размер.) На этапе создания процесса во

время загрузки его образа в оперативную

память система создает в памяти локальную

таблицу дескрипторов–описателей

сегментов (LDT) процесса. Каждый

дескриптор описывает свой сегмент.

Кроме локальных таблиц дескрипторов

сегментов система создает одну глобальную

таблицу дескрипторов (GDT), где

хранятся дескрипторы сегментов, занятых

операционной системой. Доступ к глобальной

таблице имеют все выполняемые задачи.

Информация в дескрипторе, характеризующую

сегмент: базовый адрес сегмента, резмер

сегмента, тип сегмента, право доступа,

уровень привилегии. Процессы имеют

следующие привилегии: 0-ядро операционной

системы; 1 – программы обслуживающие

аппаратуру, драйвера, программы работающие

с портами ввода/вывода компьютера; 2 –

системы управления базами данных,

расширения операционной системы; 3-

прикладные программы, запускаемые

пользователем. Так же как и в случае

реального режима будет использоваться

двухкомпонентный логический адрес.

По-прежнему логический адрес формируется

при помощи сегментных регистров и

регистров, где хранится смещение. Однако

сегментные регистры содержат теперь

не сегментный адрес, а так называемый

селектор, часть которого (13 бит)

представляет собой индекс в дескрипторной

таблице, т.е. указывает на дескриптор,

в котором находится полная информация

о сегменте. Как это происходит показано

на рис. 24. .Иначе это преобразование

называется трансляция логического

адреса в линейный. Логический адрес

состоит из 16-битового селектора

сегмента и 32-битового смещения в этом

сегменте. Логический адрес преобразуется

в линейный адрес. Адрес сегмента берется

из таблицы глобальных дескрипторов

(GDT). Бит Т (13-й разряд) в селекторе сегмента

определяет, какая таблица (глобальная

или локальная) должна быть использована,

а собственно сам дескриптор определяется

на основании 13 младших разрядов селектора

сегмента. На основании известного

системе адреса таблицы дескрипторов

(определяется специальными регистрами)

и номера сегмента вычисляется адрес

дескриптора сегмента. Получив доступ

к дескриптору, анализируются его поля,

выполняется проверка возможности

выполнения заданной операции. Если

доступ разрешен, то из дескриптора

извлекается адрес этого сегмента и

вычисляется линейный адрес. Если доступ

невозможен, возникает прерывание. Для

нахождения линейного адреса к адресу

сегмента добавляется смещение, заданное

в исходном логическом адресе. В результате

проведенного преобразования мы получили

требуемый 32- разрядный линейный адрес.

Полученный линейный адрес является

виртуальным, т.е. не может быть

непосредственно отправлен на шину

адреса. Механизм страничнаой памяти.

Второй этап преобразования требуется,

потому что реальный компьютер не имеет,

как правило, установленных 4Гб памяти,

т.е. возникает необходимость перейти

от виртуального линейного адреса к

физическому. Полученный линейный

виртуальный адрес преобразуется в

искомый физический адрес. В процессе

страничной трансляции адресов полученный

линейный адрес разбивается на три части.

Старшие десять бит линейного адреса

являются индексом (номером) строки из

каталога таблиц. По этой строке

определяется физический адрес нужной

в данный момент таблицы страниц. Следующие

десять бит линейного адреса (биты 21-12)

содержат номер строки (дескриптора) из

этой таблицы страниц, т.е. эта часть

линейного адреса позволяет выбрать

нужный дескриптор страницы из таблицы

страниц. Выбранный дескриптор определяет

физический адрес страницы. Младшие 12

бит линейного адреса определяют смещение

от начала страницы. Для того чтобы

получить физический адрес нужно к

найденному физическому адресу страницы

добавить это смещение.