- •4.1 Классификация ис

- •4.2 Система условных обозначений отечественных ис

- •4.3 Основные характеристики и параметры цифровых ис

- •4.2 Статические входные и выходные параметры логических схем

- •4.3 Потребляемая мощность и ток цифровых схем

- •4.4 Динамические параметры лэ

- •4.5 Описания базовых логических элементы кмдп типа

- •4.6 Преимущества и недостатки кмдп схем

- •4.7 Типы корпусов интегральных схем

- •5 Аналоговые интегральные схемы

- •5.1 Основные определения. Классификация операционных усилителей

- •5. 2 Основная характеристика и параметры операционных усилителей

4.4 Динамические параметры лэ

характеризуют

быстродействие ИС. К наиболее употребляемым

параметрам логических схем относятся

времена задержки распространения при

включении

![]() и при выключении

и при выключении ![]() .

В настоящее время эти параметры должны

измеряться на уровне напряжений,

оговоренных в соответствующих ТУ.

.

В настоящее время эти параметры должны

измеряться на уровне напряжений,

оговоренных в соответствующих ТУ.

U(t)

U(t)

уровень отсчёта оговоренный в ТУ

Uвх1

Uвх1

t

Uвх0

Uвых1 уровень

отсчёта оговоренный в ТУ

Uвых1 уровень

отсчёта оговоренный в ТУ

t

Uвых0

Uвых0

Рисунок 4.6 - Измерение параметров и

Раньше для всех типов ЛЭ времена задержки распространения измерялись на уровне 0,5 от амплитуды сигнала.

Другим распространённым параметром, характеризующим быстродействие ЛЭ, является среднее время задержки распространения:

![]()

Часто о быстродействии ИС определённой серии судят по максимальной допустимой рабочей частоте (обычно указывается для Д-триггера).

Быстродействие ЛЭ микросхемы определяется его схемотехникой, технологией и зависит от емкости нагрузки, числа нагрузок n, температуры окружающей среды, напряжения источника питания.

Кратко рассмотрим зависимость быстродействия ЛЭ от ёмкости нагрузки и числа нагрузок, используя простейшую эквивалентную схему (рис. 4.7).

ЛЭ Uсс

ЛЭ Uсс

Uвых

Uвых

Iз

Iз

Iр Rн

экв.

Iр Rн

экв.

Сн

Сн

Рисунок 4.7.

Ёмкость нагрузки Сн состоит из ёмкости монтажных проводников См и суммарной входной ёмкости схем – нагрузок: Сн=См+Свх. Эквивалентное сопротивление Rн экв характеризует число подключенных к выходу ЛЭ схем – нагрузок.

При U1вых происходит заряд ёмкости, а при U0вых – её разряд. На эти процессы необходимо время, поэтому появляется дополнительная задержка переключения ЛЭ, находящихся в последовательной цепи. Для ускорения процессов заряда – разряда Сн необходимо увеличивать выходные токи схемы и естественно снижать саму ёмкость.

Однако, при увеличении выходных токов, как правило возрастает потребляемая мощность ИС. Часть токов будет протекать через нагрузки, поэтому быстродействие зависит от числа нагрузок.

Другая часть задержки переключения связана с переходными процессами, происходящими в самой схеме ЛЭ.

Для оценки степени конструктивно – технологического и схемотехнического совершенства ИС пользуются понятием работы (энергии) переключения:

![]()

Теоретический предел для работы переключения по разным оценкам составляет от 10-15 до 10-18 Дж, достигнутая же в настоящее время величина составляет порядка 10-14 Дж. Разница на порядок объясняется существующим уровнем технологии.

4.5 Описания базовых логических элементы кмдп типа

Среди цифровых ИС широкого назначения известны следующие схемотехнологические разновидности:

- эмиттерно-связанная логика (ЭСЛ);

- транзисторно-транзисторная логика (ТТЛ);

- ТТЛ с диодами Шоттки (ТТЛШ);

- комплементарные схемы со структурой металл-диэлектрик-полупроводник (КМДП).

В настоящее время по масштабам и широте использования при изготовлении цифровых ИМС всех уровней сложности, начиная со схем малых и средних степеней интеграции и до сверхбольших интегральных схем (СБИС) на первом месте по применению стоит технология КМДП. Базовыми элементами для построения сложных функциональных узлов в этой технологии считаются инвертор и двунаправленный тактируемый ключ. Рассмотрим электрическую схему инвертора КМДП, которая изображена на рисунке 4.8. Основу этой схемы составляют два встречно включенных МДП-транзистора: VT1 имеет индуцированный канал p-типа, а VT2 – канал n-типа. Затворы этих транзисторов соединены между собой и являются общим входом. Поскольку транзисторы p-типа открываются при отрицательном напряжении смещения затвора относительно истока, а транзисторы n-типа – соответственно при положительном напряжении на затворе, для получения положительной логики исток транзистора с каналом n-типа подключен к минусу источника питания (общий провод), а исток с каналом p-типа – к его плюсу. Общая точка стоков обоих транзисторов служит выходом инвертора. Таким образом, транзисторы в базовой схеме по отношению к выводам питания соединены между собой последовательно, а по отношению к сигналу – параллельно. Этим объясняются многие из особенностей КМДП-схем.

Рисунок 4.8 - Электрическая схема инвертора КМДП

Когда

на входе инвертора действует сигнал

низкого уровня

![]() ,

можно считать, что затвор транзистора

VT2

(n-типа)

соединен с истоком, канал отсутствует

и транзистор заперт. В это время затвор

транзистора VT1

(p-типа)

имеет по отношению к своему стоку

отрицательный потенциал и транзистор

открыт. На выходе, следовательно,

существует напряжение высокого уровня

,

можно считать, что затвор транзистора

VT2

(n-типа)

соединен с истоком, канал отсутствует

и транзистор заперт. В это время затвор

транзистора VT1

(p-типа)

имеет по отношению к своему стоку

отрицательный потенциал и транзистор

открыт. На выходе, следовательно,

существует напряжение высокого уровня

![]() .

При высоком входном напряжении –

наоборот. Схема, таким образом, инвертирует

входные сигналы.

.

При высоком входном напряжении –

наоборот. Схема, таким образом, инвертирует

входные сигналы.

Поскольку

в каждом состоянии один из транзисторов

заперт, а входное сопротивление следующего

каскада очень велико, сквозной ток в

цепи питания отсутствует и статическая

мощность, потребляемая от источника

питания, ничтожно мала, определяется

только токами утечки. Токи утечки

транзисторов не превышают долей

микроампера при комнатной температуре,

и поэтому выходные уровни

≈

![]() ,

а

,

а

![]() ≈

0 и сигнал на выходе практически равен

.

≈

0 и сигнал на выходе практически равен

.

Входное

сопротивление транзисторов, используемых

в схеме инвертора, достигает значений

до 10![]() Ом. Толщина подзатворного диэлектрика

имеет величину порядка 50 – 100 нм, и его

электрическая прочность не превышает

150 – 200 В. По этой причине очень велика

опасность пробоя диэлектрика статическим

электричеством. Для защиты транзисторов

от действия этого фактора каждый вход

микросхемы КМДП снабжается

Ом. Толщина подзатворного диэлектрика

имеет величину порядка 50 – 100 нм, и его

электрическая прочность не превышает

150 – 200 В. По этой причине очень велика

опасность пробоя диэлектрика статическим

электричеством. Для защиты транзисторов

от действия этого фактора каждый вход

микросхемы КМДП снабжается

![]() диодно-резисторной

охранной цепью, на рисунке – VD1,VD2,

VD3

и R1.

Данная схема ограничивает напряжение

на входе инвертора в пределах от - 0,7 В

до

диодно-резисторной

охранной цепью, на рисунке – VD1,VD2,

VD3

и R1.

Данная схема ограничивает напряжение

на входе инвертора в пределах от - 0,7 В

до

![]() + 0,7 В. Наличие этих диодов накладывает

дополнительные ограничения на режим

работы ЛЭ. Всегда должно выполняться

неравенство

+ 0,7 В. Наличие этих диодов накладывает

дополнительные ограничения на режим

работы ЛЭ. Всегда должно выполняться

неравенство

|

![]() |

<

|

<

В противном случае диоды входного ограничителя и выходной цепи могут открываться, замыкая цепь питания ЛЭ. Поэтому напряжение питания на КМДП - схемы должно всегда подаваться до включения и сниматься после отключения входного сигнала.

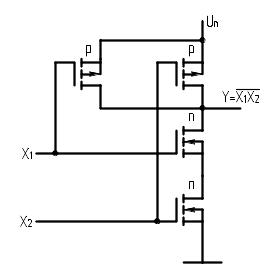

На основе инверторов КМДП реализуются многие более сложные схемы. Для построения логических элементов вида И-НЕ (И) либо ИЛИ-НЕ (ИЛИ) транзисторы одного типа соединяются параллельно, а другого – последовательно. Особенностью логических элементов также является наличие двух ярусов транзисторов относительно выходного вывода. Функция, выполняемая всей схемой, определяется транзисторами нижнего яруса. Для реализации операции И-НЕ в положительной логике транзисторы с n-каналом включаются последовательно друг с другом, с р-каналом – параллельно, а для операции ИЛИ-НЕ – наоборот.

На рисунке 4.9 изображена схема логического элемента 2И-НЕ (один ЛЭ микросхемы К176ЛА7). На ней защитные диодно-резисторные цепочки не показаны.

В

этой схеме выходное напряжение низкого

уровня

обеспечивается сигналами высокого

уровня

![]() на обоих входах. При этом оба n-канальных

транзистора будут открыты, а р-канальные

– заперты. Если хотя бы на одном входе

окажется сигнал низкого уровня

один из параллельно включенных

транзисторов откроется, а спаренный с

ним n-канальный

транзистор запрется и на выходе элемента

образуется высокий уровень напряжения

на обоих входах. При этом оба n-канальных

транзистора будут открыты, а р-канальные

– заперты. Если хотя бы на одном входе

окажется сигнал низкого уровня

один из параллельно включенных

транзисторов откроется, а спаренный с

ним n-канальный

транзистор запрется и на выходе элемента

образуется высокий уровень напряжения

![]() .

.

Рисунок 4.9 - Упрощенная схема КМДП-элемента 2И-НЕ

Микросхемы серии К176, выполненные по КМДП-технологии, имеют заметное преимущество перед ИМС серии К155 (ТТЛ) по потребляемой статической мощности, помехоустойчивости и величине входных токов. Однако по быстродействию картина прямо противоположная: среднее время задержки у микросхемы К176ЛА7 составляет 200 нс, а у микросхемы К155ЛА3 – всего 19 нс. Кроме этого, микросхемы серии К155 имеют большую нагрузочную способность по величине тока. По температурному диапазону применения серия КМ155 превосходит серию К176, но это связано только с тем, что первая из них выполняется в керамическом корпусе, а вторая – в пластмассовом.