- •1. Понятие о микропроцессорах (мп). Замена устройств с жесткой логикой на мп управление.

- •2. Выбор мп комплекта (мпк. Основные критерии выбора.

- •3. Основные параметры мп и оэвм.

- •4. Микро-эвм и оэвм на основе мп. Основные семейства современных оэвм.

- •5. Классификация оэвм и мп. Признаки классификации оэвм.

- •6. Архитектура мп систем (мпс). Основные составляющие мпс.

- •7. Однокристальные, одноплатные и многоплатные микро-эвм. Основные параметры и особенности.

- •8. Микро-эвм и контроллеры. Основные отличия и сходство.

- •9. Общий принцип обработки информации в мпс. Временные соотношения при обмене информацией.

- •10. Cхемный принцип управления мп.

- •11. Микропрограммный принцип управления мп.

- •12. Типовая структура устройства управления, основанного на микропрограммном принципе.

- •13. Структура мп, основанного на схемном принципе управления (на примере мп серии к580).

- •14. Основные составляющие внутренней структуры оэвм семейства mcs-51.

- •15. Временная диаграмма работы оэвм.

- •16. Организация стека в мпс.

- •17. Режим прямого доступа к памяти (пдп).

- •18. Система прерывания в микро-эвм.

- •19. Форматы данных и команд в мпс.

- •20. Способы адресации.

- •21. Система команд мп и оэвм. Структура команды, Информация, необходимая для записи программ.

- •22. Система команд мп и оэвм Группы команд.

- •23. Программирование мп и оэвм. Этапы составления программы.

- •24. Распределение ресурсов при составлении программы. Оценка времени выполнения программы.

- •25. Однокристальные микро - эвм (оэвм) - новые изделия мп техники. Особенности, основные характеристики (на примере семейства mcs-51).

- •26. Оэвм семейства mcs-51. Структура, характеристики, назначение выводов.

- •27. Оэвм семейства mcs-51. Особенности построения блока памяти программ.

- •28. Оэвм семейства mcs-51. Особенности построения блока памяти данных.

- •29. Оэвм семейства mcs-51. Организация ввода / вывода. Назначение портов оэвм в различных конфигурациях системы.

- •30. Синхронизация оэвм семейства mcs-51. Временная диаграмма.

- •31. Узел таймеров оэвм семейства mcs-51.

- •32. Система прерываний оэвм семейства mcs-51.

- •33. Регистр состояний оэвм семейства mcs-5.

- •34. Система команд оэвм семейства mcs-51. Информация, необходимая для составления программ.

- •35. Группы команд оэвм семейства mcs-51. Их краткая характеристика.

- •36. Способы адресации в командах оэвм семейства mcs-51

- •37. Страничная адресация в командах оэвм семейства mcs-51 (на примере команд переходов и вызова подпрограмм).

- •38. Построение мпс на основе оэвм семейства mcs-51.

- •39. Примеры программирования оэвм семейства mcs-51.

- •40. Запоминающие устройства мпс. Основные параметры и классификация.

- •41. Оперативные запоминающие устройства мпс (озу). Классификация и основные параметры.

- •42. Структура и работа бис озу статистического типа.

- •43. Постоянные запоминающие устройства (пзу). Виды пзу и их основные характеристики.

- •44. Перепрограммируемые пзу (ппзу). Принципы запоминания и стирания информации.

- •45. Интерфейсные схемы мпс (на примере мпк к580).

- •46. Бис усапп кр580ви53. Принцип действия, порядок программирования.

- •47. Бис ппи кр580вв55а. Основные режимы работы. Порядок программирования.

- •48. Основные особенности и характеристики ацп и цап. Их подключение к оэвм.

- •49. Шинные формирователи, супервизоры, регистры и другие вспомогательные элементы мпс.

- •50. Программное обеспечение мпс (по мпс). Классификация, структура.

- •51. Иерархия уровней по мпс. Характеристики отдельных модулей.

- •52. Средства отладки по мпс. Характеристики, требования к отдельным составляющим.

- •53. Языки программирования мпс. Иерархия уровней.

- •54. Средства диагностики мпс.

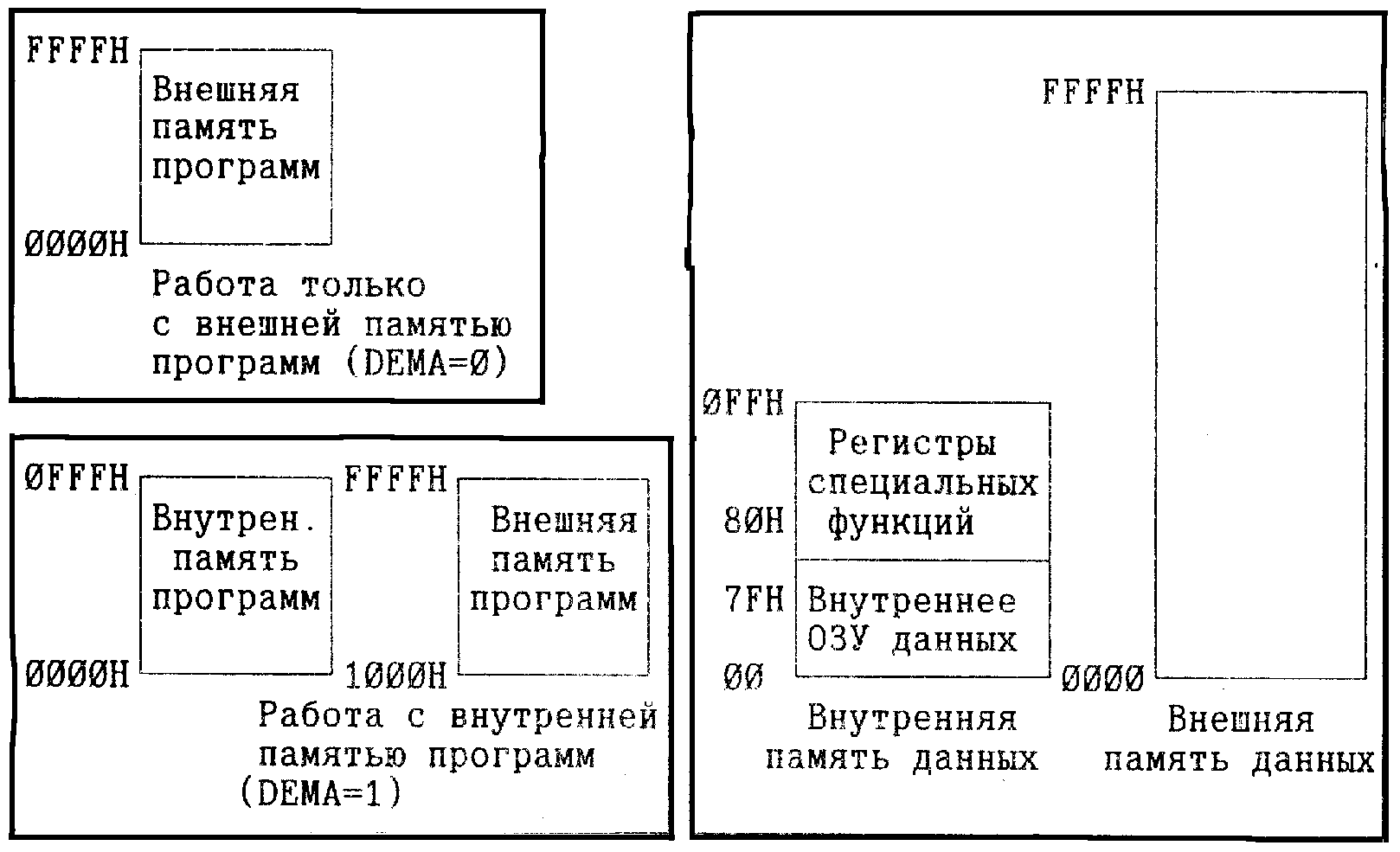

27. Оэвм семейства mcs-51. Особенности построения блока памяти программ.

Все ОЭВМ семейства МCS-51 имеют несколько адресных пространств, функционально и логически разделенных за счет разницы в механизмах адресации и сигналах управления записью и чтением:

память команд (ПК),

внутренняя память данных (ПД),

внешняя память данных (ПД).

Память команд – имеет 16-битовую адресную шину, её элементы адресуются с использованием счетчика команд (РС) или инструкциями, которые вырабатывают 16-разрядные адреса. Память команд доступна только по чтению. Она имеет байтовую организацию и общий объем до 64Кбайт. Ряд ОЭВМ содержат расположенную на кристалле внутреннюю память команд емкостью от 4Кбайт до 32 Кбайт, которая может быть расширена до 64 Кбайт за счет подключения микросхем внешней память команд.

С игналом,

стробирующим выборку и ввод байта из

внешней памяти команд в ОЭВМ является

сигнал PME (РSEN). Для ОМЭВМ, содержащих

внутреннюю память команд, сигнал РSEN

формируется только в том случае, если

адрес в счетчике команд превосходит

максимальный адрес внутренний памяти

команд, например, 0FFFH для 4 Кбайтной

версии. Для ОЭВМ, не имеющих внутренней

памяти команд, РSEN формируется при любом

обращении к памяти команд.

игналом,

стробирующим выборку и ввод байта из

внешней памяти команд в ОЭВМ является

сигнал PME (РSEN). Для ОМЭВМ, содержащих

внутреннюю память команд, сигнал РSEN

формируется только в том случае, если

адрес в счетчике команд превосходит

максимальный адрес внутренний памяти

команд, например, 0FFFH для 4 Кбайтной

версии. Для ОЭВМ, не имеющих внутренней

памяти команд, РSEN формируется при любом

обращении к памяти команд.

Рис 2.18. Организация памяти ОЭВМ

28. Оэвм семейства mcs-51. Особенности построения блока памяти данных.

Все ОЭВМ семейства МCS-51 имеют несколько адресных пространств, функционально и логически разделенных за счет разницы в механизмах адресации и сигналах управления записью и чтением:

память команд (ПК),

внутренняя память данных (ПД),

внешняя память данных (ПД).

Структура адресного пространства ОМЭВМ показана на рисунке 2.18.

Р ис 2.18. Организация памяти ОЭВМ

Внутренняя память данных – состоит из 2-х областей:

128 байт оперативной памяти (ОЗУ) с адресами 0-7FH

область регистров специальных функций (SFR), занимающая адреса 80H-FFH.

Распределение пространства внутренней памяти данных показано на рис. 2.19

Младшие 32 байта внутреннего ОЗУ данных сгруппированы в 4 банка по 8 регистров в каждом (БАНК 0 – БАНК 3 на рис. 2.4). Команды программы могут обращаться к регистрам, используя их имена R0 – R7. Два бита PSW (указатели банка рабочих регистров RS0 и RS1) определяют, с регистрами какого банка проводятся манипуляции (прямая адресация). Следующие после банков регистров внутреннего ОЗУ данных 16 байт (адреса 20H-2FH) образуют область ячеек, к которым возможна побитовая адресация.

О бращение

к внутреннему ОЗУ данных всегда

осуществляется с использованием

8-разрядного адреса.

бращение

к внутреннему ОЗУ данных всегда

осуществляется с использованием

8-разрядного адреса.

Рис 2.19. Распределение памяти данных

Внешняя память данных – формируется дополнительными микросхемами памяти и может иметь емкость до 64 Кбайт. Обращение к ячейкам внешней памяти данных осуществляется только с использованием косвенной адресации по регистрам R0 и R1 активного банка регистров внутреннего ОЗУ (команды типа MOV @Ri) или по регистру специальных функций DPTR (команды типа MOVХ @DPTR). При обращении к внешней памяти данных адрес выводится через порт Р0 (младший байт) и порт Р2 (старший байт) ОЭВМ. Обмен байтом данных производится через порт Р0 ОЭВМ. Считывание данных из внешнего ОЗУ в ОЭВМ производится с помощью выходного сигнала ОЭВМ RD, а запись - сигнала WR.