- •1. Методы передачи информации в мпс: асинхронный, синхронный, асинхронно-синхронный. Общая характеристика, сравнение.

- •2. Асинхронные методы передачи информации. Временные диаграммы.

- •3. Синхронные методы передачи информации. Временные диаграммы.

- •4. Асинхронно-синхронный методы передачи информации. Временные диаграммы.

- •5. Основные принципы организации микропроцессорных систем. Синхронизация, шины, понятие о пдп, прерываниях.

- •6. Архитектура фон Неймана и архитектуры современных мпс.

- •7. Основные циклы работы процессора на любом примере: чтения, записи.

- •8. Методы ввода-вывода: опрос, прерывание, пдп. Общая характеристика.

- •9. Пдп, методы пдп.

- •17. Особенности разработки по в системах с прерываниями.

- •20. Динамическая память. Принципы организации, режимы работы.

- •10. Стандартный контроллер пдп и его включение в мпс.

- •11. Организация пдп в ibm pc. Принципы работы.

- •12. Прерывания. Организация прерываний в микропроцессорах. Векторные прерывания.

- •18. Микросхемы памяти. Общая классификация.

- •19. Синхронные и асинхронные зу. Временные диаграммы.

- •13. Стандартный контроллер прерываний, его включение в мпс.

- •14. Организация прерывания в ibm pc. Принципы работы.

- •15. Реализация прерываний по уровню и по фронту. Сравнительная характеристика.

- •16. Прохождение прерывания от клавиатуры в ibm pc.

- •25. Принципы работы динамической памяти в ibm pc: sdram, ddr sdram. Временные диаграммы.

- •26. Организация памяти в мпс. Классификация, общая характеристика.

- •27. Методы повышения быстродействия одноуровневой динамической памяти.

- •28. Организация шин в мпс: общая шина, разделенная шина, смешанный ввод-вывод, смешанная структура шин. Общая характеристика.

- •29. Общая шина. Цикл чтения.

- •30. Общая шина. Цикл записи.

- •31. Общая шина. Цикл прерывания.

- •32. Основные характеристики pci.

- •33. Pci. Цикл чтения.

- •34. Pci. Цикл записи.

- •35. Периферийные устройства: Таймеры, порты, ацп, цап.

- •36. Микроконтроллеры и мпк бис. Общая характеристика, области применения.

- •37. Принципы цифровой обработки сигналов. Основные задачи в обработке сигналов.

- •38. Основные принципы организации dsp.

- •Методы передачи информации в мпс: асинхронный, синхронный, асинхронно-синхронный. Общая характеристика, сравнение.

- •42. Шина usb

- •44. Интерфейс rs-232.

- •Чтение памяти (0110) и запись в память (0111)

- •Чтение конфигурации (1010) и запись конфигурационных данных (1011)

- •Множественное чтение памяти (1100)

- •Спецификации scsi

- •Другие карты scsi

- •Характеристики scsi

- •Параметры конфигурирования scsi устройств

- •Хост-адаптер

- •Scsi устройства

- •Контроллеры

- •47. Шина ieee-1394

- •Технические характеристики:

- •2. Характеристики задатчиков на шине

- •2.1. Центральный процессор

- •2.2. Контроллер пдп

- •3.3. Структура прерываний

- •3.4. Перестановщик байтов

20. Динамическая память. Принципы организации, режимы работы.

В качестве элемента памяти используется микроконденсатор в интегральном исполнении, размеры которого значительно меньше D-триггера статической памяти. По этой причине, при одинаковых размерах кристалла, информационная емкость DRAM выше, чем у SRAM. Количество адресных входов и габариты должны увеличиться.Чтобы не допустить этого, адресные линии внутри микросхемы разбиваются на две группы, например старшая и младшая половина. Две одноименные k-линии каждой группы подключаются к двум выходам внутреннего k-го демультиплексора "1 в 2", а его вход соединяется с k-ым адресным входом микросхемы. Количество адресных входов, при этом уменьшается в два раза, но зато передача адреса в микросхему должна производиться, во-первых в два приема, что несколько уменьшает быстродействие, и во-вторых потребуется дополнительный внешний мультиплексор адреса.В процессе хранения бита конденсатор разряжается. Чтобы этого не допустить заряд необходимо поддерживать.

Все DRAM имеют несколько режимов работы – чтения/записи страничный режим чтения/записи режим регенерации.

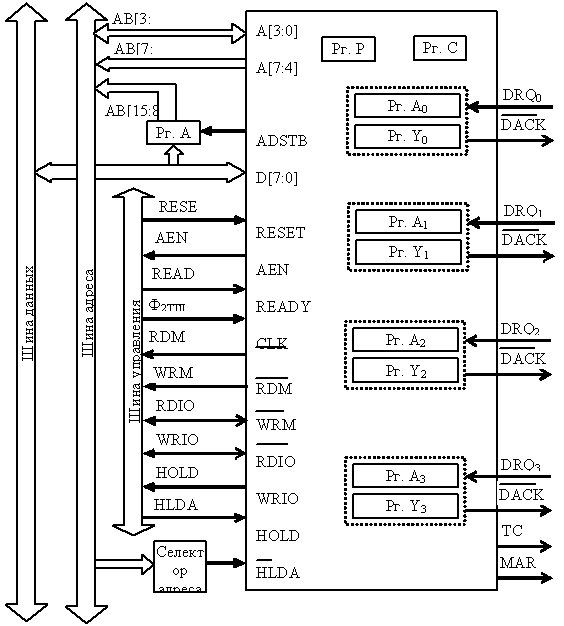

10. Стандартный контроллер пдп и его включение в мпс.

Если в МПС используется несколько ВУ, снабженных каналом ПДП, то целесообразно использовать специальный контроллер ПДП, который обеспечивает программирование каналов ПДП, подключение их к системной шине и дисциплину обслуживания.

Т иповое

включение КПДП в МПС

иповое

включение КПДП в МПС

Контроллер прямого доступа в память К580ВТ57

Микросхема К580ВТ57 предназначена для управления передачей информации между ВУ о ЗУ в режиме ПДП. Основное назначение контроллера - формирование последовательности адресов и управляющих сигналов.

Контроллер ПДП имеет четыре независимых канала обмена. Блок управления каждого канала включает два 16-разрядных регистра : регистр начального адреса РА и регистр управления РУ, причем РУ[13:0] хранит длину передаваемого массива (количество передаваемых байт), а РУ[15:14] - режим работы канала.

Контроллер прямого доступа в память

Контроллер включает в себя, помимо четырех каналов ПДП, схему управления, обеспечивающую связь с системной шиной, разрешение конфликтных ситуаций в соответствии с заданной системой приоритетов и управление работой контроллера в различных режимах.

11. Организация пдп в ibm pc. Принципы работы.

В современных машинах используются дополнительные контроллеры ПДП один из которых 16-ти разрядный но также есть и 8-ми разрядные.

П ри

программировании контроллера указываются

адреса

приоритеты

регистр страниц ПДП.

ри

программировании контроллера указываются

адреса

приоритеты

регистр страниц ПДП.

Организация ПДП в IBM PC

Высокопроизводительный 32-разрядный контроллер ПДП 82380

Контроллер 82380 выполнен в 132-выводном корпусе типа PGA и представляет собой высокопроизводительное 32-разрядное устройство, обеспечивающее прямой доступ к памяти и спроектированное специально для использования в системах на базе микропроцессора 80386. Контроллер 82380 является первым коммерческим устройством, в котором реализованы функции управления ПДП по восьми независимым программируемым каналам. Контроллер 82380 повышает общую пропускную способность шины микропроцессора 80386. Применение 32-разрядного интерфейса контроллера обеспечивает эффективную передачу данных и повышает скорость обслуживания системных устройств ввода-вывода в 5 — 10 раз по сравнению с известными схемотехническими решениями. Эти особенности наиболее важны в системах, требующих быстродействующей компьютерной техники, таких как многозадачные учрежденческие рабочие станции, промышленная связь и автоматизация, САПР, гибкие производственные системы и системы искусственного интеллекта. Специализированная ориентация контроллера 82380 на особенности интерфейса микропроцессора 80386 предельно минимизирует объем соответствующих логических схем.

Контроллер 82380 называют также интегрированным системным периферийным устройством, поскольку он выполняет ряд типовых для вычислительных систем функций, обычно реализуемых на отдельных компонентах БИС и СБИС. В состав таких средств входят: логические схемы системного сброса; 20-уровневый программируемый контроллер прерываний (функциональное расширение программируемого контроллера прерываний 82С59А фирмы Intel); четыре 16-разрядных программируемых таймера; программируемый генератор с состояниями ожидания; контроллер регенерации динамического ОЗУ; схемы управления и арбитража внутренней шины.

Структурная схема контроллера 82380 показана на Error: Reference source not found. Для каждого из восьми независимых каналов передачи данных в контроллере 82380 имеется вспомогательная регистровая память, поддерживающая обмен данными произвольной разрядности. Это позволяет исключить дополнительные внешние цепи для. выполнения действий по выравниванию данных на определенную границу. В результате контроллер обеспечивает передачу данных между устройствами с разными размерами тракта данных по одному каналу.