- •1. Системи числення. Переведення чисел із однієї системи числення в іншу.

- •2. Прямий, обернений та додатковий коди. Виконання операції складання (віднімання) в двійковій системі числення.

- •3. Логічні операції та функції. Способи задання функцій. Функціонально повні системи логічних операцій

- •4. Форми запису логічних функцій. Диз'юнктивна (кон'юктивна) нормальна форма

- •5. Мінімізація логічних функцій методом карт Карно. Приклади

- •6. Мінімізація неповністю визначених функцій. Приклад.

- •7. Класифікація цифрових схем та динамічні параметри цифрових елементів

- •Динамічні параметри цифрових мікросхем

- •8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

- •9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

- •10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

- •11. Призначення, способи завдання та побудови мультиплексорів.

- •12. Призначення, способи завдання та побудови демультиплексорів.

- •13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

- •16. Призначення, класифікація та характеристики регістрів. Паралельні однофазні та парафазні регістри.

- •Класифікація регістрів

- •Операції в регістрах

- •17. Послідовні регістри. Схеми та робота регістрів зсуву вліво, вправо та реверсивних.

- •18. Призначення, класифікація та характеристики лічильників. Схема двійкового підсумовуючого лічильника із послідовним перенесенням.

- •19. Призначення. Класифікація та характеристики лічильників. Схема двійкового віднімаючого лічильника з послідовним перенесенням.

- •20. Схема кільцевого лічильника.

- •21. Способи та схеми побудови типових недвійкових лічильників та їх характеристики.

14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

D-тригери також називають тригерами затримки (від англ. Delay).

D-тригер синхронний. D-тригер (D от англ. delay — затримка або від data - дані) - запам'ятовує стан входу і видає його на вихід. D-тригери мають, як мінімум, два входи: інформаційний D і синхронізації С. Після приходу активного фронту імпульсу синхронізації на вхід С D-тригер відкривається. Збереження інформації в D-тригерах відбувається після спаду імпульсу синхронізації С. Так як інформація на виході залишається незмінною до приходу чергового імпульсу синхронізації, D-тригер називають також тригером із запам'ятовуванням інформації або тригером-клямкою. Розмірковуючи чисто теоретично, парафазного (двофазний) D-тригер можна утворити з будь-яких RS-або JK-тригерів, якщо на їх входи одночасно подавати взаємно інверсні сигнали.

D-тригер в основному використовується для реалізації засувки. Так, наприклад, для зняття 32 біт інформації з паралельної шини, беруть 32 D-тригера і об'єднують їх входи синхронізації для управління записом інформації в засувку, а 32 D входу під'єднують до шини.

У одноступінчатих D-тригерах під час прозорості всі зміни інформації на вході D передаються на вихід Q. Там, де це небажано, потрібно застосовувати двоступінчасті (двотактні, Master-Slave, MS) D-тригери.

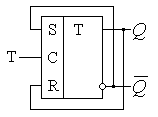

Приклад

умовного графічного позначення D-тригера

з динамічним синхронним входом С і з

додатковими асинхронними інверсними

входами S і R

Приклад

умовного графічного позначення D-тригера

з динамічним синхронним входом С і з

додатковими асинхронними інверсними

входами S і R

Умовне

графічне позначення D-тригера зі статичним

входом синхронізації С

Умовне

графічне позначення D-тригера зі статичним

входом синхронізації С

Рис. 5.7. Структурна схема синхронного D-тригера на елементах І-НЕ

![]()

Рис. 3.8. Таблиця управління (а) і часові діаграми (б) D - тригера

D-тригер двоступінчастий. У одноступенчатом тригері мається одна ступінь запам'ятовування інформації, а в двохступінчастом - дві такі щаблі. Спочатку інформація записується у перший ступінь, а потім переписується у другу і з'являється на виході. Двоступінчастий тригер позначають ТТ. Двоступінчастий D - тригер називають тригером з динамічним управлінням. Загальна схема двоступінчастого тригера.

15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

Т-тригер (від англ. Toggle - перемикач) часто називають рахунковим тригером, так як він є найпростішим лічильником до 2. Асинхронний Т-тригер не має входу дозволу рахунку - Т і перемикається по кожному тактовому імпульсу на вході С. Синхронний Т-тригер, при одиниці на вході Т, по кожнім такті на вході С змінює своє логічне стан на протилежне, і не змінює вихідний стан при нулі на вході T.

Т-тригер часто застосовують для пониження частоти в 2 рази, при цьому на Т вхід подають одиницю, а на С - сигнал з частотою, яка буде поділена на 2.

Умовне

графічне позначення синхронного

T-тригера з динамічним входом синхронізації

С на схемах.

Умовне

графічне позначення синхронного

T-тригера з динамічним входом синхронізації

С на схемах.

Рис. 5.8. Діаграми вхідного і вихідного потенціалів T-тригера.

Рис. 5.9. Синтез Т-тригера на базі синхронного RS-тригера та D-тригера.

JK-тригер працює так само як RS-тригер, з одним лише винятком: при подачі логічної одиниці на обидва входи J і K стан виходу тригера змінюється на протилежне. Вхід J (від англ. Jump - стрибок) аналогічний S, вхід K (від англ. Kill - вбити) аналогічний входу R. JK-тригер на відміну від RS-тригера не має заборонених станів на основних входах, проте це ніяк не допомагає при порушенні правил розробки логічних схем. На практиці застосовуються тільки синхронні JK-тригери. На базі JK-тригера можливо побудувати D-тригер або Т-тригер.

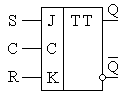

Умовне

графічне позначення JK-тригера зі

статичним входом С

Умовне

графічне позначення JK-тригера зі

статичним входом С

Алгоритм функціонування JK-тригера можна представити формулою

![]()

Карта

Карно JK-тригера для Q (t +1)

Карта

Карно JK-тригера для Q (t +1)

Рис. 5.12. Реалізація тригерів різних типів на базі JK-тригера.