- •1. Системи числення. Переведення чисел із однієї системи числення в іншу.

- •2. Прямий, обернений та додатковий коди. Виконання операції складання (віднімання) в двійковій системі числення.

- •3. Логічні операції та функції. Способи задання функцій. Функціонально повні системи логічних операцій

- •4. Форми запису логічних функцій. Диз'юнктивна (кон'юктивна) нормальна форма

- •5. Мінімізація логічних функцій методом карт Карно. Приклади

- •6. Мінімізація неповністю визначених функцій. Приклад.

- •7. Класифікація цифрових схем та динамічні параметри цифрових елементів

- •Динамічні параметри цифрових мікросхем

- •8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

- •9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

- •10. Призначення, способи завдання та побудови шифраторів. Пріоритетні шифратори.

- •11. Призначення, способи завдання та побудови мультиплексорів.

- •12. Призначення, способи завдання та побудови демультиплексорів.

- •13. Асинхронні та синхронні r-s тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •14. Синхронні d-тригери. Способи завдання, принципові схеми та часові діаграми їх роботи.

- •15. Способи завдання, принципові схеми та часові діаграми роботи j-к та т- тригерів.

- •16. Призначення, класифікація та характеристики регістрів. Паралельні однофазні та парафазні регістри.

- •Класифікація регістрів

- •Операції в регістрах

- •17. Послідовні регістри. Схеми та робота регістрів зсуву вліво, вправо та реверсивних.

- •18. Призначення, класифікація та характеристики лічильників. Схема двійкового підсумовуючого лічильника із послідовним перенесенням.

- •19. Призначення. Класифікація та характеристики лічильників. Схема двійкового віднімаючого лічильника з послідовним перенесенням.

- •20. Схема кільцевого лічильника.

- •21. Способи та схеми побудови типових недвійкових лічильників та їх характеристики.

Динамічні параметри цифрових мікросхем

Рис. 2.2 Динамічна характеристика інвертуючої мікросхеми

Основними параметрами динамічних цифрових мікросхем є:

час переходу з стану логічного нуля в стан логічної одиниці –

;

;час переходу з стану логічної одиниці в стан логічного нуля –

;

;час затримки вмикання –

;

;час затримки вимикання –

;

;час затримки поширення при вмиканні – ;

час затримки поширення при вимиканні –

;

;середній час затримки поширення –

;

;тривалість імпульсу –

;

;динамічна завадостійкість;

динамічна потужність;

імпульсна завадостійкість;

робоча частота перемикання.

8. Методика синтезу комбінаційних вузлів з одним виходом у різних базисах. Навести приклад.

Мультиплексор може бути використаний для синтезу будь-якого логічного пристрою. При цьому може бути досягнуто значне зниження числа використовуваних у схемі елементів.

Правила синтезу пристроїв на мультиплексор

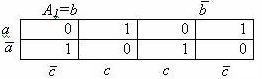

1. Побудувати карту Карно вихідний функції (по змінним функціям)

2. Вибрати порядок мультиплексора, який буде використовуватися в схемі.

3. Побудувати маскирующую матрицю, яка відповідає порядку вибраного мультиплексора.

4. Накласти маскирующую матрицю на карту Карно.

5. Мінімізувати функцію в кожній області маскирующей матриці окремо.

6. Результат мінімізації записується по тими змінним, які не подаються на адресні входи мультиплексора.

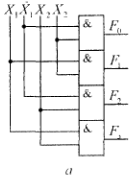

7. За результатами мінімізації будується схема, яка може містити і логічний елемент.

Детальніше розглянемо на прикладах:

![]()

с

с

Функція трьох змінних на мультиплексор другого порядку.

9. Призначення, класифікація, способи завдання та схеми побудови дешифратора.

Дешифра́тор

або деко́дер

(англ.

decoder) —

логічний пристрій, який перетворює код

числа, що поступило на вхід, в сигнал на

одному з його виходів. Якщо число

представлено у вигляді

![]() двійкових

розрядів,

то дешифратор повинен мати

двійкових

розрядів,

то дешифратор повинен мати

![]() виходів.

Дешифратор довільної складності може

бути складено з трьох базових логічних

елементів: кон'юнкції,

диз'юнкції

та заперечення.

виходів.

Дешифратор довільної складності може

бути складено з трьох базових логічних

елементів: кон'юнкції,

диз'юнкції

та заперечення.

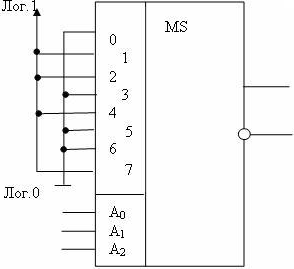

Приклад схеми дешифратора 3 на 8

У комп'ютерах дешифратори використовують для виконання таких операцій:

• дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір необхідної мікропрограми;

• перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам'яті в процесі запису або читання інформації;

• забезпечення візуалізації на зовнішніх пристроях;

• реалізації логічних операцій і побудови мультиплексора і демультиплексор.

Дешифратори класифікують за такими ознаками:

• способу структурної організації - одноступінчасті (лінійні) і багатоступінчасті. в тому числі пірамідальні і прямокутні (матричні);

• форматом вхідного коду - двійкові, двійково-десяткові;

• розрядності дешіфріруемого коду - 2. 3 n;

• формі подачі вхідного коду - з однофазними і парафазного входами;

• кількістю виходів - повні і неповні дешифратори;

• увазі вхідних стробирующих сигналів - у прямому чи інверсному значеннях;

• типом використовуваних логічних елементів - І, НЕ, АБО, І-НЕ, АБО-НЕ і т. д.

За принципом дії розрізняють такі види дешифраторів: послідовні, паралельні, паралельно-послідовні.

Рис. 4.3. Схеми лінійних дешифраторів на елементах І: а - з парафазними входами; б - з однофазними входами і стробуванням

Рис. 4.4. Схема лінійних дешифраторів на елементах АБО: а - С парафазними входами; б - з однофазними входами і стробуванням

Рис. 4.6. Схема прямокутного дешифратора

Рис. 4.8. Каскадування дешифраторів