- •В схеми «і» «або» на діодно резистивних ланках

- •2. Транзисторний ключ з спільнимемітером

- •Двокаскадна др. Логіка

- •4) Підвищення швидкодії транзисторна ключа за рахунок збільшення струму бази при включенні і зміни її напрямку на зворотній при виключені

- •5)Схема з трьома станами

- •6)Транзисторний ключ з нелінійним зворотним зв’язком

- •7) Схемы транзисторных ключей

- •11) Основна базова схема інжекційно інтегральної логіки

- •12) Ключ на мдп транзисторі. З мдп транзистором замість р(рез) стокового

- •15) Основна базова схема другого типу на мдп транзисторах

- •2. Його позитиви: простота.

- •3. Його недоліки: заборонені стани.

- •17) Реалізація рс тригера на елементах або нє

- •18 Реалізаціярстригера на елементах і нє

- •19. Т тригер(нічийний )

- •20) Д тригер

- •22. Двотактний регістр

- •25. Зсув інформації в регістрах в ліво

- •26. Зсув інформації в регістрах в право

- •27. Зсув інформації в регістрах Вліво вправо.

- •29) Лічильник з наскрізним переносом

- •31) За способом організації переносу (позички) між розрядами лічильники поділяють на такі типи:

- •32. Двійково-десяткові лічильники

- •33) Двохходовий одно розрядний суматор комбінаційного типу напівсуматор

- •34) Трьохходовий одно розрядний суматор комбінаційного типу повний суматор

- •35. Однорозрядні суматори накопичуючого типу

- •36. Послідовний багаторозрядний суматор

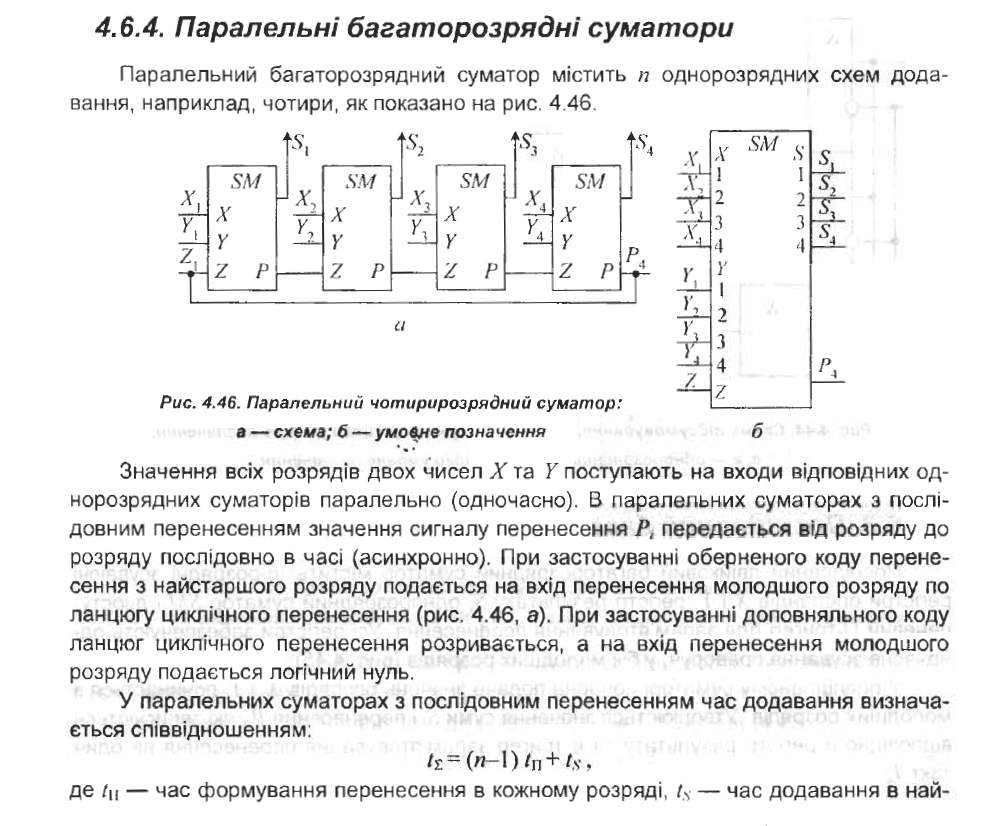

- •37. Багато розрядний суматор паралельної дії

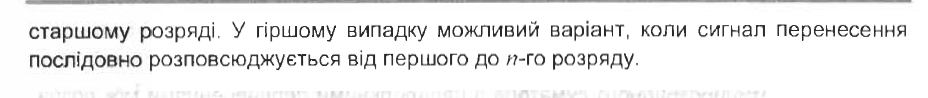

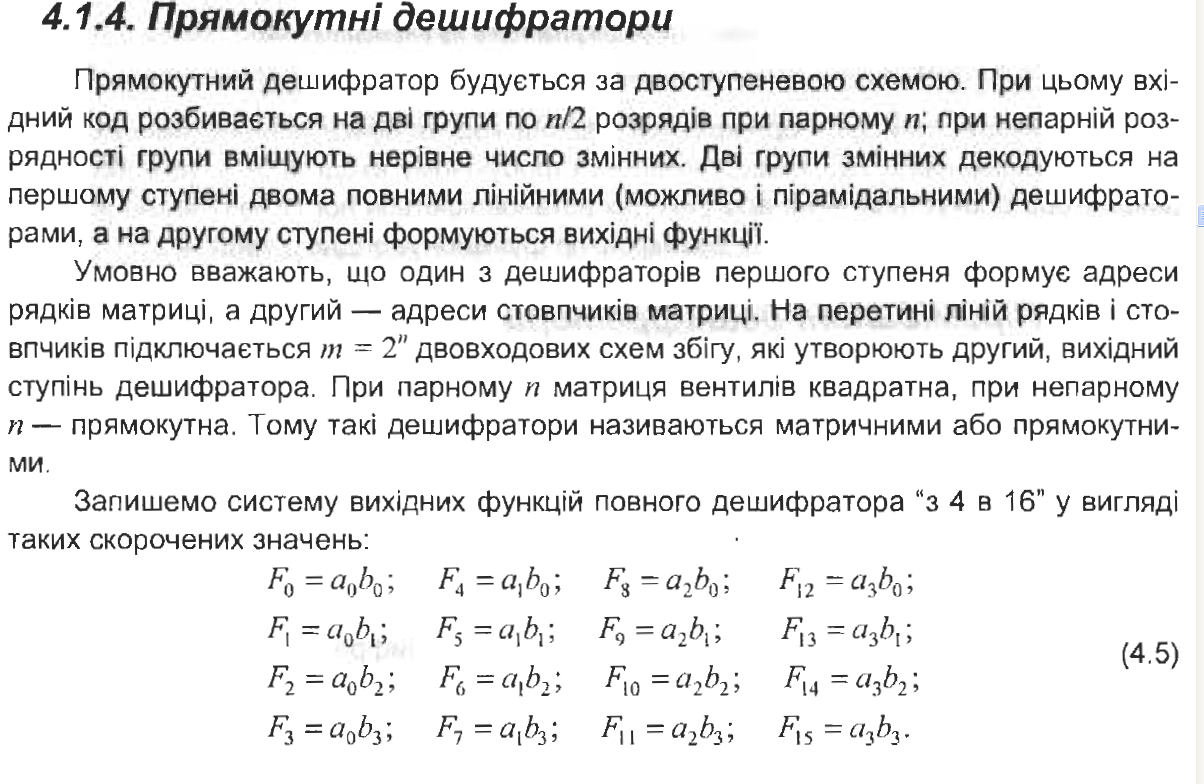

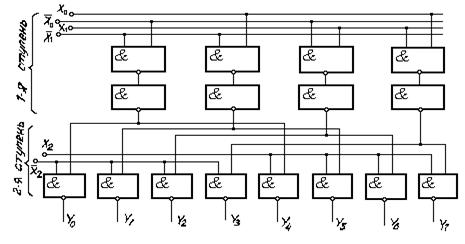

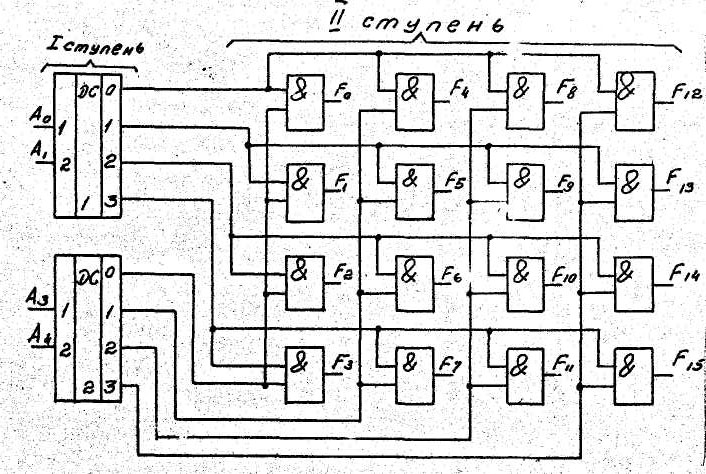

- •38. Прямокутний дешифратор

36. Послідовний багаторозрядний суматор

Послідовний двійковий багаторозрядний суматор містить: n-розрядні зсуваючі регістри операндів X і Y, регістр результату S, однорозрядний суматор SM і двоступеневий D-тригер для запам’ятовування перенесення. Усі регістри забезпечують одночасне зсування праворуч, у бік молодших розрядів.

Схема

послідовного багаторозрядного суматора

Схема

послідовного багаторозрядного суматора

У послідовному суматорі попарна подача значень розрядів Xi і Yi починається з молодших розрядів. Утворюються значення суми Si і перенесення Pi, які записуються відповідно в регістр результату та в тригер запам’ятовування перенесення на один такт Тс. Послідовне додавання виконується за стільки тактів, скільки розрядів у числі. Тому час додавання tS визначається співвідношенням: tS = nTс, де Тс – тривалість машинного такту. Від’ємні числа рекомендується представляти в доповняльному коді. Послідовний суматор потребує мінімальних апаратних витрат, однак тривалість операції додавання пропорційна розрядності операндів. Тому послідовний суматор можна використовувати у відносно повільнодіючих цифрових пристроях.

37. Багато розрядний суматор паралельної дії

38. Прямокутний дешифратор

Пірамідальний дешифратор поступається каскадному в економічності за кількістю використовуваних діодів і відрізняється тим, що в його каскадах кожна конституента одиниці формується як кон'юнкція однієї з конституент попереднього каскаду і одного з розрядів вхідного слова, яке ще не використовувався для формування конституент. Пірамідальні дешифратори, так само як прямокутні, відносяться до розряду багатоступеневих дешифраторов, особливістю яких є застосування у всіх ступеннях дешифрування двовходових вентилів з обов'язковим підключенням виходу елемента першої сходинки до входів тільки двох елементів И першої ступені. Пірамідальні дешифратори відрізняються від лінійних лише використанням тільки двовходових кон’юнктерів незалежно від розрядності дешифрируємого числа, а коефіцієнт розгалуження тригерів вхідного регістра і всіх логічних елементів дешифратора також дорівнює двом. Таким чином, пірамідальні дешифратори вільні від обмежень, які властиві лінійним дешифраторам, але в них використовується більша кількість логічних елементів. Пірамідальні дешифратори в даний час практично не застосовуються, оскільки розраховані на використання двовходових елементів і мають внаслідок цього громіздку структуру і низьку швидкодію. Пірамідальний дешифратор складається з декількох рівнів послідовного дешифрування, при цьому на кожному ступені дешифрируєтся частина коду вхідного слова. Пірамідальні дешифратори вільні від обмежень, властивих лінійним дешифраторам, але в них використовується більша кількість логічних елементів.

Пірамідальні дешифратори на n входів мають x=n-1 ступенів, причому на кожному ступені використовуються тільки двовходові схеми И. Кількість елементів И в i-й ступеня складає 2i+1, де i - номер ступені. Загальна кількість схем И для пірамідального дешифратора визначається за формулою:

![]()

Схема пірамідального дешифратора

Двоступінчастий дешифратор(ступеневий) складається з двох ступенів, в яких кожна конституента формується як коньюнкція відповідного набору часткових конституент. Багатоступінчасті дешифратори найбільш економічні серед можливих типів дешифраторів.Ступінчасті (матричні) дешифратори будуються на базі декількох дешифраторів. Нехай необхідно побудувати ступінчастий дешифратор з n входами на базі двох лінійних дешифраторов. При цьому, якщо кількість входів ступеневої дешифратора n парне число, то кожен лінійний дешифратор має n / 2 входів. Якщо кількість входів є непарних числом, то один лінійний дешифратор має (n - 1) / 2 входів, а другий (n + 1) / 2 входів.

Схема електрична – функціональна двоступеневого дешифратора